Verdi是一个功能强大的debug工具,可以配合不同的仿真软件进行debug,很多企业常用的就是VCS+Verdi或或者Xcelium(xrun)+Verdi的方式进行代码的仿真与检查,Verdi使用情形主要是IC验证工程师(Debug),IC设计工程师(Review)。总之,Verdi很重要,作为一名ICer要是不会用Verdi,确实说不过去。

一、Verdi环境配置

(一)公司 - 一般拿来直接用

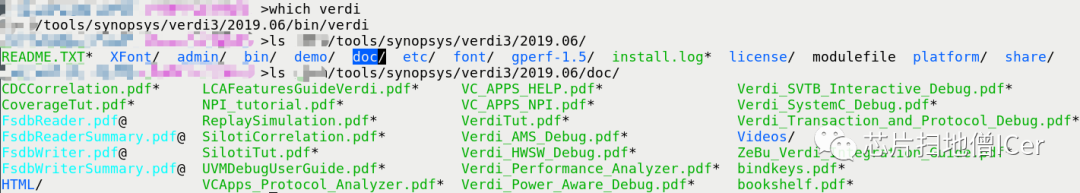

1. 在芯片设计公司中,九成公司应该都配备了Verdi,一般都会放在公司服务器目录的Tools目录下,我们可以通过which命令查看任何公司购买的EDA Tools所在路径,查看各种版本/对应文档/配置等:

2. 有些时候,我们需要切换Verdi版本,来满足不同项目或其他需求,在.cshrc中配置 或 直接module load 对应Verdi版本,最后module list查看是否load成功。

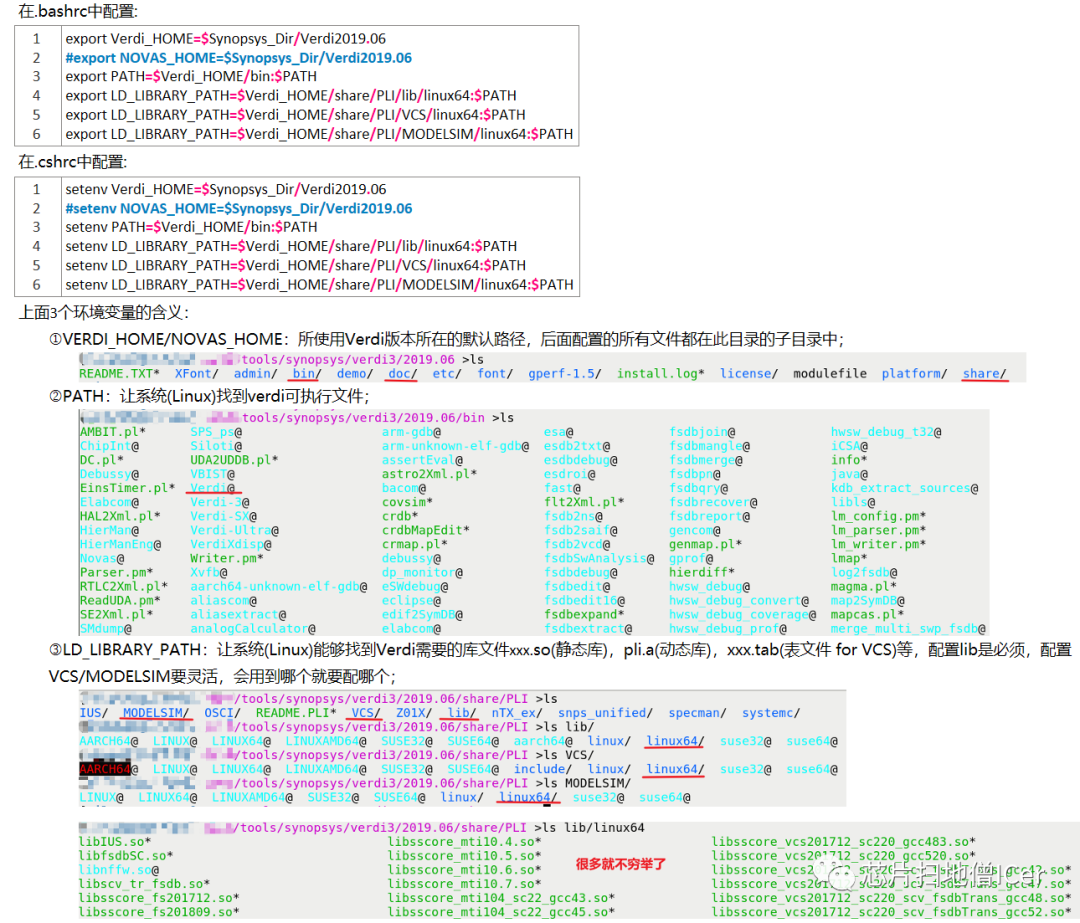

(二)其他 - 需自己摸索配置再用 (考虑排版+代码风格,直接上图)

二、配置波形文件“三方法”“八奇技”

FSDB(FastSignal Database)是Verdi支持的文件格式,用于保存仿真产生的信号波形。 据Verdi文档说明,FSDB比标准的VCD格式节省磁盘空间,处理速度更快。

(一)常用“三方法”:

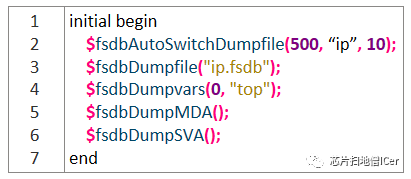

1. (最常用) 一般是在testbench(验证环境,简称tb)中的top.sv文件里,创建个initial块结合$fsdbDumpxxx()命令来配置:

提醒:使用这种方法,vcs编译前需要添加-debug_access选项。

2. (不常用) VCS添加编译选项"+vcs+fsdbon":

这样指定仿真过程生成.fsdb格式的波形,默认则保存成名为novas.fsdb的波形文件;

注

意的是,仿真过程会将整个design给dump下来,同时会自动添加 -debug_access 选项。

另外,配置过程中若出错,首先检查一下LD_LIBRARY_PATH是否配置对,目录下有没有Verdi需要的库文件xxx.so(静态库),pli.a(动态库),xxx.tab(表文件 for VCS)等,一般都是这里没配对导致没生成波形而报错;

提醒:vcs+fsdbon和tb中用$fsdbdumpvar()选一种方式即可;

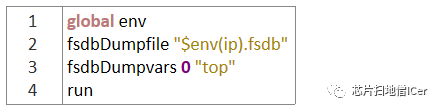

3. (不常用) 使用UCLI命令: UCLI:Unified Command Line Interface

UCLI其实就是vcs的命令交互模式,需要在编译时加入参数 (-ucli) 以开启ucli,否则ucli交互时只能使用简单的'run'、'dump'、'quit'命令。

启动方式例如:./simv -ucli

该方法与方法1基本一样,均是使用fsdbDumpvars/fsdbDumpfile等命令,不同之处在于使用的方式和便捷程度,与方法1相比,该方法可以在不重新编译的情况下,通过修改.ucli.cmd文件中的命令,来指定需要dump波形的模块和层级,从而节省编译带来的资源消耗。

得注意的是,使用fsdbDumpvars/fsdbDumpfile等命令时,不需要像方法1使用时,前方使用符号: $。

执行仿真的过程中,通过./simv -ucli -i.ucli.cmd方式给入,.ucli.cmd(名字随便取,但格式不能变)中存放命令举例如下:

提醒:使用这种方法,vcs编译前需要添加-debug_access选项。

(二)常用命令“八奇技”(结合例子看容易理解):

1. $fsdbDumpon - 打开 FSDB dumping;

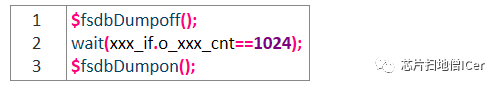

2. $fsdbDumpoff - 关闭 FSDB dumping; 上述两个命令,一般搭配wait()函数使用,更加灵活,eg:

表示之前未dump波形,直到等到o_xxx_cnt==1024时,才开始dump波形;

3. $fsdbDumpfile("fsdb_name", limit_size) - 指定dump文件;

| fsdb_name | - 表示指定的fsdb文件名,如"ip.fsdb" |

| limit_size | - 表示dump波形的最大size(多少MB)- 可不配置 |

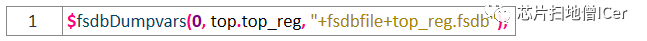

4. $fsdbDumpvars(depth,instance, "option=") - dump指定模块的信号; 这个命令可以多次使用,但一般不使用多次,使用多次目的是:想用来dump不同instance的波形,想达到相同目的其实有更加灵活的方法 ——“建立dump_scope.list + $fsdbDumpvarsToFile()” (后面会介绍);

| depth | - 0 表示dump instance以下所有层级的信号(常用) - 1 表示只dump instance这一层的信号 |

| instance | -指定dump的hierarchy,如 dut.top.xxx |

| option | - dump时可以选择的一些选项:- 可不配置 |

| "+mda" | - 表示dump memory或者MDA(多维数据)的数据; |

| "+packedmda" | - 表示dump 压缩的memory数据; |

| "+functions" | - 表示dump function和task里的信号; |

| "+all" | -表示dump all; |

| "+Reg_Only" | - 表示只dump reg类型的数据; |

| "+strength" | - 表示开启强力dump开关; |

| "+struct" | - 表示dump struct数据(默认开); |

| "+power" | - 表示dump power相关信号的数据(默认开); |

| "+fsdbfile" |

- 表示直接dump指定的hierarchy的fsdb文件名字,eg:  |

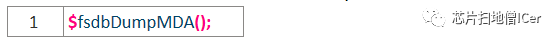

5. $fsdbDumpMDA(depth, instance,"options") - dump指定模块中的多维数组,内部参数含义同上; eg_1:如果想更方便,可直接什么参数都不配,即默认都dump

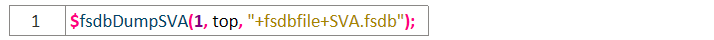

6. $fsdbDumpSVA(depth, instance, "option") - dump指定模块中的assertion,内部参数含义同上; eg_1:将该instance (top)下所有assert全部dump到SVA.fsdb中

eg_2:如果想更方便,可直接什么参数都不配,即默认都dump

7.$fsdbAutoSwitchDumpfile(file_size,"fsdb_name",number_of_files,"log_file_name", "+fsdb+no_overwrite") - 波形过大/资源紧张情况,灵活使用拆分Dump波形很有用

| file_size | 波形文件大小限制,单位为MB,最小为10M,若值小于10MB则默认10MB; |

| "fsdb_name" | 波形文件的名字,在实际加载波形时,文件名为fsdb_name_000.fsdb, fsdb_name_001.fsdb …; |

| number_of_files | 最多可以加载多少个fsdb_size这么大的波形文件,如果写为0,则默认没有限制; |

| "log_file_name" | 指定log文件的名字,log文件中会记录每段波形的起始和中止时间; - 可不配置 |

| "+fsdb+no_overwrite" | 当number_of_files限制的个数达到时停止dump波形,反之,一旦超出限制,会从头dump,这样会一定程度上覆盖掉起初的波形文件;- 可不配置 |

eg_1:单个波形文件为500MB,最大可以加载10个这么大的文件,每段波形的起始和中止时间记录在fsdb.log中,并具备防overwrite的限制;

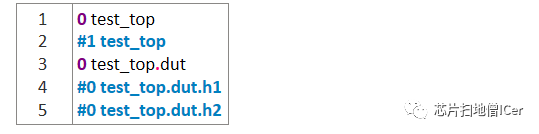

8. $fsdbDumpvarsToFile("./dump_scope.list"); - 将需要dump的hierarchy以及depth放到一个文件里吃进来,波形过大/资源紧张情况,灵活使用选取必要波形Debug; ./ - 表示当前路径,也就是dump_scope.list要与top.sv在同一路径,当然也可以灵活改变路径; eg_1:dump_scope.list (0/1代表深度,用法通上述函数一致;#用于注释)

审核编辑:刘清

-

IC设计

+关注

关注

38文章

1405浏览量

108418 -

EDA工具

+关注

关注

5文章

276浏览量

34130 -

VCS

+关注

关注

0文章

80浏览量

10339

原文标题:Verdi环境配置、生成波形的“三方法”和“八奇技”

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

利用Verdi调试协处理器的实现步骤

想调用VCS+VERDI测试蜂鸟,按照网上的弄了,但是没有波形,为什么?

请教VCS和verdi怎么联合使用

VCS仿真卡住,为什么无法生成verdi波形文件呢?

怎么修改verdi软件波形背景颜色?

Verdi使用技巧 连续有效信号量测方法

vcs和verdi的调试及联合仿真案例

如何通过自动化脚本实现Questasim和Verdi的联合仿真

Verdi环境配置、生成波形的方法

Verdi环境配置、生成波形的方法

评论