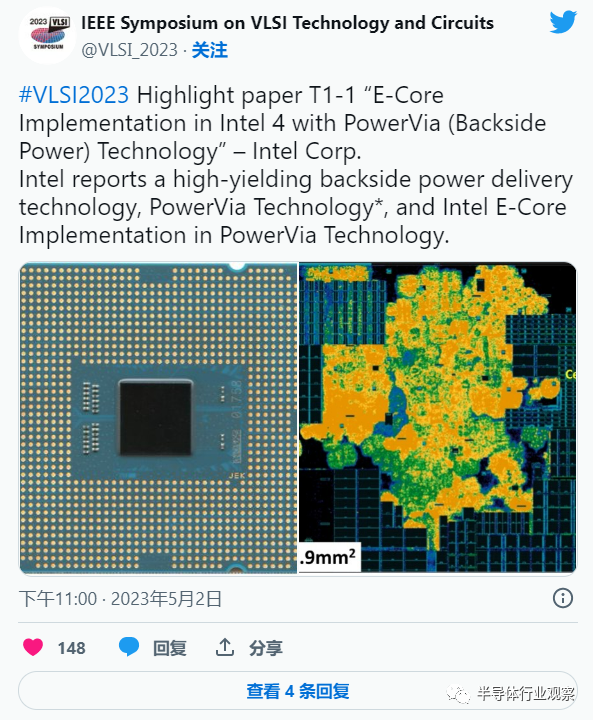

英特尔很快将在“Intel 4”E-Core 芯片中展示其称为 PowerVia 的下一代背面供电技术。

英特尔的背面供电实验芯片基于未命名的节能“E 核”,并在Intel4工艺技术上实现。英特尔将在 2023 年 VLSI 技术和电路研讨会上公布的调查结果表明,英特尔的 PowerVia 在核心的大部分区域实现了超过 90% 的标准单元利用率,同时还提供了超过 5% 的时钟速度提升,因为减少了红外压降。英特尔准备展示的一张图片似乎证明了这一点,尽管无法评估类似内核在实际工作负载中的表现。

英特尔 PowerVia 演示即将推出:利用芯片背面的独立模块实现功率传输。

VLSI已在推特上发布了英特尔 PowerVia 实施的第一眼,并将在 6 月开始的 2023 年 VLSI 研讨会期间进行演示。在推文中,VLSI 展示了英特尔在芯片背面实施 PowerVia 的情况,该芯片被提及使用“Intel 4”工艺节点并搭载全 E-Core 实施。

Intel 4 芯片看起来像是基于旧的 LGA1151/LGA1200 设计,因为它的形状是方形的,并且在封装下方有一个辅助裸片。这是您通常会看到大量小型晶体管的区域,但其中大部分已被 PowerVia 技术取代。考虑到 E-Core 实施基于“Intel 4”,它很可能基于即将推出的为 Meteor Lake 的 E-Core 提供动力的 Crestmont 架构。

此外,电池利用率显示,在芯片内 2.9mm2 的面积内,Intel PowerVia 技术的利用率可高达 90%。此外,这不仅提高了利用率,而且还导致时钟速度略有提高,IR 压降减少,在同一芯片上实现了高 5% 的时钟。

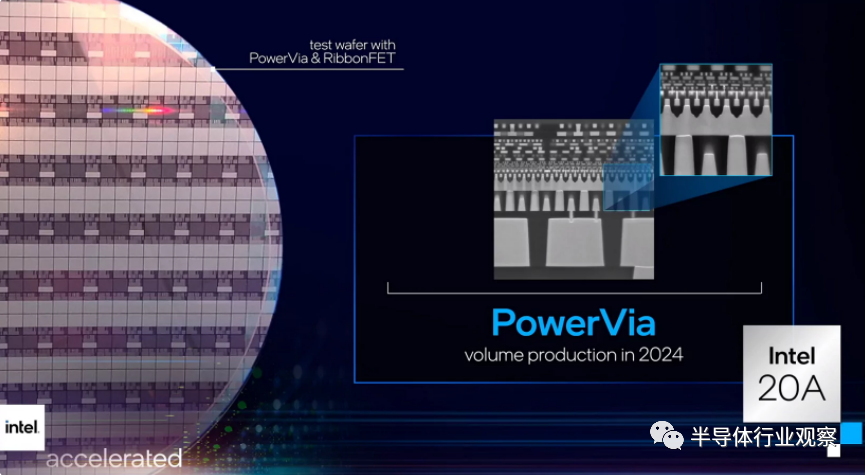

更有趣的是,VLSI 表示这是一种高产设计,但至少要到 Arrow Lake 或 Lunar Lake 世代才会出现。原因是20A和18A工艺节点的消费级芯片将采用PowerVia和RibbonFET 。据说第一批 PowerVia 芯片将于 2024 年投入量产。

从早些时候,我们知道 PowerVia 是一种功率传输工艺,它在背面工作,以解决硅架构中互连中的瓶颈问题。这是 PowerVia 推出后应该解决的常见问题。Power Via 不是将数据通信信号和电源互连传输到晶体管层的顶部,而是直接传输到硅晶圆的背面,同时在晶圆顶部传输信号。

我们迫不及待地想看看 PowerVia 做了什么,并在接下来的几个月里看到它的实际应用,因为它听起来绝对是一种可以改变电力传输格局的技术。

背面供电是大势所趋

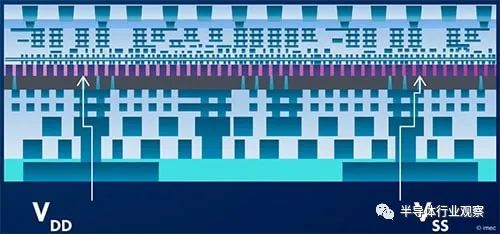

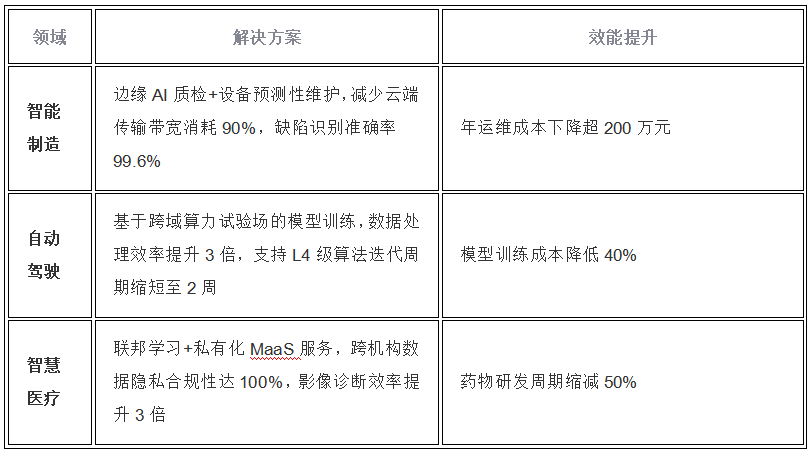

据此前报道,芯片供电网络(Power Delivery Network, PDN)的设计目标是以最高效率为芯片上的主动元件提供所需的电源(VDD)与参考电压(VSS)。一直以来,业界都是利用后段制程(BEOL),在晶圆正面布线,透过这些低电阻的导线来供应电力给芯片(图1)。但也因为如此,芯片内的供电网络与信号网络(即芯片内的信号线)必须共用相同的元件空间。

图1.传统的芯片正面供电网络

但随着制程节点往前推进,把电源网络实作在芯片正面,遇到越来越多挑战,使得业界开始探索把供电网络转移到背面的可能性,从而让晶背供电(Backside PDN)成为热门的技术议题。本文将先从传统PDN所遇到的挑战谈起,进一步探讨晶背供电技术的优势,以及这项技术未来的发展重点。

传统PDN布线面临诸多挑战

为了将电力从封装传输至芯片中的电晶体,电子必须经由金属导线和通孔,穿越15~20层BEOL堆叠。然而,越接近电晶体,线宽和通孔就越窄,电阻值也因而上升,这使得电子在向下传输的过程中,会出现IR压降现象,导致电力损失产生。

除了电力损失之外,PDN占用的空间也是一个问题。当电子快到达电晶体,例如抵达标准元件层时,电子会进入由BEOL制程所制造Mint金属层,进而分配给负责提供工作电压与接地电压的电源轨。然后,这些电源轨会透过互连网络,连接到每一个电晶体的源极与汲极,完成供电任务。但这些电源轨会占用元件周围及标准单元(Standard Cell)之间的空间。

然而,随着制程技术世代交替,传统后段制程的元件架构难以跟上电晶体的微缩速度。如今,芯片内部的电源线路,在布线复杂的后段制程上,往往占据了至少20%的绕线资源,如何解决信号网络跟供电网络之间的资源排挤问题,变成芯片设计者所面临的主要挑战之一。此外,电源线和接地线在标准单元设计上占了很大空间,使得元件很难进一步微缩。就系统设计而言,因为功率密度和IR压降急剧增加,从稳压器到电晶体的功率损失就很难控制在10%以下,带给工程师严峻挑战。

晶背供电网络具有雄厚潜力

把芯片内的PDN从正面移到背面,也就是所谓的晶背PDN(图2),可以解决上述问题。若能将供电网络与信号网络分离,把电源线路全部移至晶圆背面,就能对标准单元进行直接供电,不仅导线更宽、电阻更低,而且电子还不需层层穿越后段制程的元件堆叠。如以一来,不仅缓解了IR压降问题,让PDN的效能获得改善,同时也避免了后段制程的布线壅塞问题。如果设计得当,晶背PDN甚至还能进一步减少标准单元的高度。

图2 把供电网络从正面转移到背面,让供电网络跟信号网络分离,可带来诸多效益

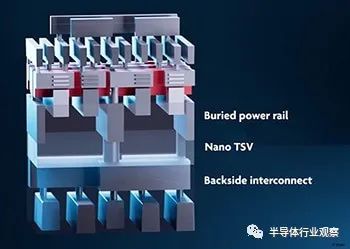

要把PDN从芯片正面转移到背面,需要两项关键技术,分别是埋入式电源轨(BPR)与纳米硅穿孔(nTSV),其结构示意如图3。

图3 晶背供电网络结构的示意图,最顶端的Nanosheet电晶体藉由埋入式电源轨跟纳米硅穿孔,连接到位于芯片背部的互联线路

埋入式电源轨是一种微缩化技术,可以进一步降低标准单元的高度,并减缓IR压降问题。这些电源轨是埋在电晶体下方的导线,一部份藏在硅基板内,另一部份则在浅沟槽隔离氧化层内。它们取代了传统后段制程在标准单元布下的电源线与接地线。

将供电网络的实作从后段制程移到前段制程,是划时代之举。这种作法能有效减少Mint层的元件堆叠数量,进而微缩标准单元尺寸。还有一点,如果电源轨设计在标准单元的垂直向,还能放宽导线,进而减缓IR压降。

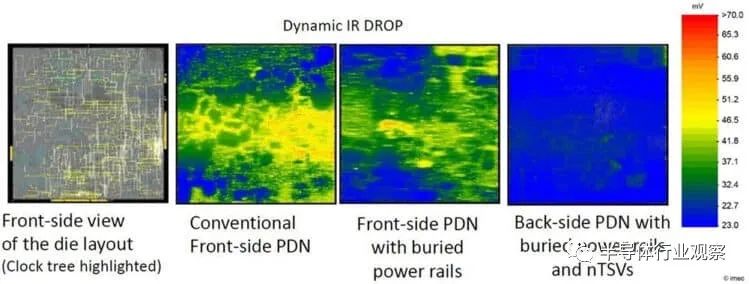

在2019年的IEEE国际电子研究会议(IEDM)上,imec携手硅智财公司Arm,预测晶背供电技术所能带来的效能升级。Arm在其开发与采用先进设计规则的中央处理器(CPU)上进行模拟,并比较「传统供电」、「晶圆正面供电结合埋入式电源轨」、「晶背供电搭配纳米硅穿孔与埋入式电源轨」这三种供电网络实作方法的优劣。

模拟结果显示,就供电效率来看,第三种明显胜过其它实作方法。芯片上的动态IR压降热力图(图4)显示,与传统的正面供电网络相比,导入埋入式电源轨后,IR压降最多可以减至1.7倍。但埋入式电轨结合晶背供电网络的性能表现更佳,电压损耗大幅下降7倍。

图4 三种不同供电方法的动态IR压降模拟热力图

晶背PDN制程解析

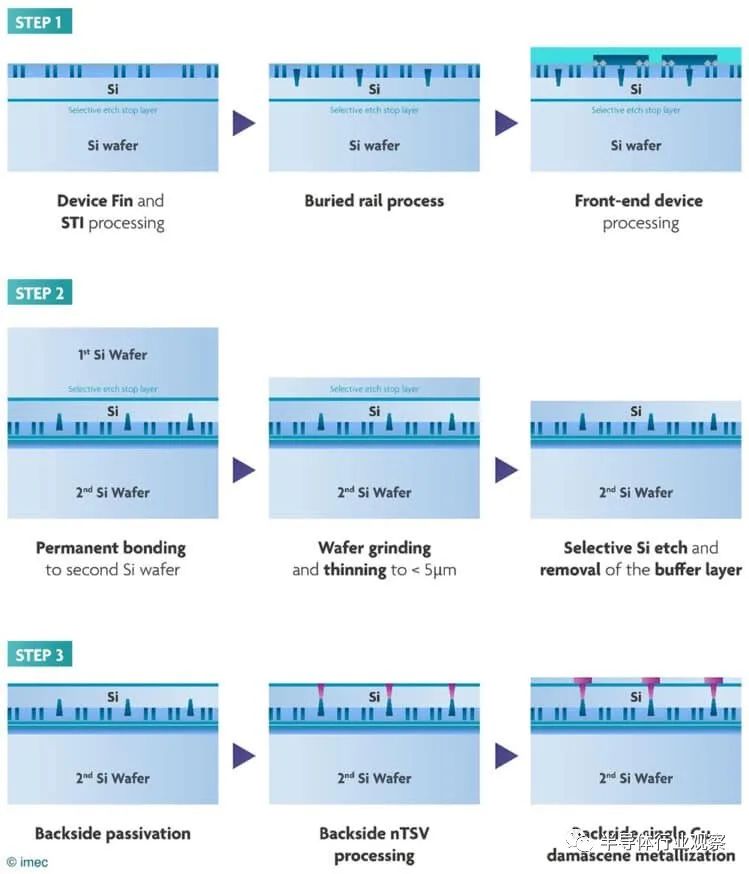

接下来,我们会说明晶背供电网络的其中一项应用案例:纳米硅穿孔在超薄膜晶圆的背面进行制造,并与埋入式电源轨连接。我们以在晶圆正面制造的FinFET为例,这些元件透过埋入式电源轨与纳米硅穿孔,连接到晶圆背面。其制程步骤如图5。

图5 晶背供电网络制程包含与纳米硅穿孔相连的埋入式电源轨。为了方便说明,步骤2和步骤3的部分细节与步骤1雷同,故省略,包含连接埋入式电源轨与元件

步骤1:在晶圆正面制程导入埋入式电轨

首先,在12吋硅晶圆上成长一层硅锗(SiGe)层。这层硅锗材料在接下来进行晶圆研磨(步骤2)时可以当作蚀刻停止层。接下来,在硅锗层上方成长一层薄膜硅覆盖层,这时才算开始制造元件与埋入式电源轨。埋入式电源轨在进行浅沟槽隔离后才确定图形。这些沟槽在硅覆盖层内蚀刻成形,并以氧化物(衬垫层)与金属材料(例如钨或钌)填充。通常,这些电源轨的最大线宽为30nm,最大间距为100nm。接着在金属材料挖洞,并覆盖一层介电材料。元件(本文指的是FinFET)的制造是在布下埋入式电源轨之后,而这些电源轨透过连接到BPR的通孔(via-to-BPR, VBPR)与M0A层的导线,与电晶体的源极和汲极连接。最后进行铜金属化。

步骤2:晶圆接合与研磨

载有元件与埋入式电源轨的晶圆接着翻到另一面,让用来制造主动元件的晶圆正面与未图形化的载板接合。先在室温下采用SiCN熔接制程(Fusion Bonding),然后在250℃下进行退火,第一片晶圆的背面就能研磨到硅锗层,也就是蚀刻停止层。晶圆研磨步骤结合了化学机械研磨(CMP)与湿式、干式蚀刻技术,依序进行晶背薄化处理。接着,移除硅锗层,晶圆处理就绪,准备进入纳米硅穿孔制程。

步骤3:制造纳米硅穿孔并连接到埋入式电源轨

先在晶背长出一层钝化层,随后采用一种能从晶背穿透硅材进行对准的微影制程,进行纳米硅穿孔的图形化。这里所用的蚀刻技术可以穿透硅材(深度达到数百纳米)来制造纳米硅穿孔,这些通孔最后落在埋入式电源轨上,并以氧化物与金属钨填充。

在这个特殊案例中,纳米硅穿孔的间距为200nm,完全没占用到标准单元的空间。最终是制造单层或多层的金属层,这些位于晶背的元件层会透过纳米硅穿孔,与晶圆正面的埋入式电源轨实现通电。

锁定三大关键步骤进一步改良

导入晶背供电网络意味着增加制程步骤。这几年来,imec展示了不少关键技术,逐步处理这些新增制程步骤所带来的挑战。

为埋入式电源轨引进新金属材料

就先前提议的制程,埋入式电源轨会在制成元件前,于前段制程制造。也就是说,这些金属导线必须在后续进行元件制造的步骤时承受高温。对芯片制造商来说,这就跟数十年前在后段制程导入铜材料一样,极具颠覆性。

因此,埋入式电源轨的材料选择至关重要。imec可以整合以不同耐火金属制成的埋入式电源轨,包含钌(Ru)和钨(W)等高度耐热的金属元素。为了避免前段制程的材料受到污染,imec研究团队还额外增加了覆盖层来包覆这些金属导线。

imec相信,就性能升级与微缩化而言,结合埋入式电源轨与纳米硅穿孔的发展潜力十分可观。晶背供电网络还有其它做法,但是有的会牺牲供电效能、标准单元面积,或是增加前段制程的复杂度。

提高晶圆研磨精准度

为了将纳米硅穿孔连接至后续制造的铜导线,并降低其电阻,进而减缓IR压降,我们必须更精准地控制晶圆薄化的厚度,研磨至数百纳米。这就限制了晶圆厚度的容许差异,但在进行不同道研磨步骤时就可能出现变异性。imec携手合作伙伴,致力于改良蚀刻制程的化学溶液。例如,最后一道湿式蚀刻能够展现高度选择性,干净去除硅锗层。在晶圆研磨的最后一步,硅锗层被移除,这时需要一种对硅材具备高度选择性的专用化学物质。这样才能确保硅覆盖层能够平滑露出,厚度差异小于40nm。

不过,在硅基板高度薄化的情况下,元件本身的温度变化所造成的热冲击(Thermal Impact)会变得更加明显。这是需要审慎评估的一点。初步模拟结果显示,晶背的导线可协助从横向散逸热能,因此对整体散热效果能带来许多助益,从而缓解了热冲击的疑虑。其它与散热有关的模拟工作仍在进行,以获取更多这方面的资讯。

提高晶圆接合对位精度

晶圆接合步骤会让主动式元件所在的第一层晶圆产生形变,进而在微影方面带来技术挑战。因为要在晶圆研磨后,从晶背进行纳米硅穿孔的图形化,故微影技术需要更高精确度,才能让纳米硅穿孔与下层的埋入式电源轨对准。因为这些元件特征都算是标准单元设计,对准精度应该优于10nm。但是传统的微影对准技术不足以准确校正晶圆接合的形变。

值得庆幸的是,晶圆接合技术已有多项进展,对准误差和失真都已大幅下降。此外,透过先进的微影校正技术,纳米硅穿孔对准埋入式电源轨的误差可以降至10nm以下。

新增制程不影响元件电性

在前段制程添加埋入式电源轨、晶圆研磨跟纳米硅穿孔这些新步骤,会影响前段制程所制造出的元件的电性吗?这点想必是很多半导体制程工程师都会有的疑问。

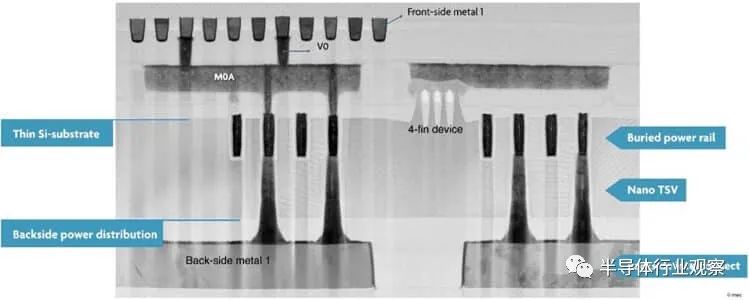

为了找出解答,imec近期开发了测试元件,采用上述制程与经过改良的做法。该元件是微型FinFET(图6),利用精确的对准能力,将纳米硅穿孔从晶背连接至320nm深的埋入式电源轨。电源轨透过MOA层与VO通孔连接到晶圆正面的导线。借此,研究人员就能比较测试元件在进行后段制程前后的电性差异。结果显示,只要在制程最后进行退火,就能取得FinFET的最佳性能,不受埋入式电源轨与后段制程影响。

图6 微型FinFET测试元件的穿透式电子显微镜(TEM)图,可见其与晶圆正面和背面相连

先进逻辑与3D SoC率先获益

有些芯片厂商已经宣布将在2nm及未来技术节点的逻辑芯片制程,也就是Nanosheet电晶体世代导入晶背供电技术。不过,这项新兴的布线技术其实可以应用在更广泛的电晶体架构上。imec认为,未来业界将发展出具备6T的Nanosheet电晶体,若结合埋入式电源轨设计,标准单元高度可望降至6T以下。

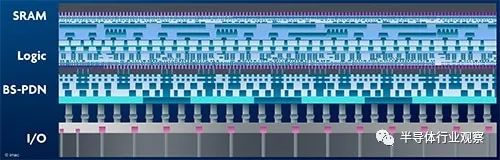

其实,晶背供电技术的应用不仅限于2D芯片,未来还有可能用来提升3D系统单芯片(SoC)的性能。想像未来的3D SoC能将部分甚至所有的记忆体元件移到芯片上层,逻辑元件则在下层,如图7。

图7 导入晶背供电网络的3D SoC示意图

技术上,这是可以透过晶圆接合技术实现的。把逻辑元件与记忆体分别置于不同晶圆的正面,再将两片晶圆正面接合。这时,两片晶圆的背面变成3D SoC的外侧。接着就是思考如何善用逻辑元件那片晶圆的背面,才能把电源连接到核心逻辑电路。其实,透过2D SoC技术就能做到这点,但主要差别是前面提到的载板晶圆,本来是为了晶圆研磨而设计,但现在则是以记忆体那片晶圆来取代。

虽然目前还未进入实验,初步评估这套做法在IR压降方面的发展可期。透过先进制程研究用的设计流程套件(PDK),上述解决方案在逻辑与记忆体堆叠(Memory-on-logic)的芯片分区设计上进行验证。结果显示,结合晶背供电网络、纳米硅穿孔与埋入式电源轨的元件性能颇富前景:与传统从晶圆正面供电的做法相比,底层元件的平均IR压降减少81%,峰值减少77%。因此,晶背供电技术特别适合用于先进CMOS的3D IC设计。

不论是2D或3D芯片设计,晶背空间还能有其它的延伸应用,像是增设I/O或静电保护(ESD)等元件。举例来说,imec结合了晶背供电技术与2.5D元件:一颗柱状且由金属—绝缘体—金属(MIM)组成的去耦电容。该元件将电容密度提升了4~5倍,利于进一步控制IR压降。这些研究成果皆源自经过实验数据校正的IR压降模型。

晶背供电带来诸多优势发展潜力值得期待

新一代芯片很可能打破传统,从晶圆背面供电。晶背供电网络的设计包含在晶圆背面制造金属导线、埋入式电源轨与纳米硅穿孔,具备多项发展优势,不仅能减少IR压降、纾解后段制程的布线压力,还能帮助微缩标准单元。关键的制程技术包含整合埋入式电源轨、晶圆接合、晶圆研磨与纳米硅穿孔制程,全都在进行研发改良,为将来应用在先进逻辑元件与3D SOC做准备。

审核编辑 :李倩

-

芯片

+关注

关注

463文章

54412浏览量

469173 -

电阻

+关注

关注

88文章

5812浏览量

179926 -

英特尔

+关注

关注

61文章

10320浏览量

181066

原文标题:芯片巨头,发力背面供电

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

航裕电源以技术创新破解火箭地面测发控系统供电难题

AI服务器机架供电架构解析:PSU、BBU 与 CBU 的设计逻辑及关键芯片方案

中国算力芯片的拐点时刻

2026年中国科技发力,瑞之辰压力传感器助力产业升级

0.2nm工艺节点的背后需要“背面供电”支撑

赋能电源芯片国产替代,智芯谷助力AI算力稳定前行

智能驾驶域控制器:车规电容如何赋能高算力车载场景?

船用轴发供电不稳,CSD船用变压器能救场吗?

芯片巨头,发力背面供电

芯片巨头,发力背面供电

评论