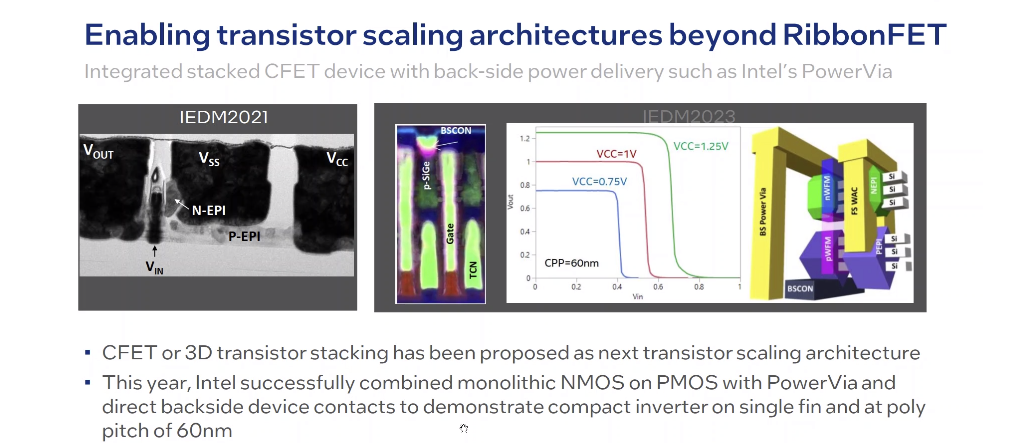

英特尔在2023年国际电子设备制造大会上宣布,他们已经成功完成了一项名为PowerVia的背面供电技术的开发。这个技术是基于英特尔的最新晶体管研究成果,它实现了互补金属氧化物半导体场效应晶体管(CFET)的60纳米栅极间距垂直堆叠。通过堆叠晶体管,该技术提高了面积效率和性能,同时还结合了背面供电和直接背面接触这两种技术。

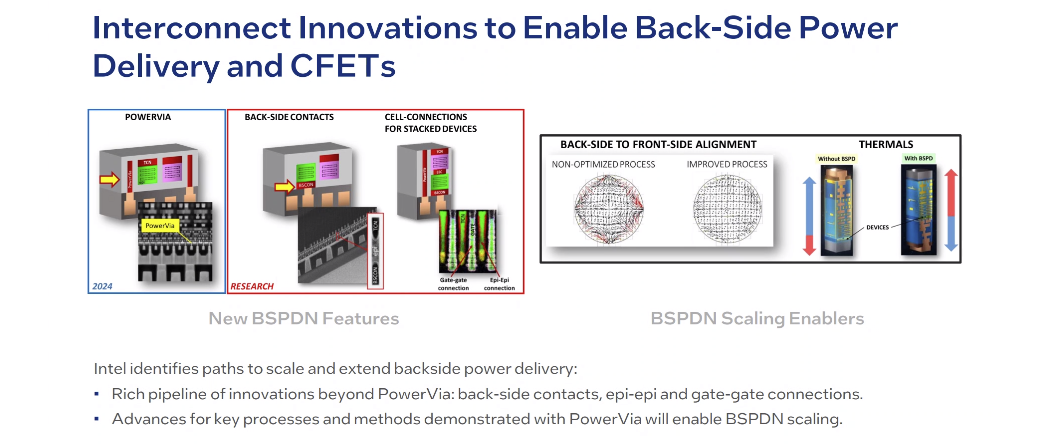

英特尔解释说,过去几年芯片制造都是层层叠加的,从最小的元件-晶体管开始制造,之后需要创建更小的线路层,用于连接晶体管和金属层。这些线路被称为信号互连线,其中还包括用于给晶体管供电的电源线等。但是随着晶体管逐渐变小、密度日益提高,互连线和电源线共享的线路层变得越来越混乱。面对这个问题,英特尔开始寻找将电源线迁移到芯片背面的背面供电技术。

英特尔的背面供电解决方案PowerVia已经产生了具有竞争力的测试结果。这项技术解决了传统"披萨式"制造方法带来的问题,尤其是电源线和互连线的分离以及线径的扩大,从而改进了供电和信号的传输。

对于英特尔的晶体管堆叠和背面供电的技术,研究表明,它将在微缩晶体管的密度上发挥重要作用。英特尔强调,这将超越其"四年五个制程节点计划",以背面供电技术继续微缩晶体管。

目前,英特尔的这项技术在竞争对手中具有一定的优势。比如台积电将在2025年量产的第一代2纳米制程时引入全环绕栅极(GAA)架构,然后在2026年的第二代2纳米制程中引入背面供电技术。与此同时,尽管韩国三星在2022年量产的3纳米制程技术上已经引入了GAA架构,但是他们预计要到2025年量产的2纳米制程才会引入背面供电技术。从这个角度来看,英特尔确实领先了一步。

-

芯片

+关注

关注

462文章

53539浏览量

459162 -

英特尔

+关注

关注

61文章

10275浏览量

179315 -

晶体管

+关注

关注

78文章

10257浏览量

146291 -

三星

+关注

关注

1文章

1737浏览量

33692

发布评论请先 登录

吉方工控亮相2025英特尔技术创新与产业生态大会

18A工艺大单!英特尔将代工微软AI芯片Maia 2

英特尔宣布工程技术领导层重要任命,加速CEO陈立武转型布局

新思科技与英特尔在EDA和IP领域展开深度合作

英特尔发布全新GPU,AI和工作站迎来新选择

英特尔持续推进核心制程和先进封装技术创新,分享最新进展

英特尔代工:明确重点广合作,服务客户铸信任

英特尔宣布完成PowerVia背面供电技术的开发

英特尔宣布完成PowerVia背面供电技术的开发

评论