GaAs基VCSEL已广泛应用于三维成像、无人驾驶、物联网、数据通讯等领域,同时在光电对抗、激光雷达、航空航天等高精尖领域也发挥着巨大的作用和潜能。GaAs基VCSEL的刻蚀技术是制备过程中最关键的环节。刻蚀时掩膜的质量、刻蚀GaAs后的表面质量、VCSEL的台面和侧壁形貌都会直接影响器件性能。在刻蚀过程中,掩膜的好坏直接影响刻蚀的效果。

VCSEL侧壁如果过于粗糙,就会影响载流子的复合效率,也会使光发生散射效应。VCSEL表面和侧壁不光滑、有残留时会增大其电阻值或击穿电流。如果GaAs/AIGaAs的刻蚀速率未能达到1:1,那么台面的侧壁会出现横向钻蚀的镂空现象,不利于实现均匀电场和高效的器件隔离。

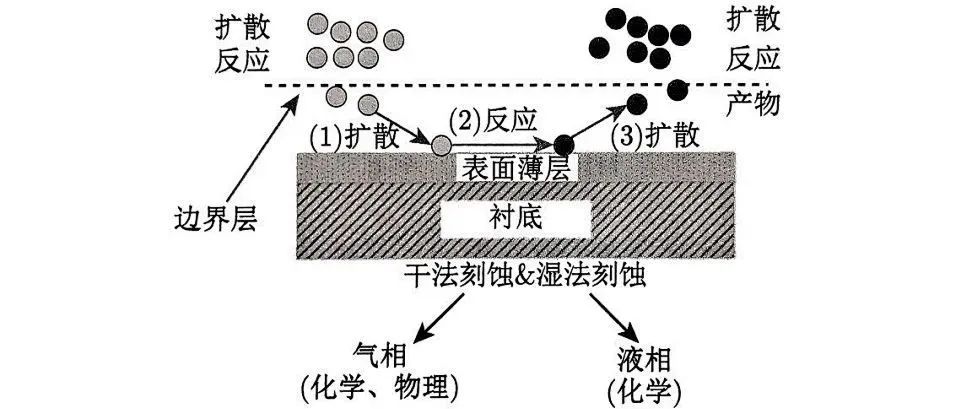

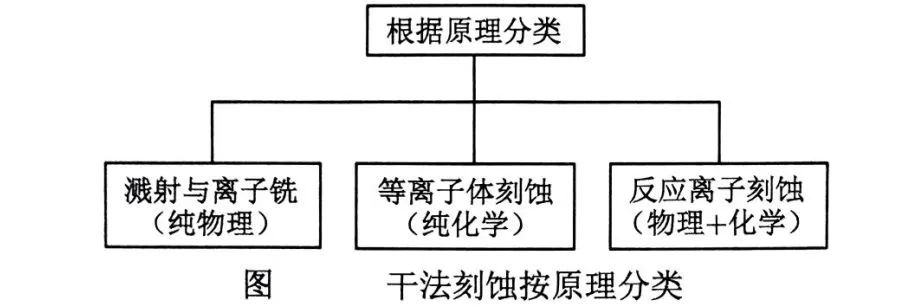

目前VCSEL刻蚀分为湿法刻蚀和干法刻蚀两种。为实现良好的形貌控制,GaAs基VCSEL的刻蚀通常采用干法刻蚀技术。干法刻烛具有精度高、可控性好、易于批量生产以及工艺清洁度高等优势。因此,深入研究高精度的刻蚀技术,尤其是高精度的干法刻蚀技术,对制备高性能VCSEL具有重要意义。

据麦姆斯咨询报道,近期,长春理工大学高功率半导体激光国家重点实验室的科研团队在《红外》期刊上发表了以“GaAs基VCSEL干法刻蚀技术研究综述”为主题的文章。该文章第一作者为范昊轩,主要从事半导体激光器件的研究工作;通讯作者为郝永芹研究员,主要从事半导体光电子材料与器件方面的研究工作。本文综述了GaAs基VCSEL干法刻蚀技术的发展与研究现状。

刻蚀中改善掩膜质量的研究现状

目前,VCSEL刻蚀过程中的关键环节主要有以下几个方面:控制台面的尺寸、刻蚀时掩膜的质量、刻蚀GaAs后的表面质量、VCSEL台面和侧壁形貌。

刻蚀VCSEL之前要进行光刻。常用的掩膜有光刻胶软掩膜,二氧化硅、氮化硅和金属硬掩膜。光刻胶掩膜通过前烘和坚膜之后形状会改变。由于在刻蚀气体氛围中光刻胶的抗蚀性不能保证稳定的状态,在刻蚀过程中高浓度的离子会使光刻胶掩膜变性或者碳化。另外,光刻胶掩膜的形状在刻蚀过程中会转移给下方的晶圆片,所以控制好掩膜的质量对刻蚀过程很重要。

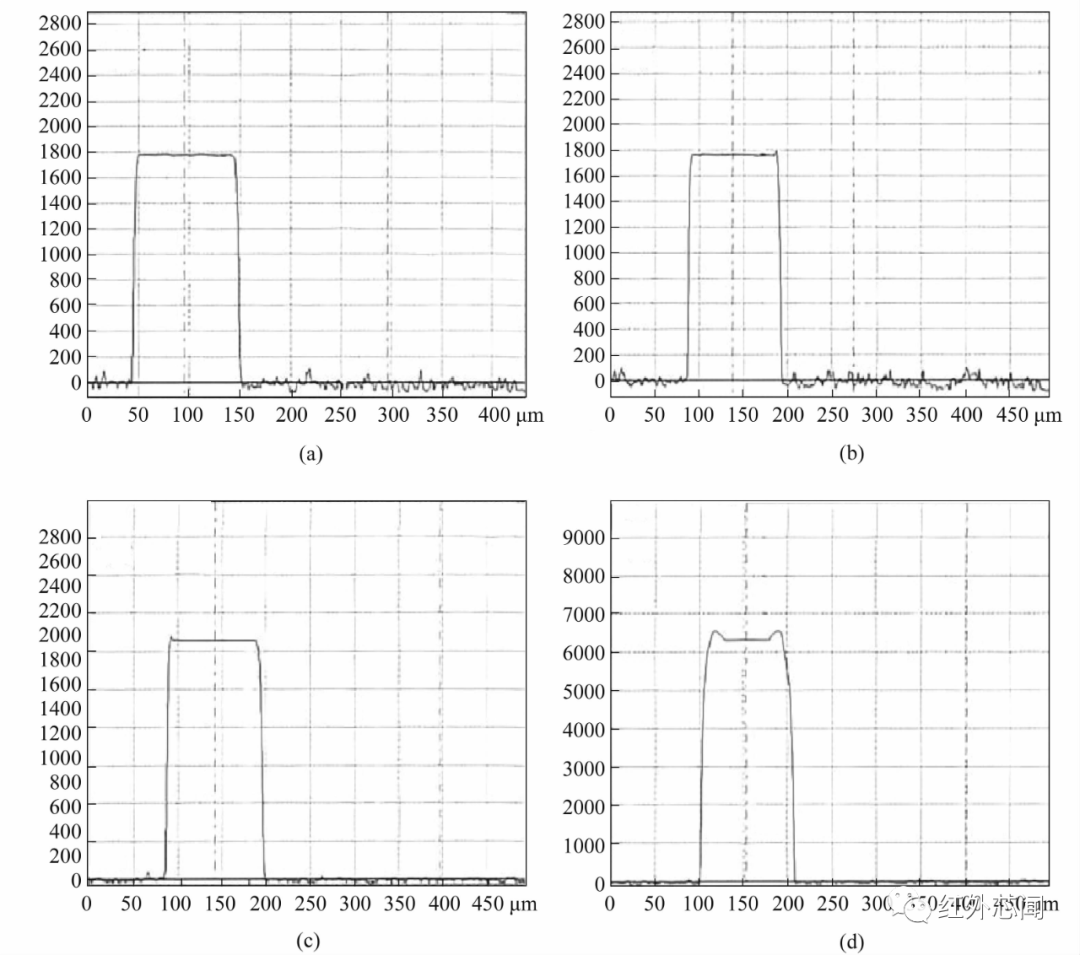

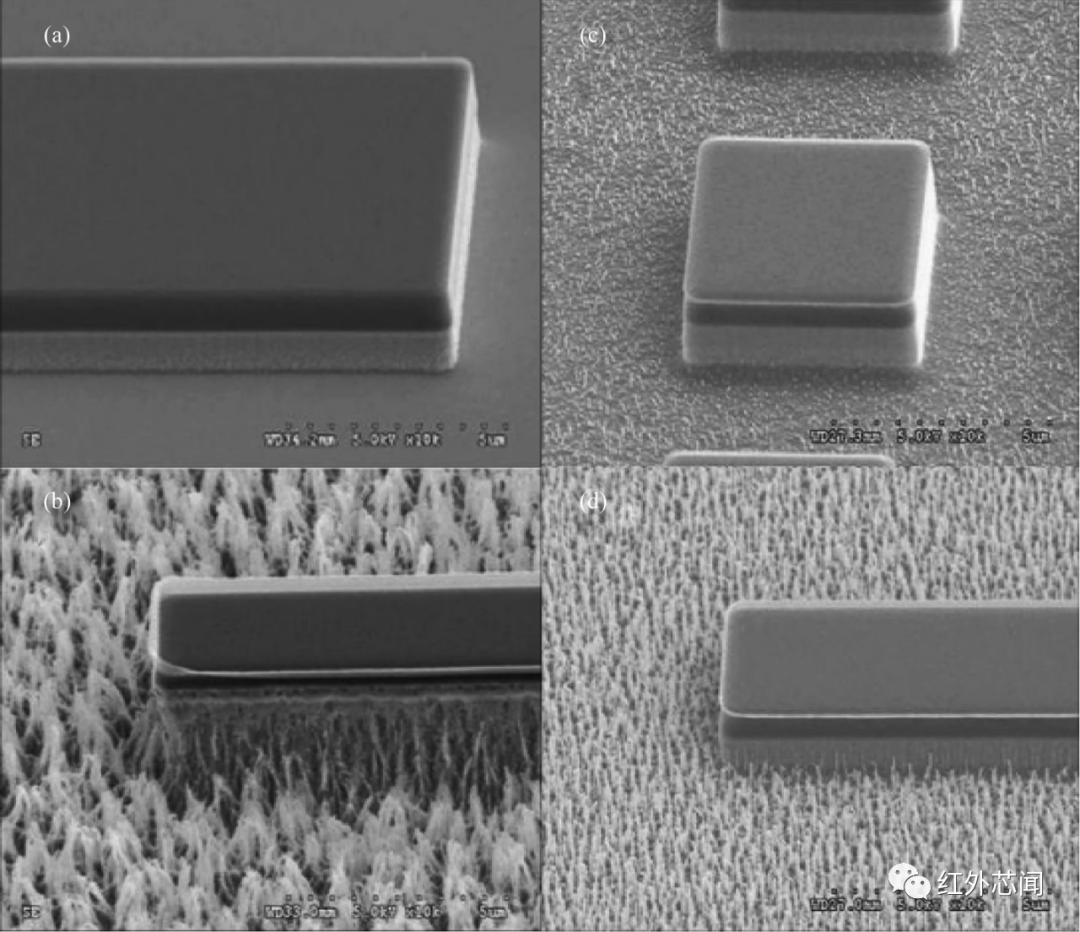

为了使光刻胶掩膜具有更好的形貌,研究人员通过对光刻胶厚度的分析,研究了不同厚度下光刻胶掩膜在烘烤后的变化规律。2012年,孙丽媛等人针对光刻胶掩膜对刻蚀GaAs材料侧壁的问题,采用控制变量法研究了厚度不同的光刻胶财GaAs材料侧壁倾角产生的影响。他们用台阶仪测量旋涂不同厚度光刻胶烘烤之后的结果,发现光刻胶的厚度越大,高温烘烤后光刻胶变性越严重,如图1所示。

图1

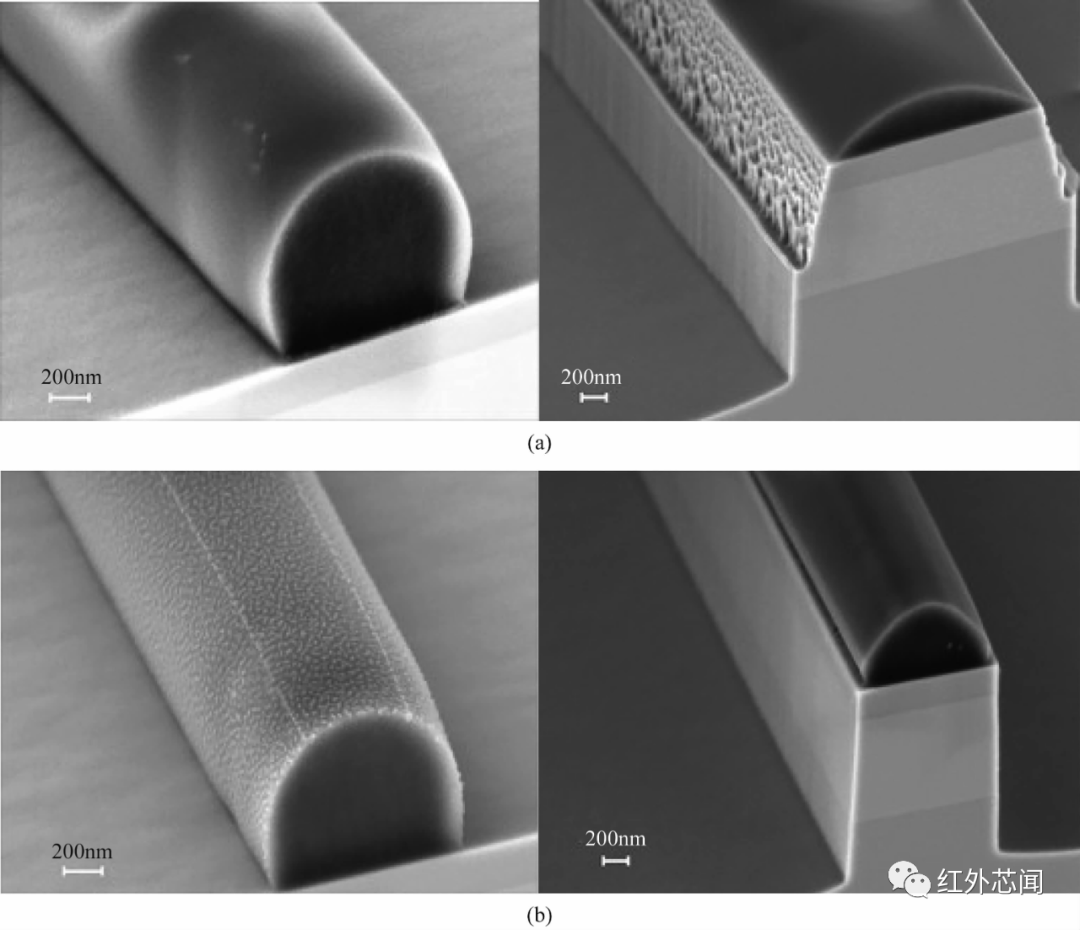

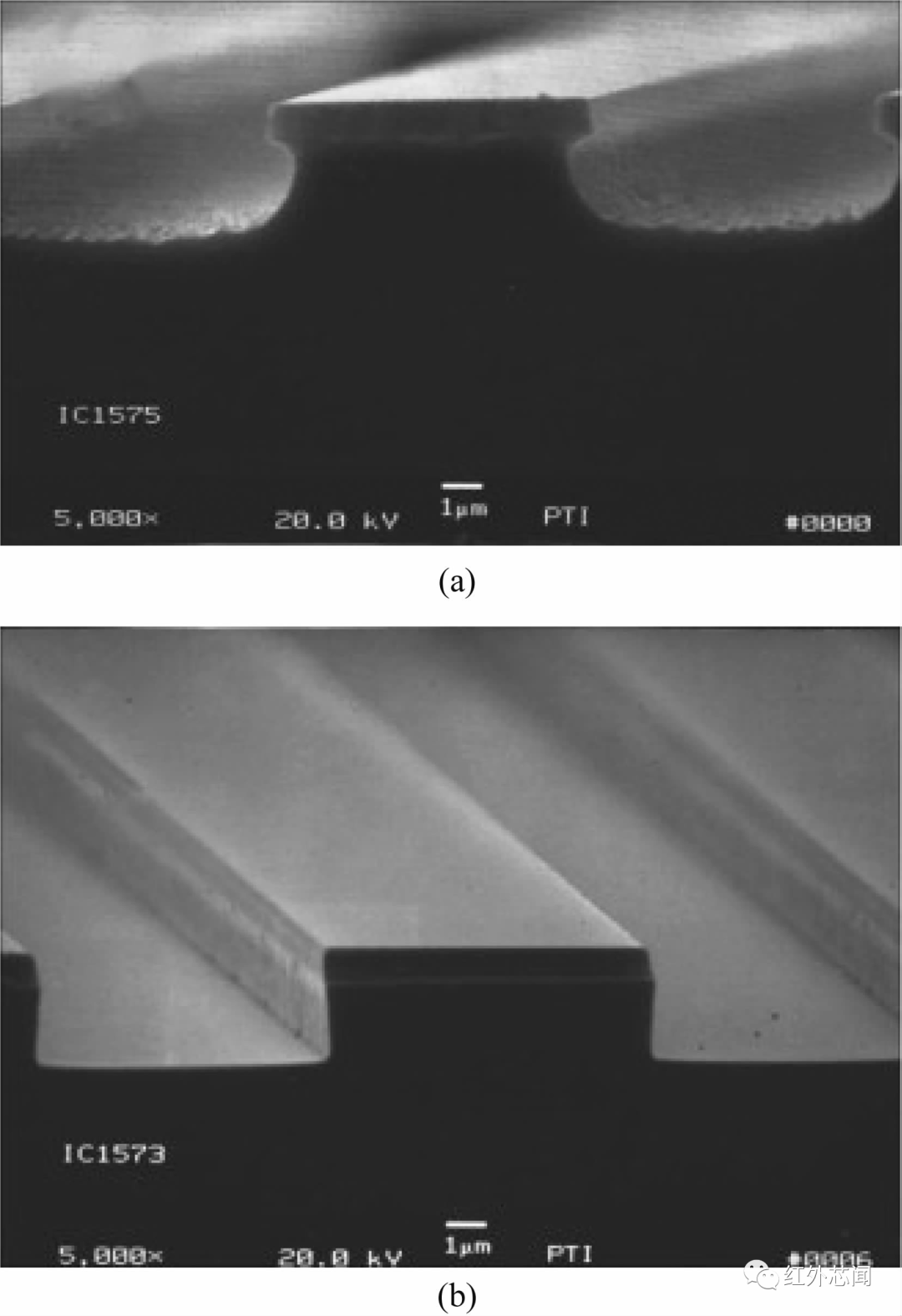

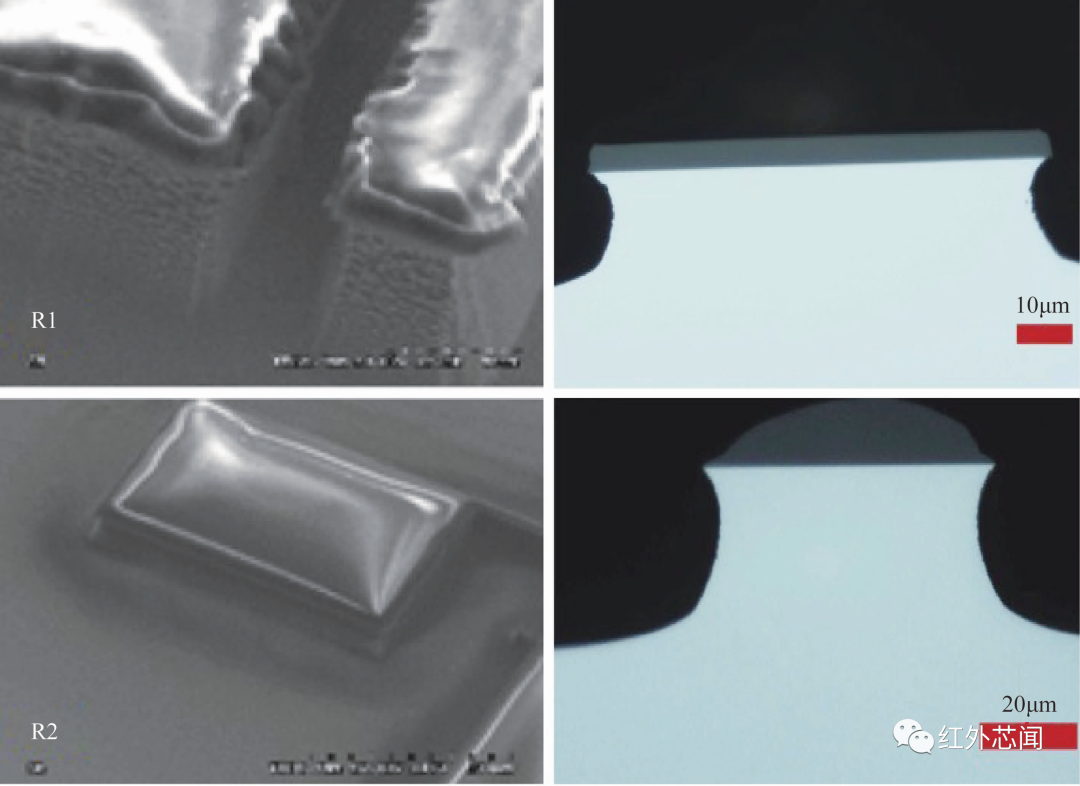

通过优化光刻胶掩膜回流方法,研究人员改善了光刻胶掩膜在回流后的形貌。2014年,Porkolab G A等人针对光刻胶掩膜回流时出现的坍塌变性问题,采用等离子体辅助回流方法改善了传统加热回流法的坍塌现象,如图2中的扫描电子显微镜(SEM)图像所示。

图2

2015年,焦庆斌等人发现了光栅顶部的光刻胶掩膜“顶角平台”现象(出现光刻胶掩模占宽比过大的情况)。针对这一问题,他们采用了改变光刻过程中的曝光时间和提高倒置热熔温度的方法。结果表明,通过增加曝光时间和提高倒置热熔温度,可明显减小占宽比以及光刻胶掩模线条宽度。

2016年,乔辉等人针对在电感耦合等离子体(ICP)干法刻蚀后光刻胶掩膜出现凸起和孔洞的异常现象,采用探针式表面轮廓仪和激光共聚焦显微镜对其进行了分析。他们认为,刻蚀时等离子体中的紫外线对掩膜的光刻胶进行曝光作用而释放出一定虽的氮气,在光刻胶内外形成了压强差,使光刻胶局部表面微凸起。当光刻胶的强度无法阻止内部氮气膨胀时,则会产生类似的孔洞状缺陷,导致掩膜保护作用失效。

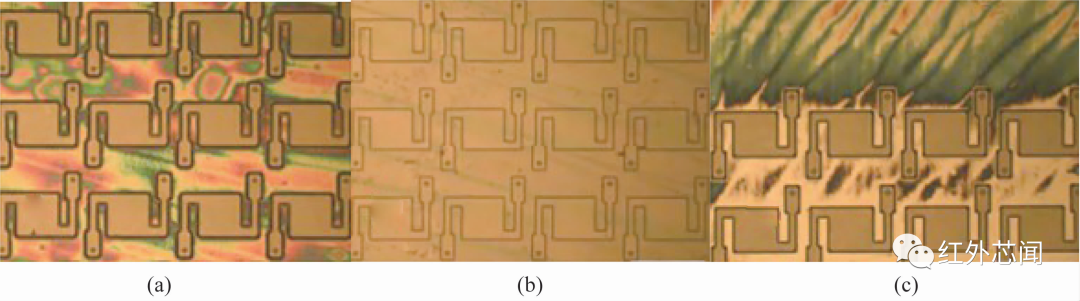

随着刻蚀技术的发展,工艺精度不断提高。2016年,艾骏等人针对光刻胶掩膜的光刻线条精度问题展开研究。他们分析了光刻时曝光时间长短(见图3(a))、显影时显影液的浓度(见图3(b))以及显影时显影的时间(见图3(c))对光刻胶掩膜的光刻线条精度的影响,探究了各种不良形貌出现的原因,为今后光刻技术在复杂环境下的应用和发展打下了基础。

图3

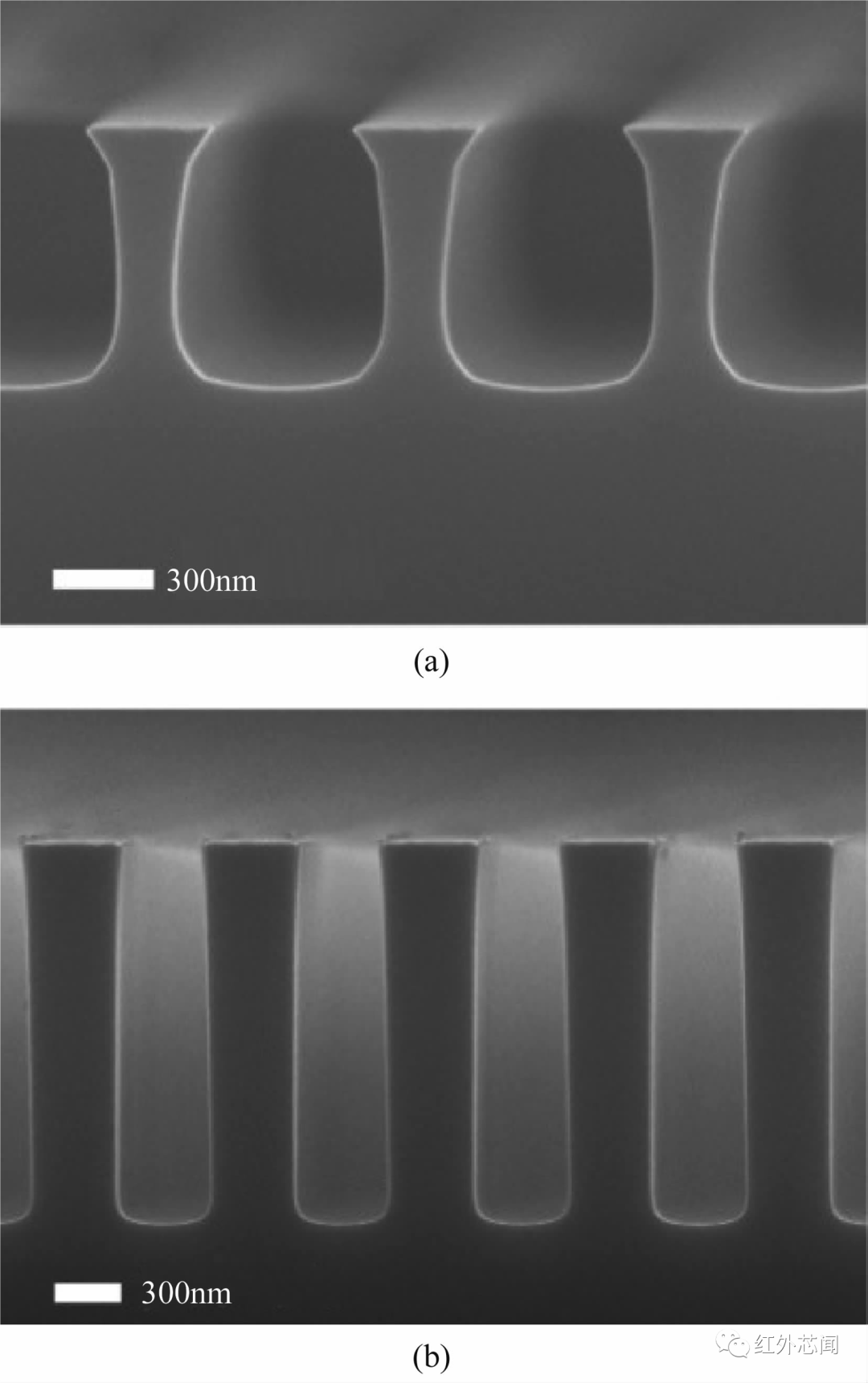

2018年,Vigneron P B等人发现刻蚀GaAs时光刻胶掩膜出现了“微掩蔽”现象。光刻胶掩膜的四角出现坍塌和波纹,如图4(a)所示。在刻蚀过程中会将这些波纹转移到下方的基片上,造成粗糙的侧壁,引起散射损伤。他们在BCl₃/Cl₂/Ar刻蚀气体组合中加入极少量N₂后,微掩蔽现象消失,如图4(b)所示。

图4

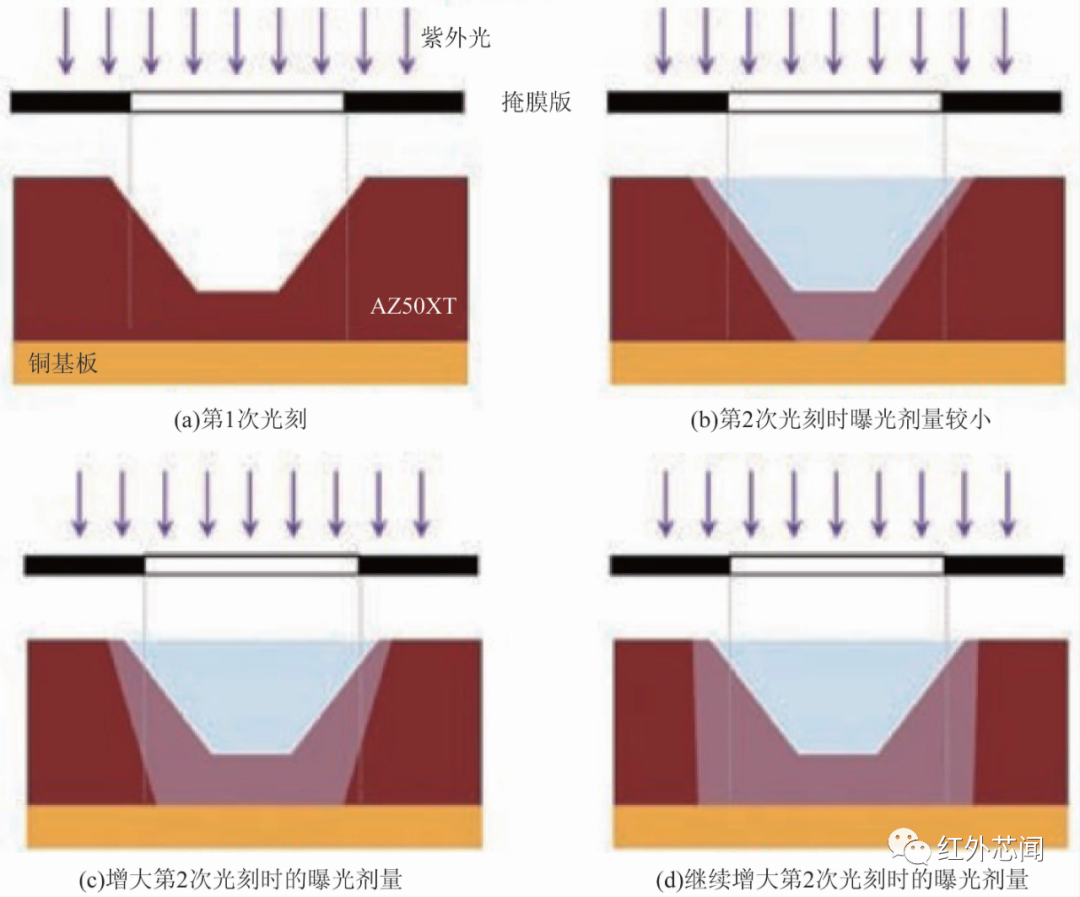

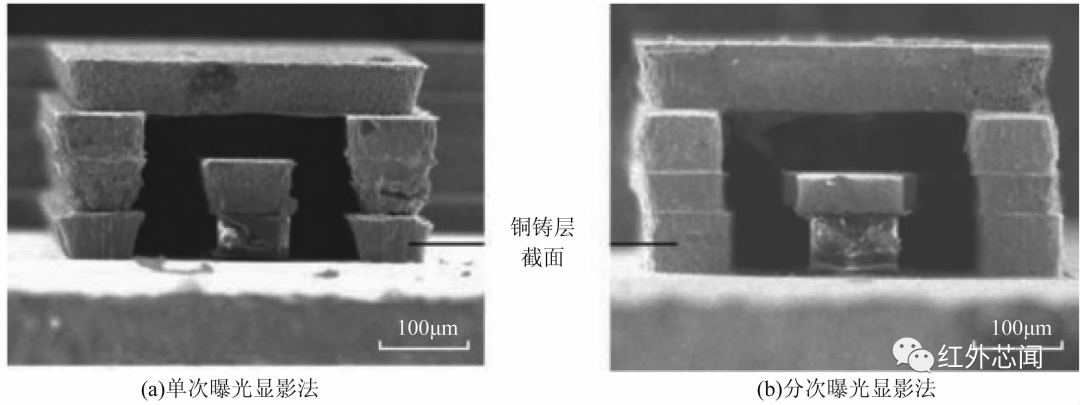

2018年,杜立群等人针对较厚的光刻胶掩膜在曝光过程中胶膜内部曝光剂量分布不均匀使得光刻胶掩膜厚度过大的情况,尝试采用分次曝光显影法改善无法控制光刻图形精度的问题。通过对基准点预曝光的分次曝光显影法调整光刻胶掩膜的厚度,对光刻胶掩模的均匀性以及光刻胶掩模内部的曝光剂量进行调节(原理见图5)。

图5 分次曝光显影法的原理图

分次曝光显影法的原理如下:首先去掉光刻胶顶部的掩膜,使光刻胶掩膜内部充分曝光;光刻胶掩膜顶部的线宽变小,底部掩膜的线宽变大,二者之间的差值变小。这方法可以显著改善光刻图形的尺寸精度,对厚胶的曝光起到了优化的作用(见图6)。

图6 射频同轴传输截面的SEM图

刻蚀GaAs的研究现状

在刻蚀GaAs方面,2000年Lee J W等人针对GaAs侧壁存在的钻刻现象,引用BCl₃/SF₆/N₂/He气体刻蚀GaAs结构,并通过添加N₂来增强刻蚀过程中的侧壁钝化功能。结果表明,刻蚀轮廓形貌得到了明显的改善,增强了各向异性刻蚀(见图7)。

图7

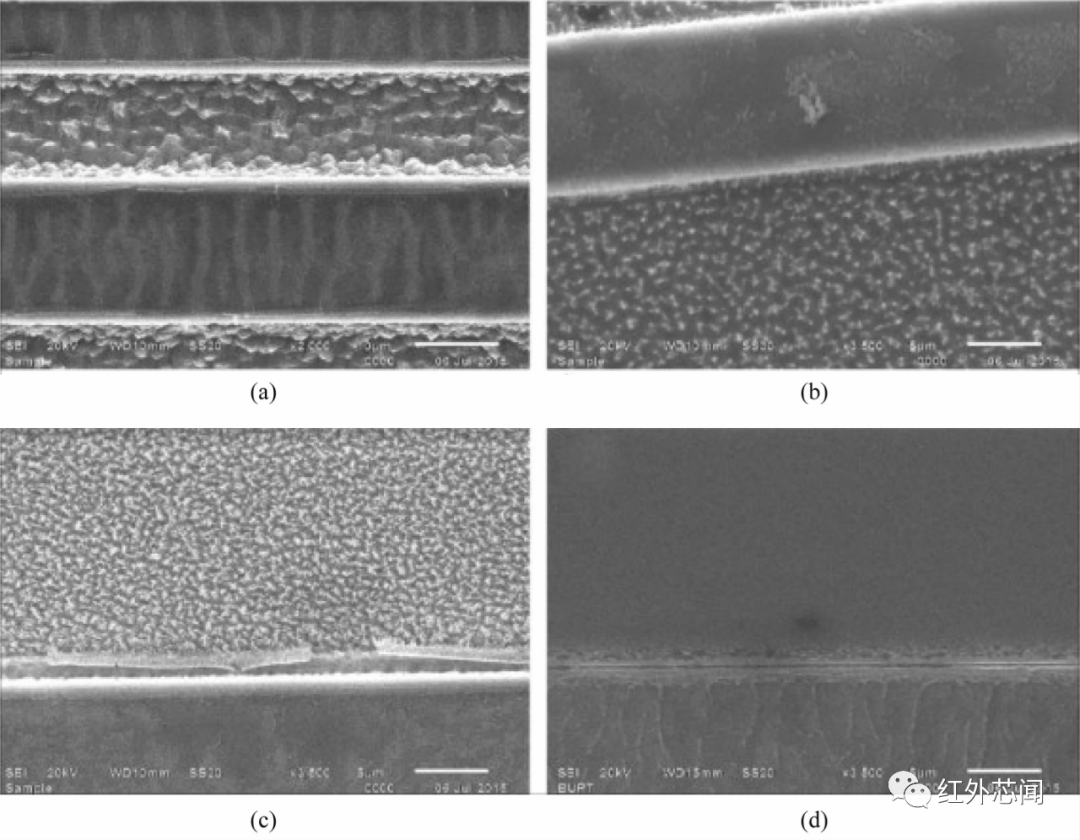

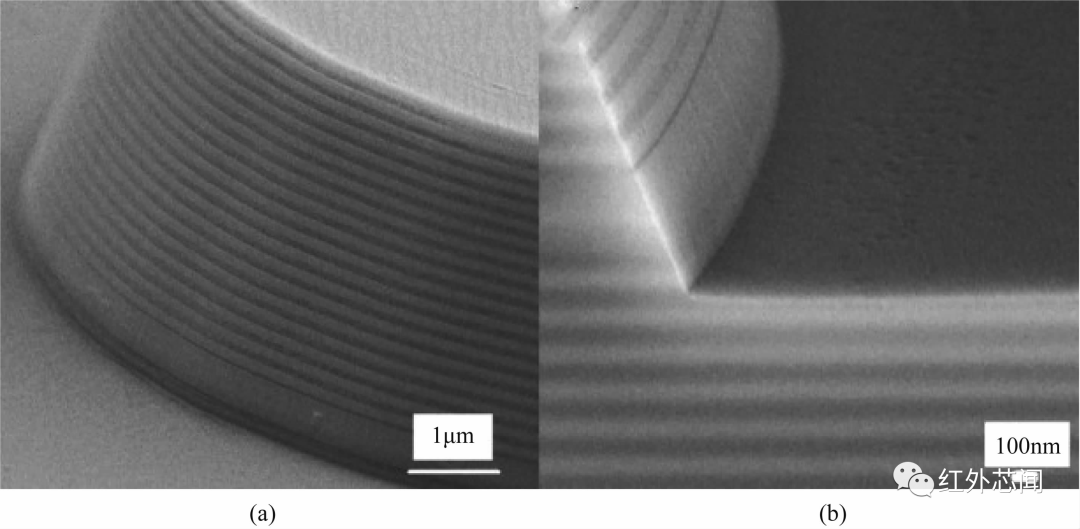

2010年,Volatier M等人针对刻蚀GaAs侧壁出现的横向刻蚀现象,在Cl₂/BCl₃/Ar中添加N₂以增加侧壁钝化保护。首先,添加N₂后增加的钝化层可以减少过度的横向蚀刻,从而产生各向异性剖面。其次,通过研究不同比例N₂相关数据可知,加入10%~13%的N₂时能够获得接近理想的各向异性结构。一旦N₂比例超过14%,GaAs的底部就会变得很粗糙。此研究改善了刻蚀GaAs侧壁时出现横向钻蚀的情况,如图8所示。

图8

2010年,Lee J W等人针对GaAs在刻蚀后存在表面粗糙的问题,研究了BCl₃/N₂和BCl₃/Ar两种组合的刻蚀机理。通过调节辅助气体N₂和Ar的比例来观察表面质量的好坏(见图9)。研究发现,添加过量的辅助气体会降低等离子体刻蚀的速率和选择性,从而对等离子体刻蚀产生负面影响,最终出现表面粗糙的现象。

图9

2015年,Liu K等人针对用Cl₂/Ar刻蚀GaAs时表面粗糙的问题,通过加入不同浓度的O₂来加以对比。他们分析了Cl₂/Ar/O₂的刻蚀机理,发现O₂的加入使GaAs的刻蚀速率减小,但表面质量变高,选择比变大,改善了GaAs在Cl₂/Ar刻蚀下表面粗糙的问题(见图10)。

图10

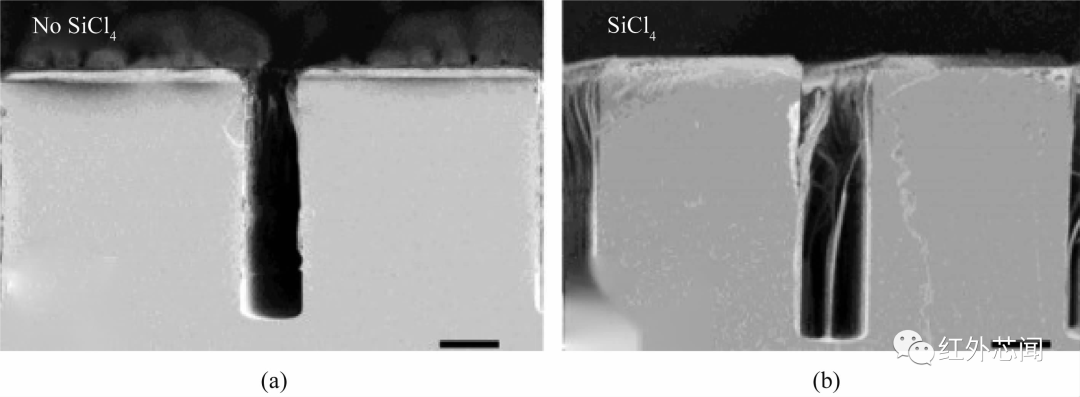

2019年,Booker K等人针对刻蚀GaAs通孔时出现横向刻蚀的问题,将SiO₂用作掩膜,并通过在Cl₂/Ar组合中加入SiCl₄,来完成刻蚀。这将促进通孔侧壁上的硅基聚合物持续形成,防止横向蚀刻再次破坏侧壁,如图11所示。

图11

2022年,杨晶晶等人针对刻蚀以SiO₂为掩膜时GaAs外延片出现的长草现象(见图12(a)),分析了刻蚀的机理,找出了刻蚀的副产物。这些副产物会产生“微掩膜”效应,从而影响刻蚀的结果。通过调整射频(RF)功率,增大了等离子体副产物粘附在基片的概率,减少了长草现象的发生,如图12(b)所示。

图12

刻蚀中改善GaAs/AlGaAs选择性刻蚀的研究现状

在GaAs/AlGaAs的刻蚀方面,1995年Constantine C等人针对GaAs和AlGaAs刻蚀速率有明显差异的问题,采用1:10的BCl₃/Ar气体组合,发现BCl₃可以去除铝氧化物,并在反应腔室内吸收水蒸气,防止AlGaAs的再次氧化,获得了更均匀的非选择性刻蚀。

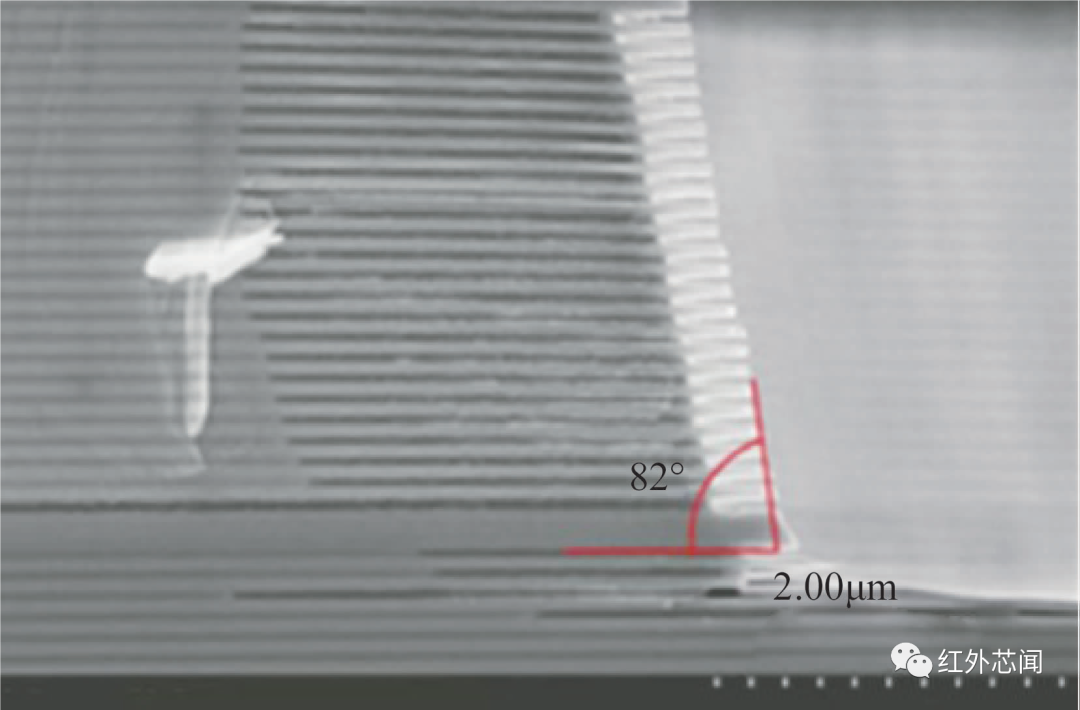

2018年,Vigneron P B等人针对GaAs/AlAs异质结刻蚀过程中出现的横向钻蚀问题(见图13),在BCl₃/Cl₂/Ar刻蚀气体组合中加入N₂诱导的钝化层,可以防止横向蚀刻,从而产生光滑且几乎理想的垂直侧壁。针对金属掩膜和光刻胶掩膜的微掩膜效应,通过加入Ar气带走这些反应副产物。为了解决损伤问题,他们加入N₂作为辅助气体,结果是微掩膜效应完全消失。等离子体中的N₂浓度提高了刻蚀剖面的平滑性。接着增加BCl₃,气体以降低腐蚀速率,同时增加压力以提高选择性,得到了侧壁垂直且光滑的形貌。

图13 GaAs/AlAs侧壁的SEM图像

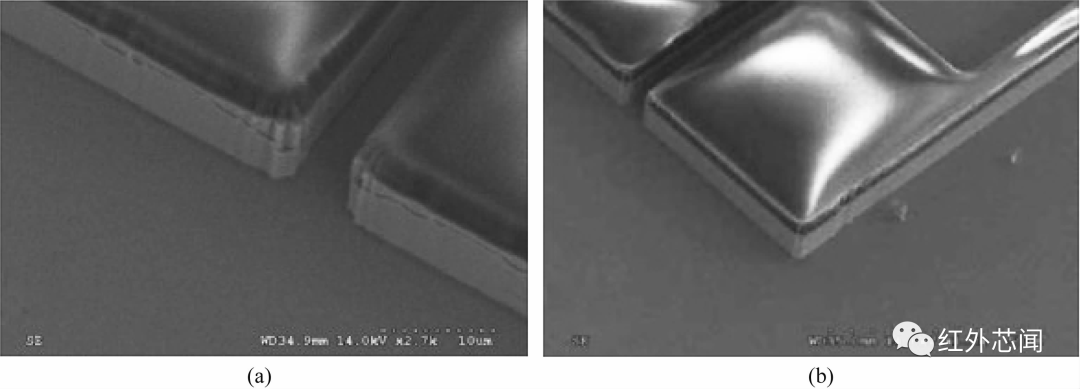

2019年,王宇等人针对GaAs/AlAs侧壁的横向钻蚀问题和VCSEL基脚不平坦问题,采用SiO₂硬掩膜并调整ICP源功率和RF功率两个参数,在保证高刻蚀速率的条件下,得到了侧壁角度为60°~70°且侧壁光滑的形貌。调节腔室内压强的大小,减少了反应的副产物,改善了台面的平坦度,降低了基脚效应(见图14)。

图14 优化后的侧壁和基脚

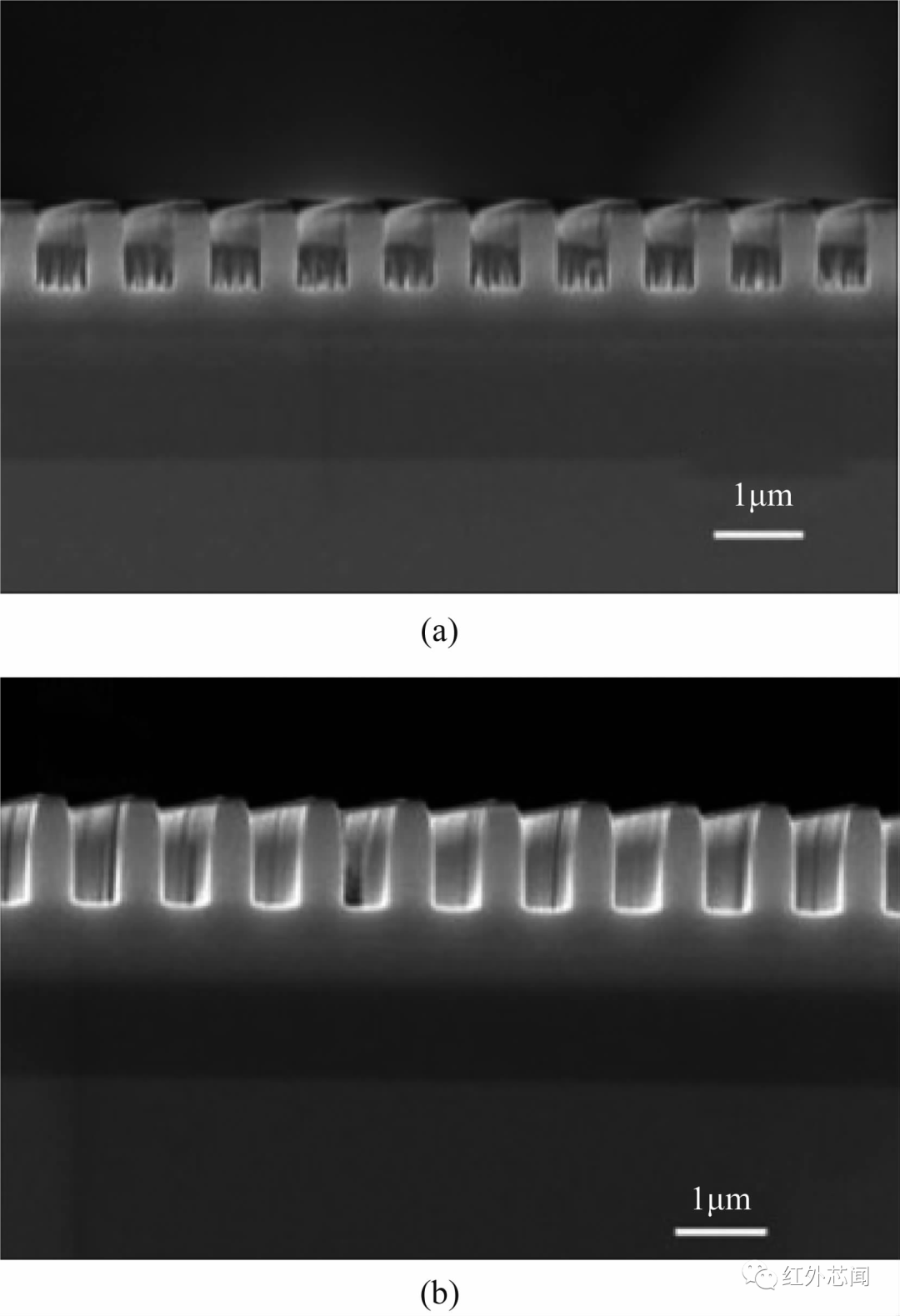

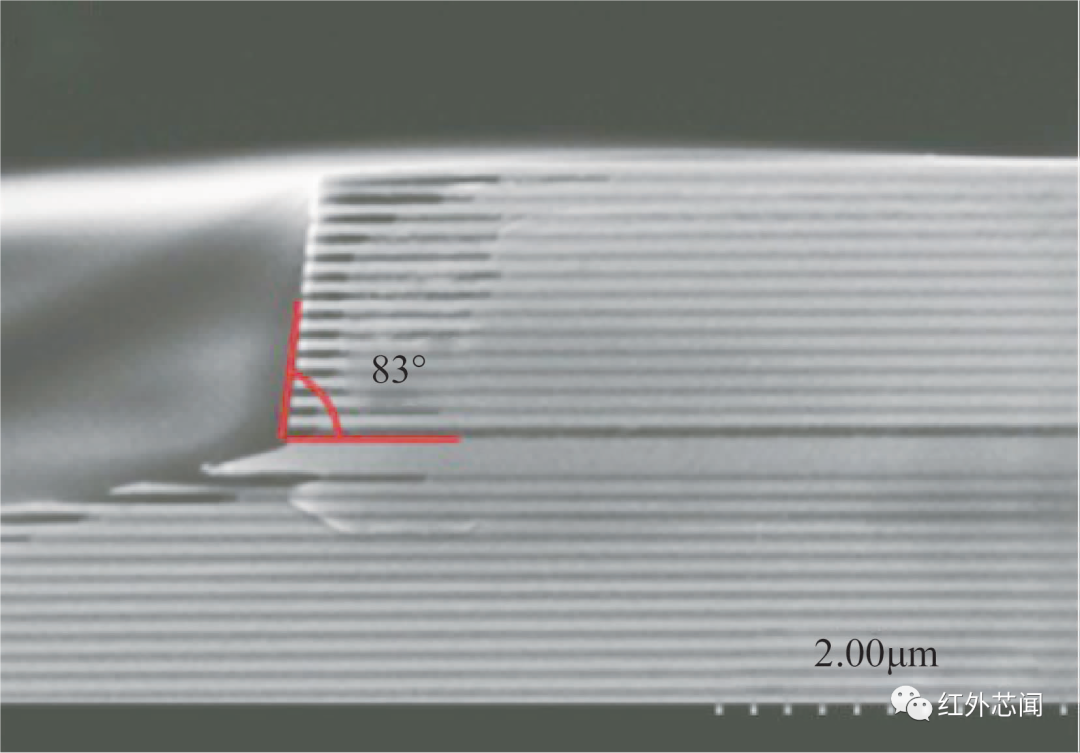

2020年,张秋波等人针对ICP刻蚀氧化限制型VCSEL时出现的选择性刻蚀(镂空)现象(见图15),用SiO₂掩膜刻蚀VCSEL,通过调整RF功率增强刻蚀中的物理效应;通过调整BCl₃,气体的流量组分,使VCSEL的侧壁钝化效果增强;采用ICP刻蚀时增强了RF功率,使反应腔室内达到化学和物理效应的动态平衡;增强的物理刻蚀轰击掉镂空的部分,如图16所示。

图15和图16

结束语

本文对VCSEL干法刻蚀关键技术的进展和研究现状进行了综述(主要包括刻蚀时掩膜的质量、刻蚀GaAs后的表面质量、VCSEL的表面和侧壁形貌)。目前,国际上对VCSEL刻蚀技术进行了广泛而深入的研究,在制备掩膜、增强GaAs的各向异性刻蚀以及实现多层分布式布拉格反射器(DBR)的非选择性刻蚀方面取得了重要进展。但针对介质掩膜的优化和去残胶工艺、刻蚀气体与材料的作用机理及规律、刻蚀过程中出现的副产物问题等研究较少。随着各个领域对VCSEL的需求增大,对VCSEL刻蚀技术的精度也会提出更高的要求。

审核编辑:刘清

-

SEM

+关注

关注

0文章

274浏览量

15713 -

GaAs

+关注

关注

3文章

893浏览量

25172 -

激光雷达

+关注

关注

982文章

4531浏览量

197046 -

vcsel技术

+关注

关注

0文章

7浏览量

987

原文标题:综述:GaAs基VCSEL干法刻蚀技术研究

文章出处:【微信号:MEMSensor,微信公众号:MEMS】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体制造中的侧墙工艺介绍

国星光电入选2025年度佛山市工程技术研究中心

干法刻蚀机在精密光栅加工中的应用优势

MEMS制造中玻璃的刻蚀方法

双三相永磁同步电机多矢量控制技术研究

双定子直线振荡电机动子位移自传感技术研究

三相永磁同步电机直接转矩控制技术研究

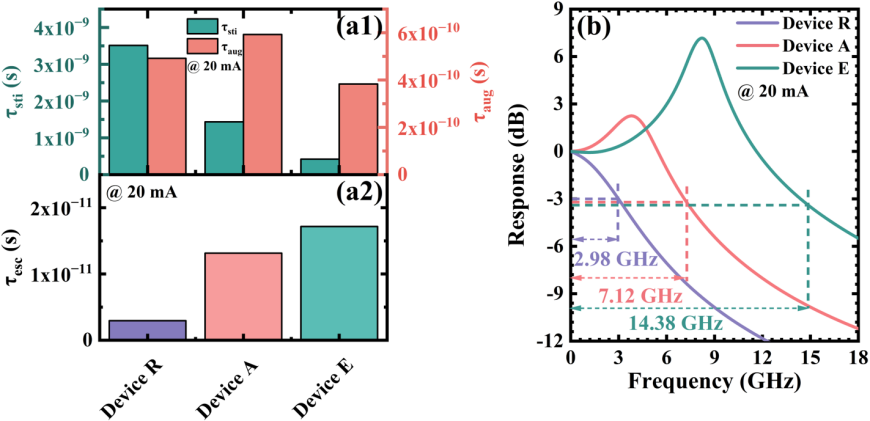

新成果:GaN基VCSEL动态物理模型开发

一文详解湿法刻蚀工艺

GaAs基VCSEL干法刻蚀技术研究

GaAs基VCSEL干法刻蚀技术研究

评论