PCB铺铜的优缺点

1

优点

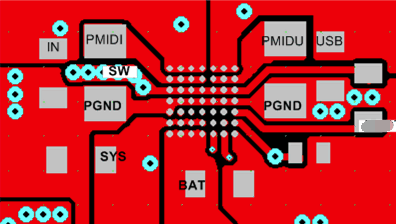

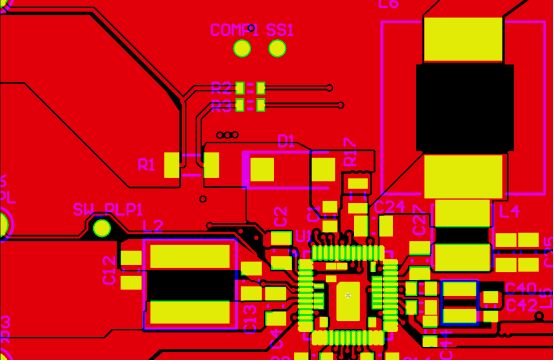

对于PCB工艺制造要求,一般为了保证电镀的镀铜均匀效果,或者层压不变形弯曲,对于布线较少的PCB板层铺铜。

对于信号完整性要求,给高频数字信号一个完整的回流路径,并减少直流网络的布线。当然还有散热,特殊器件安装要求铺铜等等原因。

2

缺点

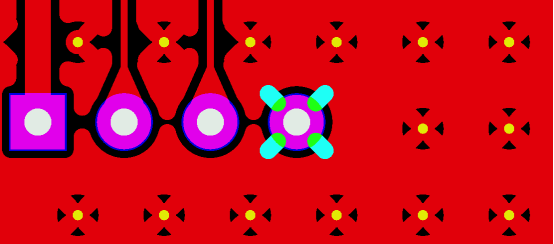

如果对元器件管脚进行铺铜全覆盖,可能导致散热过快,从而导致拆焊和返修时困难。所以有时为了避免这种情况,对元器件采用十字连接(引脚接触和焊盘接触为“十”字)。

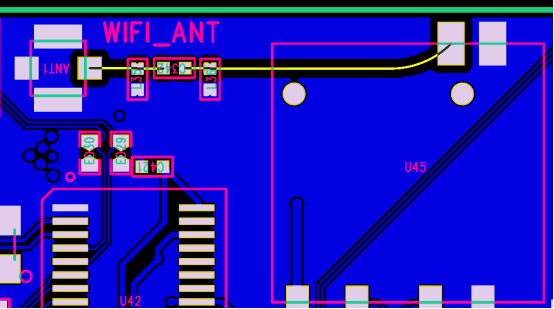

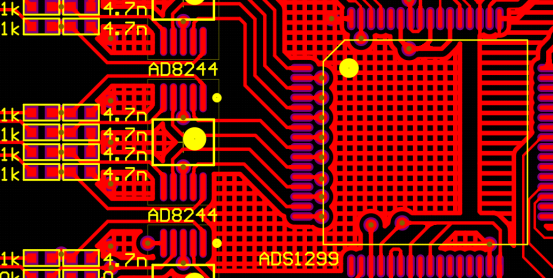

在天线部分周围区域铺铜容易导致信号弱,采集信号受到干扰,铺铜的阻抗会影响到放大电路的性能。所以天线部分的周围区域一般不会铺铜。

PCB铺铜的形状

1

实体形状铺铜

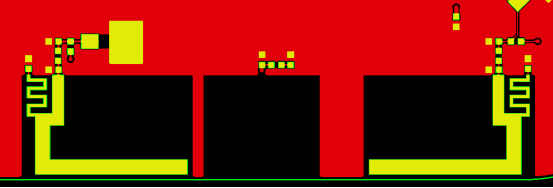

实体敷铜,具备了加大电流和屏蔽的双重作用。但是实体覆铜,如果过波峰焊时,有一定的热胀冷缩的拉力,板子可能会翘起来,甚至会起泡。因此实体敷铜,一般会开几个槽,缓解拉力导致铜箔起泡。

2

网格形状铺铜

网格敷铜,主要起到屏蔽作用,加大电流的作用会被降低。从散热的角度说,网格敷铜既降低了铜的受热面,又起到了一定的电磁屏蔽作用。但是生产工艺对网格形状铺铜有一定的要求,网格过小影响品质良率。

PCB铺铜的设计

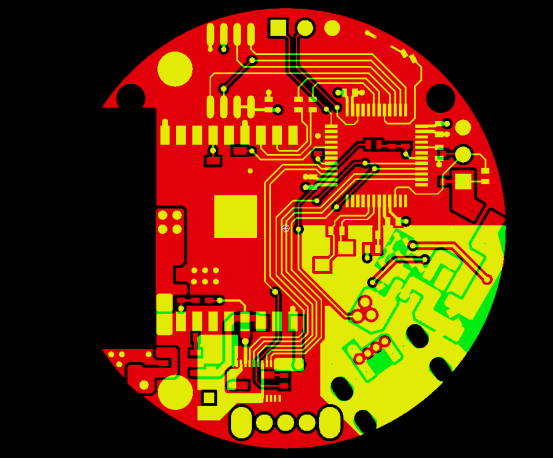

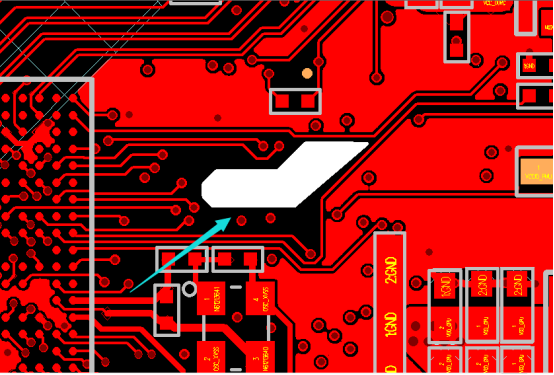

在PCB设计的时,一般PCB的每个面都要覆铜接地,主要原因是防止PCB弯曲变形和各种信号干扰、串扰。

所以在走线时要覆铜接地。但是由于外层有大量的元件及走线,所以铜箔会被这些元件焊盘及其走线分割成许多小的孤铜及细长的铜皮。

1

处理碎铜

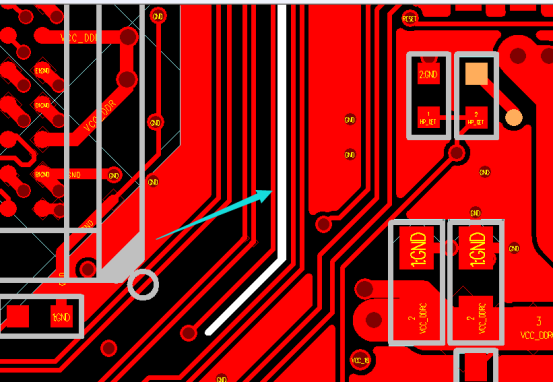

那些细细长长的接地不良的地铜会具有天线效应,会引起EMC不良问题。所以要尽量避免在覆铜时引起碎铜,如引起碎铜可删除处理。

2

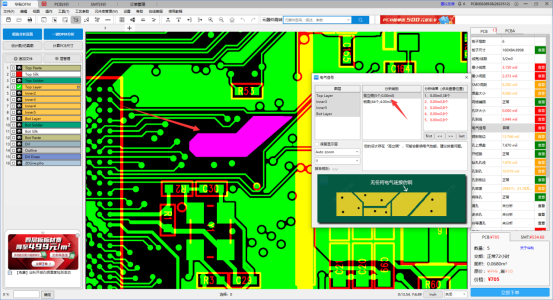

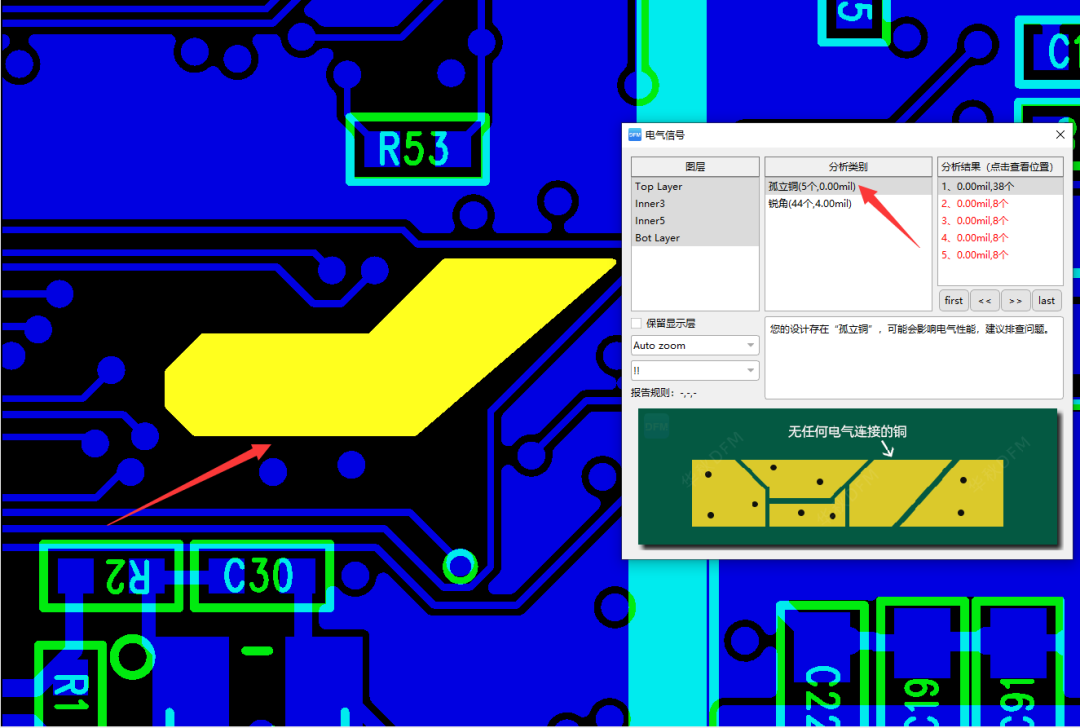

处理孤立铜

孤岛(死区)铜问题,孤立铜如果比较小等同于碎铜,可删除处理。如果很大,可定义为某个地,进行添加过孔处理,此时就不存在孤立铜了。

PCB铺铜的可制造性设计检查

关于碎铜、孤立铜的可制造性问题,碎铜在生产制造过程中因细长的特征会被蚀刻掉,从而导致铜分离,脱落在其他位置导致不同网络短路。

孤立铜在板厂CAM工程师处理生产文件时,会提出询问与设计工程师确认,因为无网络链接的孤立铜属于异常设计。所以设计存在孤立铜会浪费沟通成本,耽误生产周期。

这里推荐一款华秋DFM软件,可以一键分析孤立铜,在制造前拦截设计文件的异常,提醒设计工程师避免设计错误,导致产品设计失败,并可减少与板厂的沟通成本,缩短生产周期。

华秋DFM软件主要的功能包括:PCB裸板分析、PCBA装配分析、优化方向推荐、价格交期评估、供应链下单、阻抗计算等工具。

能够满足工程师需要的多种场景,在制造前期解决或发现所有可能的质量隐患,将产品研制的迭代次数降到最低,减少成本。

目前华秋DFM推出了新版本,可实现制造与设计过程同步,模拟选定的PCB产品从设计、制造到组装的整个生产流程。

华秋DFM使BOM表整理、元器件匹配、裸板分析及组装分析四个模块相互联系,共同协作来完成一个完整的DFM分析!

软件下载地址(复制到浏览器下载) ↓

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_hqsc.zip

原文标题:【PCB设计】搞定PCB铺铜,这篇就够了!(附设计要点详解)

文章出处:【微信公众号:华秋商城】欢迎添加关注!文章转载请注明出处。

-

华秋商城

+关注

关注

8文章

119浏览量

8663

原文标题:【PCB设计】搞定PCB铺铜,这篇就够了!(附设计要点详解)

文章出处:【微信号:华强芯城,微信公众号:华秋商城】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

射频前端设计的阻抗匹配和铺铜距离参数解析

07. 如何在Allegro中设置可以走线但不能铺的铜区域?| 芯巧Allegro PCB 设计小诀窍

射频PCB的“隐形杀手”:90%的工程师都忽视的铺铜细节!

高速PCB工程师必看:用仿真三步法,让铺铜从“隐患”变“保障”

PCB拼板三大细节要点

从设计阶段排查预防PCB短路

如何选择一家可靠的PCB设计公司?

PCB拼版三大细节要点

浅谈晶振在PCB设计中的要点

高速PCB设计EMI避坑指南:5个实战技巧

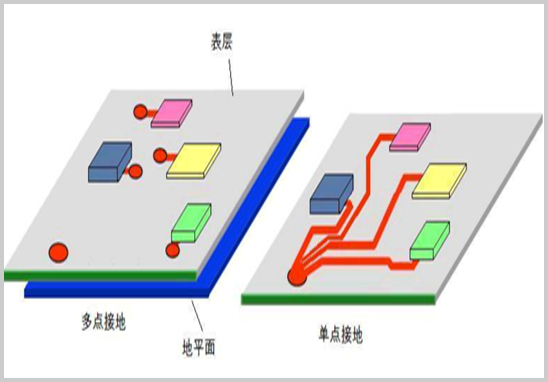

PCB设计中单点接地与多点接地的区别与设计要点

【PCB设计】搞定PCB铺铜,这篇就够了!(附设计要点详解)

【PCB设计】搞定PCB铺铜,这篇就够了!(附设计要点详解)

评论