射频前端难调?阻抗匹配和铺铜距离决定了成败

一个让人头疼的调试现场

上个月帮朋友看一个2.4GHz WiFi模块的设计,原理图没问题,器件选型也合理,但就是灵敏度比规格书低了8dB。换了几个厂家的模块,结果都差不多。最后发现是PCB布线的问题——射频走线两侧铺铜距离太近,把阻抗"吃"掉了。

说实话,这种情况我见得太多了。很多工程师对射频前端设计有一个误区:以为选对器件、画对原理图就够了。其实射频PCB设计里,阻抗匹配和铺铜距离这两个细节,往往决定了成败。

射频前端难调,难就难在这些看不见的"隐形参数"。今天聊聊这两个容易被忽视的关键点。

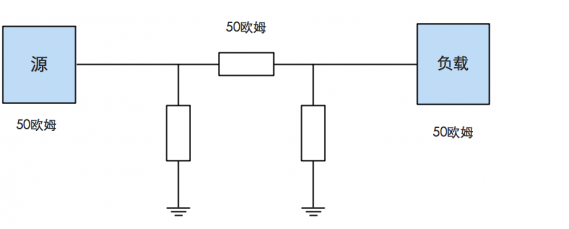

阻抗匹配:射频设计的"生死线"

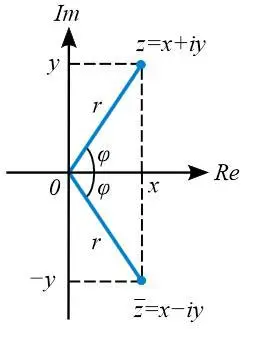

先说阻抗匹配,这个是射频设计的核心。射频信号在传输线上传播时,如果遇到阻抗不匹配,就会产生反射。反射信号和入射信号叠加,形成驻波,导致信号失真、功率传输效率下降。

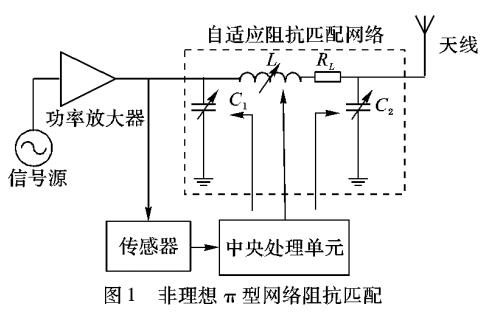

图1:Smith圆图 - 阻抗匹配的图形化工具

举个直观的例子:50Ω传输线连接75Ω负载,反射系数是0.2,回波损耗约-14dB。这意味着有4%的功率被反射回来了。听起来不多?但在射频系统里,这4%可能就意味着通信距离缩短一半。

关键指标你得懂

评估阻抗匹配质量,主要看三个指标:

回波损耗(Return Loss, RL):反射信号与入射信号的功率比,单位dB。数值越负越好,一般要求≤-15dB,优质设计要≤-20dB。

驻波比(VSWR):驻波电压最大值与最小值之比。理想值是1,实际设计要求≤1.5,高频场景要≤1.2。

阻抗控制精度:一般要求±5%,毫米波应用要±3%。

【案例】某5G基站射频模块,工作频率3.5GHz,设计要求VSWR≤1.3。实测发现个别通道VSWR达到1.8,排查后是微带线宽度蚀刻偏差+0.05mm,导致阻抗从50Ω偏到54Ω。调整蚀刻工艺后,VSWR降到1.25。

匹配网络怎么选

实现阻抗匹配的方法有好几种,选对了事半功倍:

微带线/带状线阻抗控制:最基础的方法。通过计算线宽、介质厚度、介电常数,实现目标阻抗。比如FR-4板材,1.6mm厚度,50Ω微带线宽度约1.8mm。

λ/4阻抗变换器:适合窄带匹配。利用四分之一波长传输线的阻抗变换特性。公式是Z_λ/4 = √(Z0×ZL)。比如50Ω匹配75Ω,变换段阻抗约61Ω。

LC匹配网络:最常用,适合宽带匹配。有L型、π型、T型等拓扑结构。设计时用Smith圆图工具计算LC参数,选用高Q值电容电感。

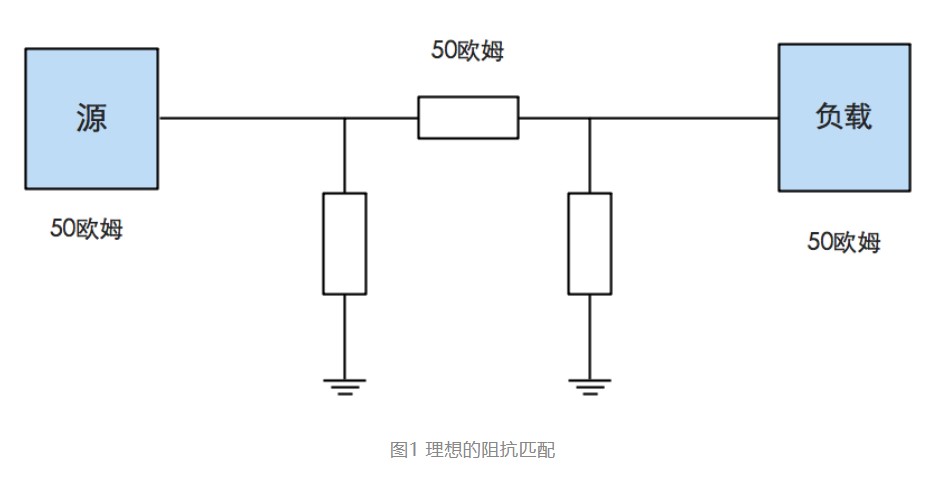

铺铜距离:被忽视的"隐形杀手"

说完阻抗匹配,再来说铺铜距离。这个是很多工程师踩坑的地方。

射频PCB设计中,铺铜(敷铜)是一把双刃剑。铺得好,能提供良好的接地参考和电磁屏蔽;铺不好,会改变传输线阻抗,引入寄生参数,成为"隐形杀手"。

射频线两侧铺铜的影响

当射频走线两侧有铺铜时,传输线结构就变成了"共面波导"。这时候,阻抗不仅由线宽和介质厚度决定,还和铜皮与走线的间距密切相关。

间距越小,阻抗越低,但损耗越大。这个变化不是线性的,在某些间距下会急剧变化。

图2:铺铜距离对阻抗和损耗的影响

【注意】对于2.4GHz、5GHz等通用射频线,两侧保留0.2-0.5mm的净空区是常见做法。低于0.2mm,阻抗和损耗都会明显恶化。

我个人觉得,如果需要精确控制阻抗,应该在设计阶段就通过仿真确定间距,而不是凭感觉铺铜。

什么时候不能铺铜

有些区域是"禁铺铜区",必须保持净空:

晶振和时钟电路下方 :至少0.3mm范围内禁止铺铜,防止串扰和辐射。

天线及匹配网络周围 :严格按参考设计留出净空区,匹配网络区域也要保持"干净"。

高阻抗节点 :如滤波器输入输出节点,周围需保持净空,避免寄生电容影响滤波效果。

接地过孔的"缝合"技巧

铺铜必须连接到GND网络,悬空的"孤岛铜"会成为天线,接收和辐射噪声。

处理方法是用缝合过孔(Via Stitching)将不同层的GND铜皮多点连接,形成低阻抗的"地墙"。过孔间距建议小于最高工作频率波长的1/20。

举个例子:2.4GHz信号,波长约125mm,λ/20约6mm。所以接地过孔间距控制在5mm以内是比较稳妥的。

图3:接地过孔屏蔽墙示意图

实战设计要点

结合我的经验,总结几条实战设计要点:

阻抗控制优先

射频走线的阻抗控制是第一位的。先用阻抗计算工具(如SI9000)计算线宽,然后通过电磁仿真软件(如ADS、HFSS)验证。设计时保持线宽均匀,避免突变。

微带线与器件引脚过渡处做圆弧倒角,半径≥0.5mm,减少阻抗突变。

参考地平面完整

射频信号层相邻的地平面必须完整,无开槽、无镂空。任何切割都会破坏回流路径,导致阻抗不连续。

【示例】某WiFi模块,微带线下方接地层有1mm宽的开槽。实测阻抗从50Ω突变到55Ω,回波损耗从-18dB恶化到-12dB。移除开槽后恢复正常。

铺铜距离合理规划

射频走线两侧铺铜距离,按以下原则:

常规射频线(≤6GHz):≥0.3mm

高频射频线(6-10GHz):≥0.4mm

毫米波(>10GHz):建议不做侧面铺铜,或按仿真结果确定

接地过孔密集布置

射频模块周围、关键信号线两侧,用密集的接地过孔形成"屏蔽墙"。过孔间距≤λ/20,高频应用可以更密。

过孔与信号线的间距建议为线宽的1-3倍,既能提供良好屏蔽,又不影响阻抗。

仿真验证必不可少

高速、高频设计,不要完全靠经验。用电磁仿真工具检查阻抗匹配、串扰、辐射性能。特别是铺铜距离的影响,仿真一眼就能看出来。

【建议】设计完成后,做一次S参数仿真。检查S11(回波损耗)在工作频段内是否满足要求,S21(插入损耗)是否在预期范围内。发现问题早修改,比投板后再改成本低得多。

图4:射频PCB布局要点示意图

常见误区澄清

最后说几个常见的误区:

误区一:"铺铜越多越好"

错!射频区域盲目铺铜会改变阻抗,增加损耗。铺铜要有策略,该留净空的地方必须留净空。

误区二:"接地过孔随便打"

错!接地过孔的位置和间距都有讲究。太密会增加加工成本,太疏屏蔽效果不够。按λ/20原则布置是比较合理的。

误区三:"阻抗50Ω就够了"

不完全对。阻抗控制精度也很重要。±5%是基本要求,高频应用要±3%。设计时要考虑工艺偏差,留出余量。

总结

射频前端难调,很多时候不是器件的问题,而是PCB设计细节没做到位。阻抗匹配和铺铜距离,这两个"隐形参数"往往决定了射频性能的成败。

核心要点记住这几条:

阻抗匹配是基础 :回波损耗≤-15dB,VSWR≤1.5,控制精度±5%

铺铜距离要合理 :射频线两侧保留0.2-0.5mm净空,敏感区域禁止铺铜

接地平面要完整 :射频走线下方地平面不能有切割

缝合过孔按规则 :间距≤λ/20,形成低阻抗地墙

仿真验证不能省 :投板前做S参数仿真,早发现早修改

射频设计没有捷径,但掌握这些要点,至少能避开最常见的坑。希望这些经验对你有帮助。

-

阻抗匹配

+关注

关注

14文章

371浏览量

32138 -

射频前端

+关注

关注

5文章

293浏览量

25233 -

射频设计

+关注

关注

0文章

62浏览量

9143

原文标题:射频前端难调?阻抗匹配和铺铜距离决定了成败

文章出处:【微信号:射频微波研究院,微信公众号:射频微波研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

从阻抗匹配的角度来解析射频微波传输线的设计技术

基于Ansoft Designer的射频功放电路阻抗匹配优化

怎样理解阻抗匹配_pcb阻抗匹配如何计算

阻抗匹配原理解析

阻抗匹配的原理及应用

RF芯片和天线间的阻抗匹配设计

为什么要阻抗匹配?怎么进行阻抗匹配?

射频前端设计的阻抗匹配和铺铜距离参数解析

射频前端设计的阻抗匹配和铺铜距离参数解析

评论