在电路设计中,系统晶振时钟频率很高,干扰谐波出来的能量也强,谐波除了会从输入与输出两条线导出来外,也会从空间辐射出来,这也导致在PCB设计中对晶振的布局要求严格,如果出错会很容易造成很强的杂散辐射问题,并且很难通过其他方法来解决,所以在PCB板布局时对晶振和CLK信号线布局很关键。

布局与走线设计

晶振内部是石英晶体,如果不慎掉落或受不明撞击,石英晶体易断裂破损,所以晶振的放置远离板边,靠近MCU的位置布局。

晶振紧邻主控芯片(如MCU、FPGA)时钟输入引脚,最大走线长度≤10mm。

远离高速信号线(如DDR、USB差分对),间距≥3倍线宽,避免串扰。

走线长度与宽度:时钟走线应尽量短且直,线宽适当加粗以降低阻抗,但需平衡与发热源的距离。对于高频信号(如10 MHz以上),走线长度需控制在500 mil以内。

包地屏蔽:时钟走线建议包地处理,用地线包围信号线,并每隔一段距离(如100 mil)打过孔连接地层,增强抗干扰能力。

避免交叉干扰:晶振输出信号线不得跨越电源层或敏感信号线,若必须跨越需垂直走线并保持间距。

去耦与滤波

电源去耦:晶振电源引脚需加去耦电容(如100nF陶瓷电容),靠近引脚放置,以滤除高频噪声。4 对于有源晶振,电源线可串联小电阻(47~100 Ω)限流。

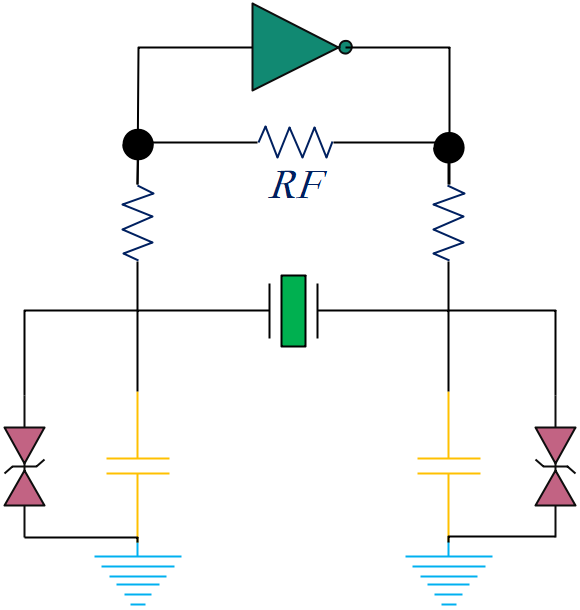

负载电容配置:无源晶振需外接负载电容(Cg和Cd),其值需满足:负载电容CL = (Cg × Cd) / (Cg + Cd) + 杂散电容(Cs)。杂散电容通常取2~5 pF,设计时需根据晶振规格调整Cg和Cd值(例如CL=15 pF时,可取Cg=Cd=24 pF)

耦合电容应尽量靠近晶振的电源管脚,如果多个耦合电容,按照电源流入方向,依次容值从大到小摆放;晶振则要尽量的靠近MCU

其他说明

高独立:尽可能保证晶振周围的没有其他元件。防止器件之间的互相干扰,影响时钟和其他信号的质量。晶振周围 1mm 禁布器件,0.5mm 禁布过孔走线,所有晶振下不打过孔(包括地过孔)。当心晶振和地的走线。

尽可能将其它时钟线路与频繁切换的信号线路布置在远离晶振连接的位置。

外壳要接地:晶振的外壳必须要接地,除了防止晶振向外辐射,也可以屏蔽外来的干扰。

-

晶振

+关注

关注

35文章

3638浏览量

73818 -

PCB设计

+关注

关注

396文章

4939浏览量

95780 -

时钟频率

+关注

关注

0文章

74浏览量

21176

原文标题:炬烜知识汇|晶振在PCB设计中的要点

文章出处:【微信号:炬烜科技,微信公众号:炬烜科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

晶振不起振也可能是PCB设计的锅

石英晶振的设计要点有哪些

晶振电源电路及PCB设计要点资料下载

浅谈晶振在PCB设计中的要点

浅谈晶振在PCB设计中的要点

评论