扫描二维码获取

更多精彩

FPGA设计论坛

欢迎关注至芯科技

至芯官网:www.zxopen.com

至芯科技技术论坛:www.fpgaw.com

至芯科技淘宝网址:

https://zxopen.taobao.com

至芯科技FPGA初级课程(B站):

https://space.bilibili.com/521850676

至芯科技FPGA在线课程(腾讯课堂):

https://zxopenbj.ke.qq.com/

至芯科技-FPGA 交流群(QQ):282124839

更多资料下载欢迎注册http://www.fpgaw.com

扫码加微信回复加群

邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:如何实现FPGA的可重复性设计

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1663文章

22493浏览量

638967

原文标题:如何实现FPGA的可重复性设计

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

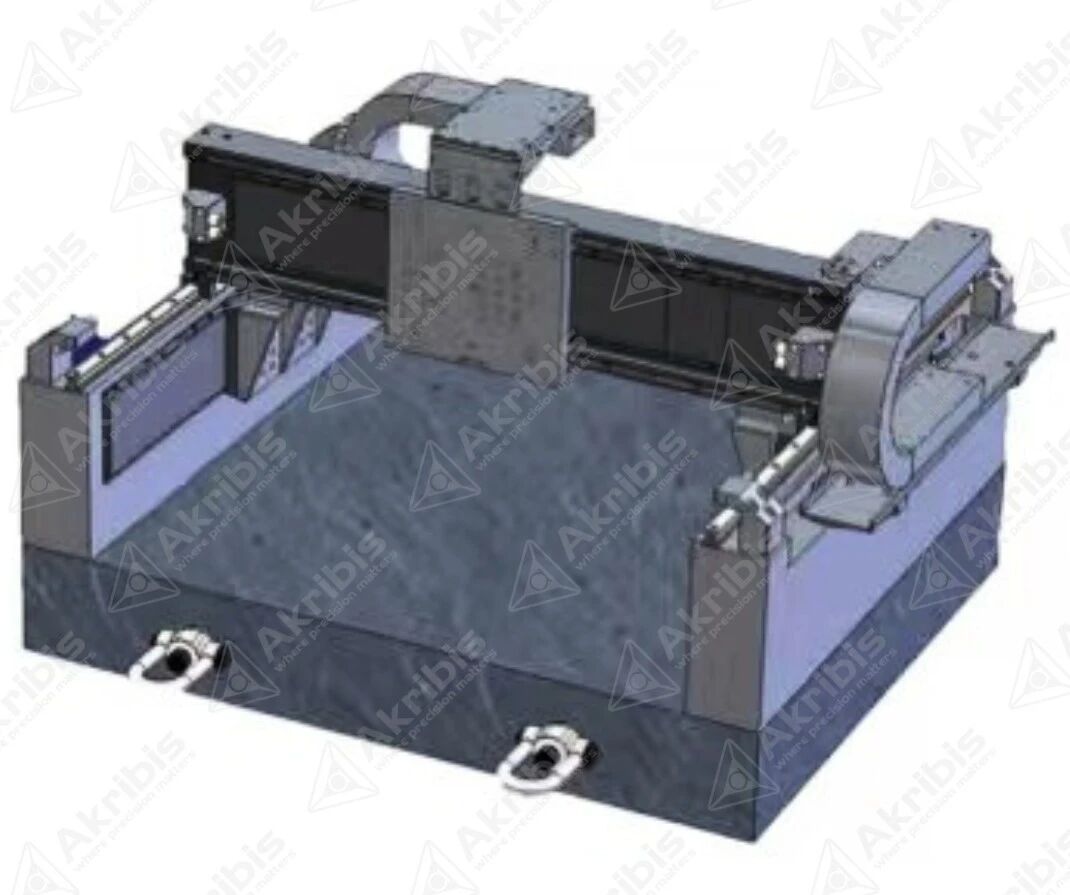

直线电机模组——精密测量设备的核心驱动方案

精密测量设备,如三坐标测量机、光学检测设备、表面轮廓仪等,是现代工业质量控制体系的核心。其测量精度、重复性与效率的不断提升,与驱动执行机构的技术革新密切相关。直线电机模组凭借无间隙传动、高定位精度

别再无效加班!IT 运维自动化脚本,砍掉90%重复工作

周一早晨,打开工单系统,23个待处理,其中一半是“软件装不上”“系统卡顿”这类重复问题。这场景你是否似曾相识?大多数IT团队已被重复性工作压垮。人手本就捉襟见肘,还要被终端重复操作、工单积压、补丁

基于BL350平台的焊接机器人智能控制与质量追溯解决方案

在汽车制造、重型机械、压力容器等高端焊接领域,对焊接质量的稳定性、工艺的可重复性以及生产过程的可追溯性提出了近乎严苛的要求。然而,传统的焊接机器人系统架构,正面临着一系列影响其智能化升级与卓越品质实现的关键瓶颈。

突破技术瓶颈!昊衡科技推出4通道同步同速光纤三维形状传感系统,实时重构更精准!

高频测量,形状传感重复性精度达1%,并在10米传感长度内实现应变解调,重复性精度稳定在±1με,为高动态三维形状监测提供可靠技术支撑。技术升级:从“交替解调”到“同

GRAS 座舱测试支架 AutoArray:PR0003 PR0004!

两款坚固耐用的六传声器阵列专为实现车内声学测量的高精度和可重复性而设计。PR0003采用基于哈曼等车载系统公司成熟测试方法的“Cross”配置。而PR0004则遵循AES

暂态事件记录的重复触发抑制是如何实现的?

暂态事件记录的重复触发抑制通过 触发抑制时间(死区时间) 、 迟滞阈值 、 事件分级独立设置 和 事件验证机制 四大核心技术实现,确保同一暂态事件不被重复记录,同时保证真实事件完整捕捉。 一、核心

中科银河芯全新推出GXC400 RTD至数字输出转换器

RTD(热阻式温度检测器)基于材料电阻随温度“灵敏变化”的特性实现对温度的测量。其中应用最广泛的铂电阻RTD(PT-RTD),测温范围最高可超过800℃,并具备良好的精度、可重复性与线

AMD利用可重构FPGA设备Moku实现自定义激光探测解决方案

摘要本文介绍了AdvancedMicroDevices,AMD公司如何基于可重构FPGA设备自定义激光探测解决方案,替代传统的仪器配置,通过灵活且可定制的FPGA设备Moku提供更高效

5大理由:声学工程师为何依赖 GRAS 40PO 系列实现稳定、可扩展的测试

当声学验证需要兼顾可重复性与测量速度时,测量链中任何微小的低效环节都可能产生叠加影响。无论您正在验证移动设备、音频电子设备还是声学传感器,传声器都不应成为变量因素。GRAS40PO-L和40PO-H

椭偏仪在精密薄膜中的应用:基于单驱动变角结构的高重复性精度控制系统

椭偏测试技术具有非接触、高灵敏、无样品破坏优势,广义椭偏仪因可测各向同性与异性样品成研究热点,但需变角结构实现多角度测量。当前立式椭偏仪存在双电机配合难或装配精度高问题,卧式椭偏仪光路不易对准,且

精密平台中重复精度的影响因素有哪些

什么是重复定位精度? 在精密运动平台中,重复定位精度(或重复性)是指运动台多次运动到同一名义位置时,与实际位置偏差的某个统计量,根据不同的测试标准会有不同的统计计算方法,例如峰谷值、2σ、3

滑台模组如何实现电子制造精密加工?

滑台模组是一种线性运动装置,用于实现高精度、高重复性的直线位移,由导轨、滑块、驱动(如伺服电机、步进电机)和传动(滚珠丝杆、同步带)组成。广泛应用于自动化设备、数控机床、3D打印等领域。

Python脚本实现运维工作自动化案例

还在为重复性运维工作而烦恼?每天被各种告警、监控、部署搞得焦头烂额?作为一名有10年经验的运维老司机,今天分享5个超实用的Python自动化脚本,让你的运维工作效率提升300%!这些都是我在生产环境中实际使用的案例,代码简洁高效,拿来即用!

GRAS 发布全新座舱测试支架 AutoArray:PR0003 &amp; PR0004!

坚固耐用的六传声器阵列专为实现车内声学测量的高精度和可重复性而设计。PR0003采用基于哈曼等车载系统公司成熟测试方法的“Cross”配置。而PR0004则遵循AESTC-

SAP实施专家解答:如何用DeepSeek-R1实现需求沟通效率倍增

工博科技分享AI工具链在IT项目中的深度应用:通过DeepSeek-R1实现智能会议记录结构化(2小时会议5分钟生成决策表)和精准多语言文档翻译(错误率降低14%),帮助IT团队将重复性工作耗时减少

如何实现FPGA的可重复性设计

如何实现FPGA的可重复性设计

评论