HMC987LP5E 1:9扇出缓冲器设计用于低噪声时钟分配。该器件旨在生成上升/下降时间小于100 ps的相对方波输出。HMC987LP5E具有低偏斜和抖动输出以及快速上升/下降时间,从而可以控制混频器、ADC/DAC或SERDES器件等下游电路的低噪声开关功能。这些应用中,当时钟网络带宽足够宽并允许方波切换时,噪底尤为重要。HMC987LP5E的输出以2 GHz驱动,其噪底为-166 dBc/Hz,相当于0.6 asec/rtHz抖动密度,或8 GHz带宽内的50 fs。

输入级可单端或差分驱动,可采用多种信号格式(CML、LVDS、LVPECL或CMOS),以及交流或直流耦合。输入级同样具有可调输入阻抗。该器件集成带有可调摆幅/功率电平的8路LVPECL输出和1路CML输出,步进为3 dB。

各输出级可以通过硬件控制引脚或串行端口接口的控制使能或禁用,以便在不需要时节省电能。

应用

SONET、光纤通道、GigE时钟分配

ADC/DAC时钟分配

低偏斜和抖动时钟或数据扇出

无线/有线通信

电平转换

高性能仪器仪表

医疗成像

单端至差分转换

审核编辑 :李倩

-

缓冲器

+关注

关注

6文章

2215浏览量

48662 -

时钟

+关注

关注

11文章

1953浏览量

134532 -

低噪声

+关注

关注

0文章

460浏览量

24453

原文标题:HMC987 3.3V低噪声1:9扇出缓冲器,DC - 8 GHz

文章出处:【微信号:兆亿微波,微信公众号:兆亿微波】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

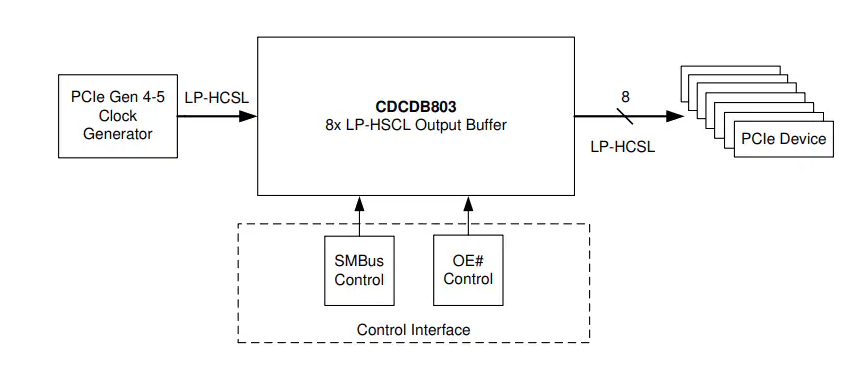

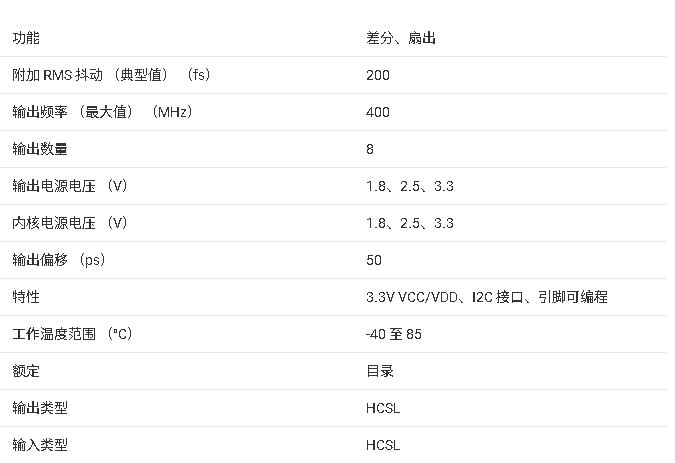

Texas Instruments CDCDB803用于PCIe®第1代至第5代的8输出时钟缓冲器数据手册

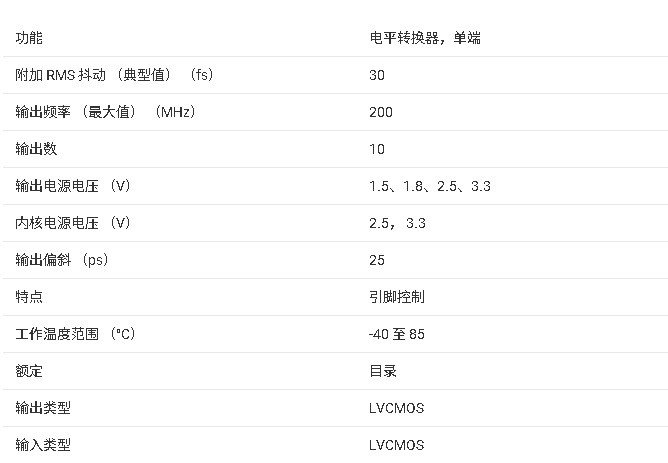

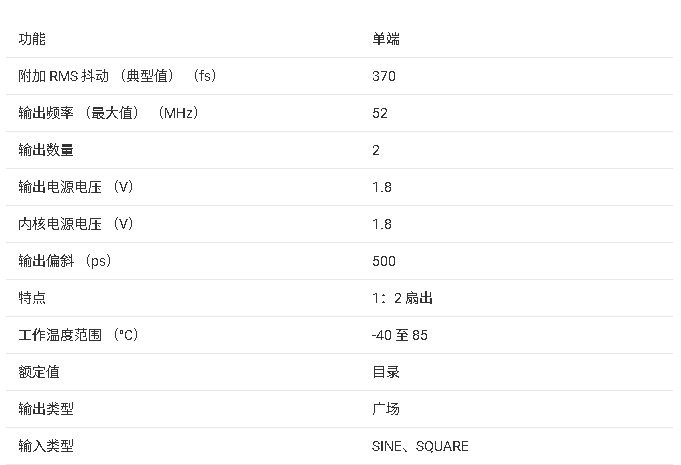

LMK00101 超低抖动LVCMOS扇出缓冲器/电平转换器技术手册

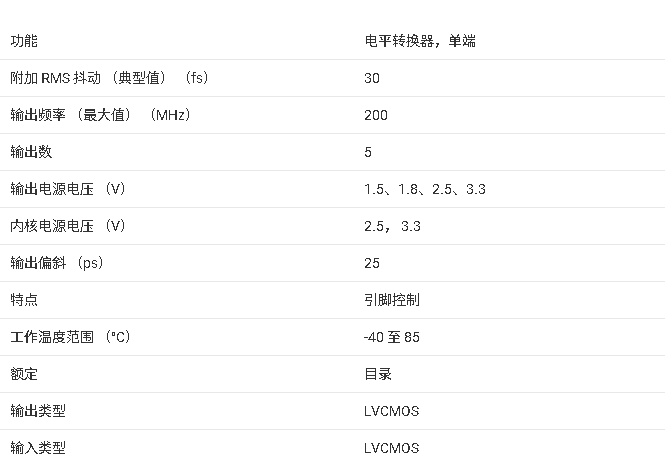

LMK00105 超低抖动LVCMOS扇出缓冲器与电平转换器技术文档总结

CDCUN1208LP 2:8扇出缓冲器技术文档总结

HMC1113LP5E GaAs MMIC I/Q下变频器技术手册

HMC987LP5E 1:9扇出缓冲器设计用于低噪声时钟分配

HMC987LP5E 1:9扇出缓冲器设计用于低噪声时钟分配

评论