该CDCUN1208LP是一个2:8扇出缓冲器,具有宽工作电源范围、两个通用差分/单端输入以及带边沿速率控制的通用输出(HCSL、LVDS或LVCMOS)。时钟缓冲器支持 PCIe Gen1、Gen2 和 Gen3。其中一个器件输入包括一个分频器,提供 /1、/2、/4 或 /8 的分频值。该CDCUN1208LP采用 32 引脚 QFN 封装,可减少解决方案尺寸。该设备灵活且易于使用。某些引脚的状态决定了上电时的设备配置。或者,CDCUN1208LP提供SPI/I^2^主机处理器控制设备设置的 C 端口。该CDCUN1208LP具有出色的附加抖动性能和低功耗。输出部分包括四个专用电源引脚,支持来自不同电源域的输出端口运行。这提供了在不同 LVCMOS 电平上切换的器件时钟的能力,而无需外部逻辑电平转换电路。

*附件:cdcun1208lp.pdf

特性

- 支持 PCIe Gen1、Gen2、Gen3

- 配置选项(通过引脚或SPI/I^2^C):

- 输入类型(HCSL、LVDS、LVCMOS)

- 输出类型(HCSL、LVDS、LVCMOS)

- 信号边沿速率(慢、中、快)

- 时钟输入分频值 (/1、/2、/4、/8) – 仅 IN2

- 低功耗和电源管理功能,包括1.8V工作和输出使能控制

- 集成稳压器可改善 PSNR

- 优异的加法抖动性能

- 200 fs RMS(10 kHz 至 20 MHz),100 MHz 时的

LVDS - 160 fs RMS(10 kHz 至 20 MHz),100 MHz 时的

HCSL

- 200 fs RMS(10 kHz 至 20 MHz),100 MHz 时的

- 最大工作频率:

- 差分模式:高达 400 MHz

- LVCMOS 模式:高达 250 MHz

- ESD 保护超过 2 kV HBM、500 V CDM

- 工业温度范围(–40°C 至 85°C)

- 宽电源范围(1.8 V、2.5 V 或 3.3 V)

参数

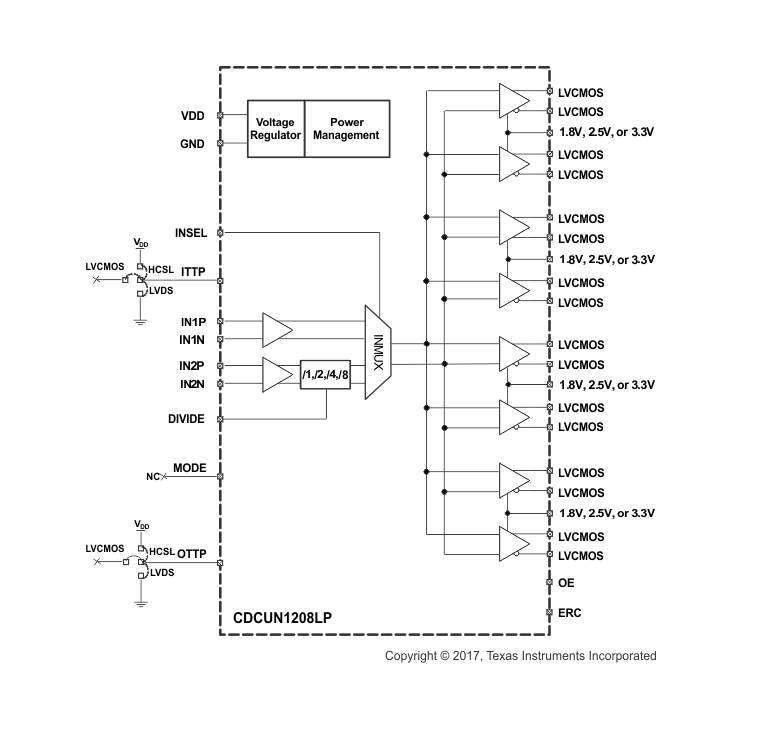

方框图

1. 产品概述

CDCUN1208LP是德州仪器(TI)推出的一款低功耗2:8扇出缓冲器,支持PCIe Gen1/2/3协议,具有通用输入(HCSL/LVDS/LVCMOS)和输出配置。核心特性包括:

- 输入灵活性:2个通用差分/单端输入,支持HCSL、LVDS、LVCMOS信号类型,输入频率范围0.008-400 MHz(差分模式)或0.008-250 MHz(单端模式)。

- 输出配置:8路输出可独立配置为HCSL、LVDS或LVCMOS,支持边缘速率控制(慢/中/快),输出频率最高400 MHz(差分)或250 MHz(LVCMOS)。

- 低功耗设计:1.8V/2.5V/3.3V宽电源范围,集成电压调节器优化电源噪声抑制(PSNR)。

- 低抖动性能:LVDS模式下100 MHz时附加抖动仅200 fs RMS,HCSL模式下160 fs RMS。

2. 关键特性

- 时钟分频:IN2输入支持/1、/2、/4、/8分频(通过引脚或SPI/I2C配置)。

- 智能输入多路复用器:支持自动切换优先级(IN1为默认主输入),切换时提供无毛刺过渡。

- 输出控制:支持全局使能(OE引脚)或通过SPI/I2C独立控制每路输出。

- 工业级温度范围:-40°C至85°C。

3. 应用场景

4. 封装与引脚

- 封装:32引脚VQFN(5mm×5mm),带散热焊盘。

- 引脚功能:

- 核心电源(VDD,引脚5)需优先或与输出电源(VDDOx)同步上电。

- 配置引脚(如MODE、ERC、OTTP)决定工作模式(引脚控制或SPI/I2C主机控制)。

5. 技术参数

- 电源要求:VDD与VDDOx可独立供电(1.8V/2.5V/3.3V),支持混合电压输出。

- 时序特性:输出使能至稳定时钟时间20 µs(LVDS),传播延迟3.8-6.8 ns(取决于输出模式)。

- ESD保护:超过2 kV HBM、500 V CDM。

6. 设计支持

7. 文档与支持

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

缓冲器

+关注

关注

6文章

2236浏览量

49050 -

封装

+关注

关注

128文章

9333浏览量

149048 -

端口

+关注

关注

4文章

1110浏览量

34049 -

PCIe

+关注

关注

16文章

1479浏览量

88929 -

LVCMOS

+关注

关注

1文章

142浏览量

12036

发布评论请先 登录

相关推荐

热点推荐

SN65LVEP11 2.5 V/3.3V PECL/ECL 1:2扇出缓冲器数据表

电子发烧友网站提供《SN65LVEP11 2.5 V/3.3V PECL/ECL 1:2扇出缓冲器数据表.pdf》资料免费下载

发表于 07-08 11:37

•0次下载

SN65LVEL11 3.3V ECL 1:2扇出缓冲器数据表

电子发烧友网站提供《SN65LVEL11 3.3V ECL 1:2扇出缓冲器数据表.pdf》资料免费下载

发表于 07-08 11:52

•0次下载

SN65EL11 5v PECL/ECL 1:2扇出缓冲器数据表

电子发烧友网站提供《SN65EL11 5v PECL/ECL 1:2扇出缓冲器数据表.pdf》资料免费下载

发表于 07-10 11:22

•0次下载

具有通用输入和输出的CDCUN1208LP 400MHz低功耗2:8扇出缓冲器数据表

电子发烧友网站提供《具有通用输入和输出的CDCUN1208LP 400MHz低功耗2:8扇出缓冲器数据表.pdf》资料免费下载

发表于 08-20 09:18

•0次下载

CDCLVD1208 2:8低附加抖动LVDS缓冲器技术文档总结

CDCLVD1208时钟缓冲器分配两个可选时钟输入(IN0和IN1)之一 8对差分LVDS时钟输出(OUT0至OUT7),时钟偏移最小 分配。该CDCLVD1208可以接受两个时钟源进

深入解析SN65EL11:5V PECL/ECL 1:2扇出缓冲器

深入解析SN65EL11:5V PECL/ECL 1:2扇出缓冲器 在电子电路设计领域,信号的分配和处理至关重要。今天我们要探讨的是德州仪器(TI)推出的SN65EL11,一款高性能的5V PECL

3.3V低噪声1:9扇出缓冲器ADH987S的设计与应用

3.3V低噪声1:9扇出缓冲器ADH987S的设计与应用 在电子设计领域,缓冲器是至关重要的组件,它能有效增强信号并分配到多个输出端。今天,我们就来深入探讨Analog Devices公司推出

HMC720LP3E:高速1:2扇出缓冲器的卓越之选

HMC720LP3E:高速1:2扇出缓冲器的卓越之选 在高速逻辑电路设计领域,对高性能、高速度的组件需求日益增长。HMC720LP3E作为一

高速利器——HMC724LC3 1:2扇出缓冲器深度解析

高速利器——HMC724LC3 1:2扇出缓冲器深度解析 在当今高速数据传输的时代,对于高速、稳定的信号处理元件需求日益增长。而HMC724LC3 1:2

高速逻辑之HMC850LC3:1:2扇出缓冲器的卓越表现

高速逻辑之HMC850LC3:1:2扇出缓冲器的卓越表现 在高速数据传输和时钟管理领域,一款性能出色的扇出缓冲器至关重要。今天,我们就来深入

CDCUN1208LP 2:8扇出缓冲器技术文档总结

CDCUN1208LP 2:8扇出缓冲器技术文档总结

评论