由于测试芯片的复杂性和覆盖范围的原因,单个小芯片对复合材料成品率下降的影响正在为晶圆测试带来新的性能要求。从测试的角度来看,使小芯片成为主流技术取决于确保以合理的测试成本获得“足够好的模具”。

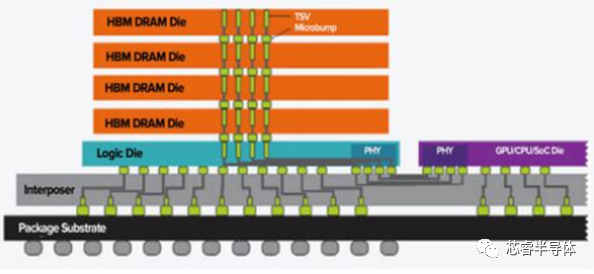

晶圆级测试在小芯片制造过程中扮演着至关重要的角色。以HBM(高带宽内存)为例,它可以及早发现有缺陷的DRAM和逻辑芯片,以便可以在复杂而昂贵的堆叠阶段之前将其删除。堆叠后晶圆的进一步测试可确保完成的堆叠在切割成独立组件之前具有完整的功能。理想情况下,每个DRAM芯片在堆叠之前都应进行已知良好芯片(KGD)测试,以独立验证其性能。但这在经济上通常是不可行的。在某些时候,测试成本超过了系统完成后增加的价值。 因此,需要一种平衡测试成本和未做芯片不良率检测的测试策略,以将异构集成引入大批量生产。

得益于MEMS探针卡技术的创新,FormFactor的产品可以帮助客户实现全流程的KGD测试(例如支持45μm栅格阵列间距微凸点测试的Altius探针卡,用于高速HBM和Interposer插入连接器的良品率验证),并且可以接受有限的测试成本(例如SmartMatrix探针卡,通过同时测试300mm晶圆上的数千个芯片,大大降低了每个芯片的测试成本)。最终,我们在小型芯片制造过程的每个阶段获得有关产品性能和成品率的更多信息,从而帮助客户降低总体制造成本。

审核编辑 :李倩

-

晶圆

+关注

关注

53文章

5344浏览量

131687 -

芯片制造

+关注

关注

11文章

711浏览量

30326

原文标题:探针台测试,从晶圆测试角度来看,使小芯片(Chiplet)成为主流技术所面临的最大挑战是什么?

文章出处:【微信号:gh_064d56de9e11,微信公众号:芯睿半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Chiplet核心挑战破解之道:瑞沃微先进封装技术新思路

Chiplet封装设计中的信号与电源完整性挑战

开发无线通信系统所面临的设计挑战

小芯片(Chiplet)技术的商业化:3大支柱协同与数据驱动的全链条解析

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

AI 时代来袭,手机芯片面临哪些新挑战?

Chiplet与先进封装设计中EDA工具面临的挑战

使小芯片(Chiplet)成为主流技术所面临的最大挑战是什么?

使小芯片(Chiplet)成为主流技术所面临的最大挑战是什么?

评论