生成式 AI、Chiplet、多Die 架构、具身智能……新一轮计算浪潮正在深刻改变芯片设计方式,也对底层 IP 技术提出了前所未有的挑战。

在近期举办的新思科技 IP 技术日活动上,我们特别采访了新思科技 IP 事业部应用工程高级总监王迎春和新思科技资深产品市场经理 Mehak Kalra,围绕高性能接口 IP、Chiplet 生态、车规级 IP 以及 EDA 与 IP 的深度协同,分享了他们对行业趋势与技术演进的洞察。

算力爆发时代,IP设计面临哪些新挑战?

生成式 AI 正推动计算、存储、互联同步扩展。PCIe、CXL、UCIe、HBM、高速以太网等接口标准快速演进,芯片设计正在从“单芯片”走向分布式、多Die、系统级协同。

IP 不再只是“接口实现”,而是系统性能、功耗与可靠性的关键基础。

Chiplet 成为主流,难点在哪?

Chiplet 设计带来了更高的灵活性,也显著提升了系统复杂度:架构划分、Die-to-Die 互联、封装、可靠性、信号完整性……新思科技通过 EDA + IP 协同的一站式方案,帮助客户把复杂性前移并系统化解决。

车规级与具身智能,对 IP 提出了哪些新要求?

在智能汽车与具身智能场景中,功能安全、可靠性与安全性成为“入场券”。

新思科技 IP 在设计之初就原生支持 ISO 26262、ISO 21434 等国际标准,并提供完整的合规证明,帮助客户显著缩短认证周期。

面向未来:IP 决定的不仅是芯片性能,更是系统能力

从 EDA 到 IP,从数字孪生到系统级验证,新思科技正在为下一代 边缘智能、工业元宇宙与具身智能构建可扩展、可验证、可持续演进的技术底座。

-

AI

+关注

关注

91文章

41057浏览量

302561 -

新思科技

+关注

关注

5文章

979浏览量

52986 -

算力

+关注

关注

2文章

1669浏览量

16832

原文标题:从生成式AI到具身智能,IP设计正在发生哪些关键变化

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AI算力大爆发,传统光纤“跑不动”了

AI算力时代的热挑战:宏展高发热大负载Walk-in试验箱的技术应对

国产算力出海元年开启

算力爆发下的刚需赛道:AI服务器高频高速连接器需求迎爆发式增长

赋能电源芯片国产替代,智芯谷助力AI算力稳定前行

从云端集中到边缘分布:边缘智算如何重塑算力网络布局

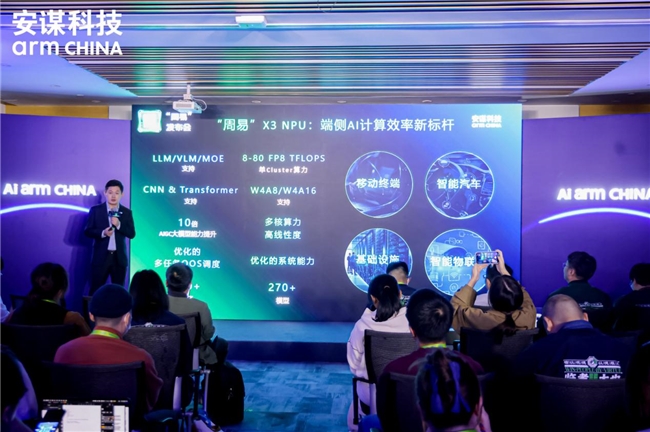

安谋发布“周易”X3 NPU,破局AI算力,智绘未来蓝图

智算IP广域网助力算力互联网建设进入快车道

热”芯”冷“调”高算力时代的“降温”革命 | 氮化硼散热材料

算力爆发时代IP设计面临哪些新挑战

算力爆发时代IP设计面临哪些新挑战

评论