近几年中,芯片特征尺寸已接近物理极限,而先进封装技术成为延续摩尔定律的重要途径。一系列新型封装技术出现在人们视野之中。而其中扇出型晶圆级封装(FOWLP)被寄予厚望,它将为下一代紧凑型、高性能的电子设备提供坚实而有力的支持。

扇出型晶圆级封装技术无需使用中介层或硅通孔(TSV),即可实现外形尺寸更小芯片的封装异构集成。在嵌入每个裸片时,裸片间的空隙会有一个额外的I/O连接点,在提高I/O数量的同时,也会使得硅的利用率有所提升。在扇出型晶圆级封装技术的加持下,具有成千上万I/O点的半导体器件可通过两到五微米间隔线实现无缝连接,从而使互连密度最大化。

工艺步骤

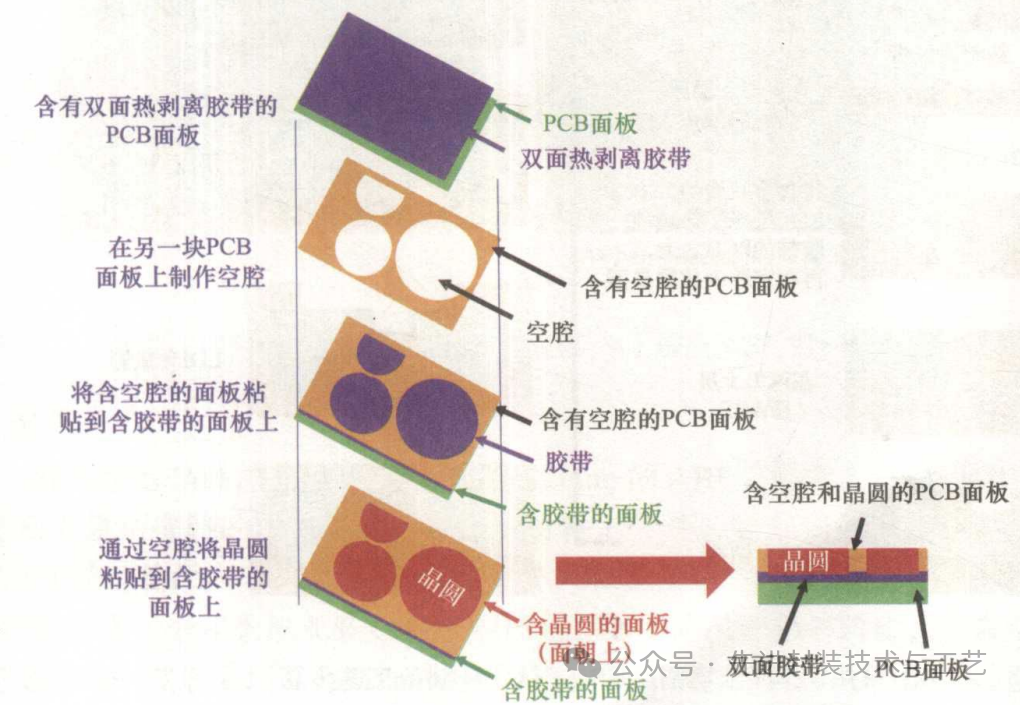

从晶圆代工厂(Foundry)生产完成的晶圆(Wafer)经过测试后进入生产线类似传统封装,扇出型封装第一步也需要将来料晶圆切割成为裸晶。

扇出型封装的主要特点是将切割后的裸晶组合成为重构晶圆,与来料晶圆相比,重构晶圆上裸晶之间的距离相对更大,因此方便构造单位面积更大,输入输出(I/O)更多的芯片成品。

塑封、去除载片

完成重构晶圆的贴片后,对重构晶圆进行塑封以固定和保护裸晶。然后将重构晶圆载片移除,从而将裸晶对外的输入输出接口(I/O)露出。

制作再布线层

为了将裸晶上的接口(I/O)引出至方便焊接的位置,在晶圆上通过金属布线工艺制作再布线层(RDL)。

晶圆减薄

为使芯片成品更轻薄,对晶圆进行减薄加工。

植球

在再布线层(RDL)所连接的金属焊盘上进行植球,方便后续芯片在印刷电路板(PCB)上的焊接。

晶圆切割、芯片成品

最后将重构晶圆进行切割,以得到独立的芯片。

芯片制造工艺的发展不会停滞,长电科技在先进封测领域深耕多年,拥有深厚的技术积累和坚实的平台。无论是现在还是未来,长电科技都将精准把握市场趋势、紧扣科技脉搏,为推动芯片成品制造技术的突破与发展尽一份力量。

审核编辑:刘清

-

半导体

+关注

关注

339文章

31438浏览量

267425 -

晶圆

+关注

关注

53文章

5475浏览量

132886 -

FOWLP

+关注

关注

1文章

18浏览量

10209

原文标题:硬核科普 | 一文看懂扇出型晶圆级封装(FOWLP)

文章出处:【微信号:gh_0837f8870e15,微信公众号:长电科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

晶圆级MOSFET的直接漏极设计

扇出型封装材料:技术突破与市场扩张的双重奏

什么是晶圆级扇入封装技术

科普一下扇出型晶圆级封装(FOWLP)

科普一下扇出型晶圆级封装(FOWLP)

评论