01简介

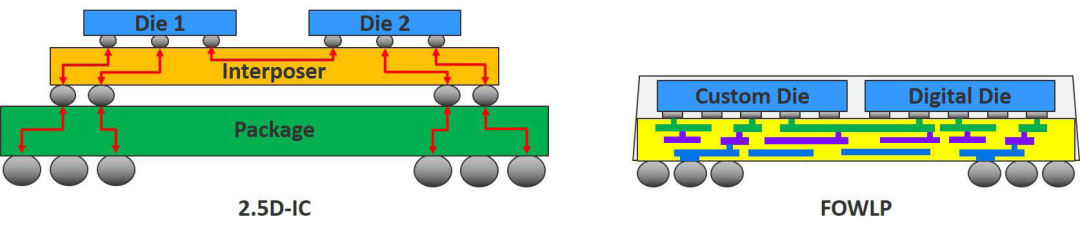

高密度先进封装 (HDAP) 设计如今已成为真实的产品。过去十年里,HDAP 技术的所有变化形式都承诺通过集成使用不同技术节点构建的多个集成电路 (IC) 芯片(异构集成),来获得改进的外形参数和功能。下图显示了两种流行的 HDAP 技术:2.5D(中介层)和扇出型晶圆级封装 (FOWLP) 设计。

图:基于中介层的 2.5D IC 和 FOWLP 设计是最常用的 HDAP 技术

同任何电子产品一样,HDAP 设计也需要广泛的验证,确保它们能够按预期运行,并且能够可靠地制造出足够的数量以满足市场需求。但事实证明,自动化 HDAP 验证对电子设计自动化 (EDA) 行业来说颇具挑战,因为它需要结合 IC 和封装验证的元素。在确定问题、建议或制定解决方案方面,人们投入了大量的时间和研究。类似于集成电路工艺设计套件 (PDK) 的合格装配设计套件 (ADK) 的一般概念,至少已在有限的程度上变为现实。HDAP 的装配级版图和电路图比较 (LVS) 验证,现在至少有了一种 EDA 解决方案。HDAP 的布线后仿真(模拟)和布线后 STA(数字)流程的价值,更是众所周知。人们认识到,需要一种方法来生成 HDAP 系统级连接,同时兼顾芯片、封装和芯片/封装接口寄生效应。

在推动 HDAP 成为一个可行的市场选择方面,虽然上述所有工作都很珍贵,但现在似乎有必要评估这一过程的成熟度和范围,并展望其未来的发展。为此,我们将聚焦其中一个目标:封装 LVS 验证。

02HDAP 物理验证成熟度

随着 HDAP 技术的日益发展和成熟,设计人员需要 EDA 工具公司、晶圆代工厂和封测代工厂 (OSAT) 提供合格、可靠的 EDA 设计和验证流程。完成设计后,第一步自然是 HDAP 的物理验证。HDAP 设计包含通过封装连接的多个异构芯片。虽然 HDAP 中每个芯片自身的功能都已经过验证,但 HDAP 设计人员如何确保整个 HDAP 在制造后仍能按预期运行呢?

这个问题代表了一种不连续性,也是传统封装设计中不存在的全新挑战。在过去,单凭肉眼检查就足以确认芯片是否正确连接到封装,继而连接到最终产品,如印刷电路板 (PCB)。对 HDAP 设计而言,情况并非如此。

尽管 EDA 公司、晶圆代工厂/OSAT 和 HDAP 设计公司已合作多年,共同构建 HDAP 物理验证流程,但这个流程还远远谈不上 “成熟”。各方需要学习的地方还很多。

03验证数据完整性

下面我们来考虑一下面向 HDAP 设计的版图和电路图比较 (LVS) 验证。除非版图设计中内置的几何形状实现了原始原理图/设计意图所需的连接,否则片上系统 (SoC) 就无法获批投入制造。LVS 验证是 SoC 领域一个成熟、完善的自动化流程。用于 SoC 的 EDA LVS 工具需要一组一致的基本输入:

■ 版图数据库(格式可以是 GDSII、OASIS 或 LEF/DEF)

■源网表(格式可以是 SPICE 或 Verilog)

■ LVS 规则集(基于 EDA 公司专有语法的格式)

设计公司、晶圆代工厂和 EDA 供应商都理解并同意,如果没有某种形式的上述三种输入,SoC LVS 验证便无从谈起。LVS 规则集通常由晶圆代工厂创建并提供,独立于任何单一 SoC 设计,版图数据库和源网表则由设计公司创建。

回到 HDAP LVS 验证,我们马上就能发现重要的差异。最明显且最关键的一点是,设计公司、晶圆代工厂/OSAT 和 EDA 公司在 HDAP LVS 流程所需的输入集上没有达成一致。存在这种脱节的原因有三个:所有权、数据可用性和设计依赖性。

所有权

由于 HDAP 仍是一种新兴技术,HDAP 验证的责任在不同公司往往由不同的团队承担。例如,一些设计公司倾向于将 2.5D 设计和验证视为 “SoC 为主,封装为辅” 的活动。这类设计的设计和验证责任通常落到了 SoC 和/或计算机辅助设计 (CAD) 团队的身上,他们在 SoC 验证要求和格式方面有着丰富的经验。而对于 FOWLP 封装,设计和验证被视为 “SoC 为辅,封装为主” 的活动,因此该责任通常由不太熟悉 SoC 验证要求和格式的封装团队承担。保持这种多样性的底线是,晶圆代工厂/OSAT 和 EDA 公司在支持采用不同方法且具有不同要求的 HDAP 设计公司时,必须做好灵活应对的准备。

数据可用性

为了实现对整个 HDAP 的 LVS 验证,所有组件的所有数据都必须可用。例如,FOWLP 设计人员需要 die1 版图设计数据库、die2 版图设计数据库、FOWLP 设计数据库,以及某种形式的 FOWLP 系统源网表。现在,如果 FOWLP 设计数据库(由封装团队负责)已准备就绪,而芯片数据库(由 SoC 团队负责)仍在开发中,将会出现什么情况?对 FOWLP 设计人员来说,如果等到所有芯片构建完毕并经过验证再运行 FOWLP LVS,结果发现 FOWLP 设计数据库中充斥了短路、开路和其他错误,将是完全行不通的。设计人员必须在完成完整的 LVS 验证之前的早期验证期间,采取一些做法来修复明显的问题。为了实现和支持这种早期验证,EDA 公司必须提供一种自动化 HDAP LVS 检查方法,并且能够在尚未取得所有最终组件的情况下运行。

设计依赖性

在 SoC LVS 验证中,LVS 规则集仅依赖于 SoC 技术节点信息(即 GDSII 层)。但是,HDAP LVS 却增加了另一个复杂问题:芯片布局。HDAP LVS 规则集依赖于中介层、 die1、die2 等 GDSII 层,也依赖于芯片(以及 2.5D 设计的中介层)的布局位置。反过来,这些信息则高度依赖于 HDAP 设计本身。晶圆代工厂/OSAT 构建 HDAP LVS 规则集将是一个面面俱到的过程,需要考虑所有可能的芯片和中介层布局组合。尽管 “一个中介层上两个芯片” 的设计在过去是可能的,但随着 HDAP 中的裸片和基底数量的增加,很快就变得不切实际了。

04克服数据 “不完整性”

因此,我们认识到,与已经存在了几十年的 SoC 验证流程相比,设计端的 HDAP 验证流程还远远不够成熟。这导致每个设计公司(以及潜在的每个 HDAP 设计周期)都可能具有不同类型的验证数据。这种情况下,EDA 公司为 HDAP 验证强制执行某一组数据要求是不切实际的。相反,EDA 公司必须非常灵活,从某种意义上说,应始终能够利用可获取的数据实现某种类型的 HDAP LVS 验证。下面我们来探讨一下,不同情况下的不同流程中的 LVS 验证可能是什么样子。

不含原理图/设计意图的封装/中介层连接检查

采用标准格式的 “源网表” 在封装领域是个相对较新的概念。传统上,封装设计人员使用手动电子表格来规划从裸片到封装再到印刷电路板 (PCB) 上的外部 I/O 的连接。尽管在 HDAP 验证中应用这类方法非常困难,但一些设计人员出于不同的原因(传统、管脚数目太少等)仍在使用电子表格。不用说,根据设计公司的旧有方法,这些电子表格可能有不同的格式和组织形式,所以 EDA 公司很难支持所有可能的电子表格。

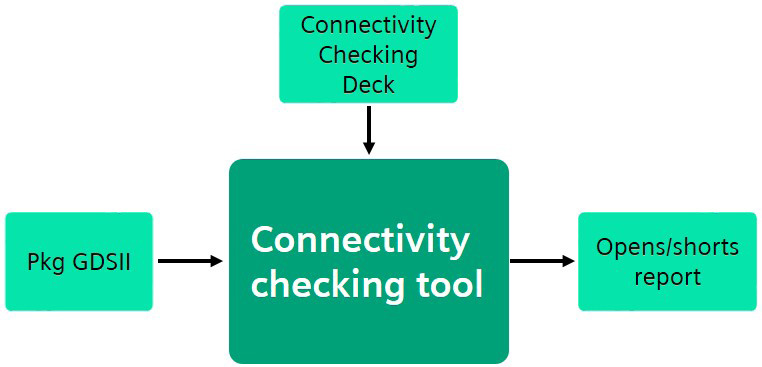

好吧,如果各种旧式电子表格不可用,设计人员还有封装设计数据库。难道就没有什么简单的开路/短路检查办法吗?事实上,可能真有。鉴于设计人员拥有的数据量(仅限于封装设计数据库),EDA 工具可以使用一种仍对他们有用的简单方法:

■ 如果封装设计数据库中的两个形状具有相同的文本标签,但在物理上是断开连接的,则应报告为 “开路”

■如果封装设计数据库中的两个形状具有不同的文本标签,但在物理上是相连接的,则应报告为 “短路”

尽管这不是全面的 LVS(因为没有可比较的设计意图),但如果还没有源网表,则仍不失为一种有价值的开路/短路检查。下图显示了这种简单的开路/短路检查器的方框图。

图:不含设计意图的封装连接检查

不含裸片管脚的封装/中介层 LVS

下一个案例介绍一种更复杂的情形。验证数据现在包括封装设计数据库和源网表,这样设计人员应该能够运行真正的 LVS 验证。他们的第一个念头可能是,使用与 SoC LVS 相同的 LVS 工具和方法。但是,SoC 中的 LVS 概念依赖于 SoC 版图设计数据库和源网表中的“器件”的存在。器件可以是有源(晶体管)或无源(电阻器、电容器等)器件。由于大多数 2.5D-IC 和 FOWLP 设计不含任何器件(仅包含金属布线),所以 SoC LVS 工具并不实用,因为它们并非针对 HDAP LVS 问题。

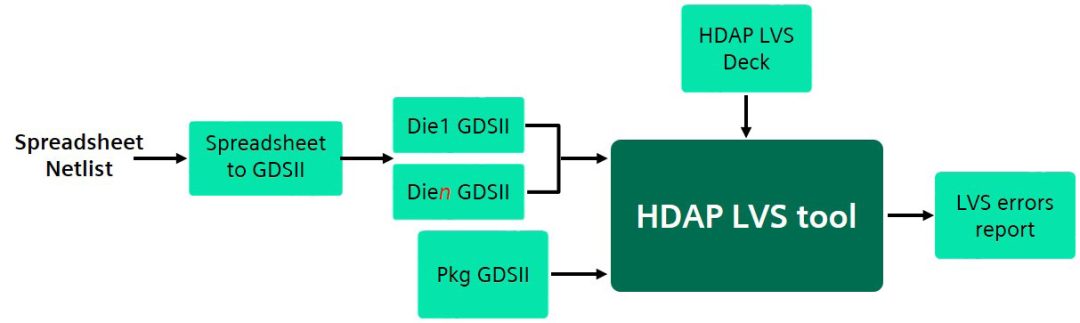

更为可行的解决方案是使用 HDAP 装配级 LVS 工具,默认情况下,这些工具会考虑封装中不存在器件的情况。但此类工具不仅需要用于装配级 LVS 的封装版图设计数据库,还需要裸片的版图设计数据库。不过,这一限制是可以解决的。装配级 LVS 工具经过强化,可以从输入电子表格网表(其中包括裸片凸块 (x,y) 坐标和管脚名称)自动生成“占位符”裸片凸块(表示裸片)。然后可以在装配设计数据库中使用此 “裸片占位符” 设计数据库。设计人员仅使用封装版图设计数据库和输入电子表格网表,就能成功运行 HDAP LVS。下图显示了不含裸片管脚的 HDAP LVS 流程的方框图。

图:不含裸片管脚的 HDAP LVS

尽管这类流程为客户提供了价值(捕获封装设计数据库中的任何物理短路/开路),但不能保证完整的装配能够成功运行。如果 HDAP 中的裸片与封装之间存在错位怎么办?

装配级 LVS/LVL

在 HDAP 中,版图与版图比较 (LVL) 验证跟 LVS 同样重要,尤其在需要旋转或缩放时(例如,将裸片收缩 10%,旋转 90°,然后布置在封装上)。设计人员必须确保,经过这类处理之后,封装凸块与裸片凸块之间仍有足够的重叠。

仅几何裸片接口

如果封装设计人员能够获得裸片接口(凸块)GDSII 层,那么除了封装 LVS 之外,他们还可以执行 LVL 验证。设计人员可以使用 EDA 工具自动将裸片布置在封装/中介层的顶面,并验证对齐情况(根据需要)。

从连接的角度来看,将裸片和封装都纳入装配级 LVS 时,通常会面临一个挑战:SoC 团队可能使用与封装团队不同的方法来命名裸片管脚/网络。SoC 设计人员的 SoC 版图设计数据库中可能有一个名为 “A” 的裸片管脚,而在系统源网表和封装设计数据库中,该管脚被称为 “A_B”。这种差异会导致许多虚假的 LVS 违规。但这一状况与此流程无关,因为 HDAP 设计人员从裸片导入的数据是 “接口物理几何形状”,而不是“接口逻辑管脚”。

也就是说,如果 SoC 设计数据库或封装设计数据库中存在额外管脚,则在使用此流程时不会捕获到该管脚。

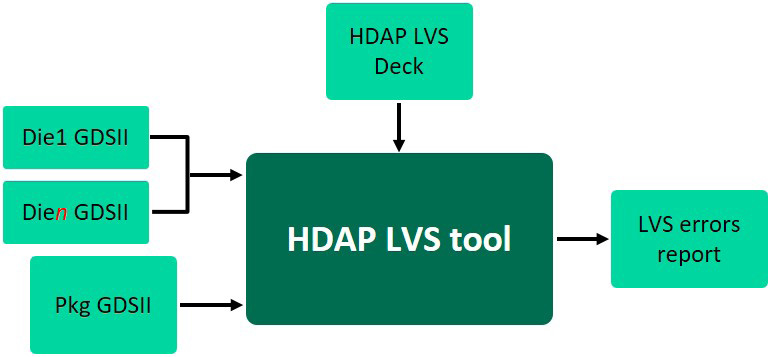

几何裸片接口 + 逻辑裸片管脚

在此流程中,来自裸片的所有接口信息(几何形状和管脚)全部可用。HDAP 设计人员可以将此流程作为 signoff 流程来运行,因为其中包括了综合验证所需的全部数据。设计人员可以验证所有可能的违规:

■ 装配级 LVS

■装配级 LVL

■额外/缺失的管脚

至于 SoC 与封装之间管脚名称/网络名称不匹配的挑战, EDA 公司提供了新颖的方法来解决这类问题,避免导致虚假的 LVS 违规。例如,HDAP 设计人员可以在输入中将这类不一致标注为豁免。下图显示了包含裸片管脚的装配级 LVS/LVL 流程。

图:装配级 LVS/LVL,包括裸片管脚

05HDAP LVS 流程

西门子提供了完整的自动化流程,可支持 HDAP 设计人员运行灵活的 HDAP LVS 验证流程,同时兼顾各种级别的数据 “不完整性” Xpedition Substrate Integrator (xSI) 工具可执行 HDAP 系统级连接关系管理和规划。xSI 工具生成系统源网表(采用电子表格格式),其中包括连接信息和裸片/封装管脚的 x,y 位置。利用 Calibre 3DSTACK 工具可实现灵活的 HDAP 物理验证(LVS 和 LVL),执行上述任意和所有三种流程。Calibre 3DSTACK HDAP 规则集可使用 xSI 工具自动生成,以兼顾 HDAP 规则集的设计依赖性。

06总结

随着 HDAP 技术逐渐成为主流,HDAP 设计人员需要来自晶圆代工厂/OSAT 和 EDA 公司的可靠设计与验证流程。但与成熟的传统 SoC 验证流程相比,目前可用的 HDAP 验证流程还远远不够成熟。在许多情况下,HDAP LVS “sign off”所需的验证数据可能并不完整。EDA 公司必须提供工具和流程来兼顾各种级别的数据可用性,同时继续支持 HDAP 设计人员执行有用且有价值的 HDAP LVS 流程。

-

芯片

+关注

关注

463文章

54429浏览量

469377 -

集成电路

+关注

关注

5464文章

12686浏览量

375729 -

LVS

+关注

关注

1文章

38浏览量

10522 -

先进封装

+关注

关注

2文章

562浏览量

1062

原文标题:一文了解 HDAP LVS/LVL 验证

文章出处:【微信号:Mentor明导,微信公众号:西门子EDA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

长电科技成功完成晶圆级射频集成无源器件工艺验证

请教:6G 确定性通信原型验证,FPGA+SDR 方案该怎么搭?

RDMA设计35:基于 SV 的验证平台

_timer_start()函数功能虽然正常,但实现是否未达预期,怎么处理?

如何验证电能质量在线监测装置的抗干扰能力?

ulog_tag_lvl_filter_set()函数无法实现按照文档说明那样实现按模块过滤,怎么解决?

如何验证硬件冗余设计的有效性?

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计

电能质量在线监测装置数据验证的流程是什么?

芯华章RISC-V敏捷验证方案再升级

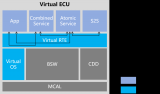

技术解读 | 光庭信息虚拟ECU技术赋能SOA化MCU软件的早期验证与集成加速

面向HDAP设计的LVS/LVL验证

面向HDAP设计的LVS/LVL验证

评论