5纳米芯片是什么概念

5纳米是指芯片的特征尺寸,特征尺寸越小,制造出来mos管就更小,成本也就更低。5纳米芯片意味着芯片更小,在单位面积内晶体管更为密切,功耗也更低。

通俗的来说。5纳米相当于头发的万分之一。一根头发大约有6万纳米,所以5纳米几乎是头发的万分之一。

5纳米芯片有多少晶体管

5纳米芯片容纳了多达153亿个晶体管。5纳米用肉眼是无法分辨出来的,在电子技术领域,技术精密等级用纳米来形容,所以纳米的数字越小,则工艺和产品就更先进。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54429浏览量

469377 -

晶体管

+关注

关注

78文章

10439浏览量

148610 -

5纳米

+关注

关注

0文章

27浏览量

5132

发布评论请先 登录

相关推荐

热点推荐

晶体管中界面层的作用和重要性

在芯片制造的宏大叙事中,人们常常津津乐道于光刻机如何雕刻纳米级线条,刻蚀机如何打通层层叠叠的沟槽。但有一个极其关键的薄膜,薄到只有几个原子层厚度,却决定着整个晶体管的生死——它就是界面层。

纳米AZO

纳米AZO 杭州九湖新材料科技有限公司 热线 壹伍贰陆捌壹捌贰伍零玖 李经理

基本信息:

特点:在Zn0中掺杂A1203简称AZ0,耐高温,导电性好,高温稳定性强,防辐射性能好。该产品是一种价格相对

发表于 03-23 13:22

揭秘芯片测试:如何验证数十亿个晶体管

微观世界的“体检”难题在一枚比指甲盖还小的芯片中,集成了数十亿甚至上百亿个晶体管,例如NVIDIA的H100GPU包含800亿个晶体管。要如何确定每一个晶体管都在正常工作?这是一个超乎

漏致势垒降低效应如何影响晶体管性能

随着智能手机、电脑等电子设备不断追求轻薄化,芯片中的晶体管尺寸已缩小至纳米级(如3nm、2nm)。但尺寸缩小的同时,一个名为“漏致势垒降低效应(DIBL)”的物理现象逐渐成为制约芯片性

三星公布首批2纳米芯片性能数据

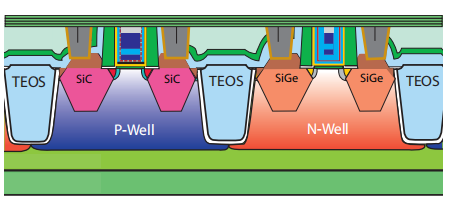

三星公布了即将推出的首代2nm芯片性能数据;据悉,2nm工艺采用的是全栅极环绕(GAA)晶体管技术,相比第二代3nm工艺,性能提升5%,功耗效率提高8%,芯片面积缩小

台积电2纳米制程试产成功,AI、5G、汽车芯片,谁将率先受益?

与现行的3nm工艺相比,台积电在2nm制程上首次采用了GAA(Gate-All-Around,环绕栅极)晶体管架构。这种全新的结构能够让晶体管电流控制更加精确,减少漏电问题,大幅提升芯片整体效能

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

。那该如何延续摩尔神话呢?

工艺创新将是其途径之一,芯片中的晶体管结构正沿着摩尔定律指出的方向一代代演进,本段加速半导体的微型化和进一步集成,以满足AI技术及高性能计算飞速发展的需求。

CMOS工艺从

发表于 09-06 10:37

铜对芯片制造中的重要作用

在指甲盖大小的芯片上,数百亿晶体管需要通过比头发丝细千倍的金属线连接。当制程进入130纳米节点时,传统铝互连已无法满足需求——而铜(Cu) 的引入,如同一场纳米级的“金属革命”,让

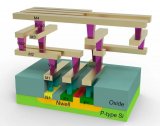

晶体管架构的演变过程

芯片制程从微米级进入2纳米时代,晶体管架构经历了从 Planar FET 到 MBCFET的四次关键演变。这不仅仅是形状的变化,更是一次次对物理极限的挑战。从平面晶体管到MBCFET,

下一代高速芯片晶体管解制造问题解决了!

晶体管的密度,同时减少了芯片的横向面积。

相比传统的FinFET和纳米片晶体管,叉片晶体管能够显著减少nFET和pFET之间的间距,从而在相

发表于 06-20 10:40

无结场效应晶体管详解

当代所有的集成电路芯片都是由PN结或肖特基势垒结所构成:双极结型晶体管(BJT)包含两个背靠背的PN 结,MOSFET也是如此。结型场效应晶体管(JFET) 垂直于沟道方向有一个 PN

半导体芯片中的互连层次

在半导体芯片中,数十亿晶体管需要通过金属互连线(Interconnect)连接成复杂电路。随着制程进入纳米级,互连线的层次化设计成为平衡性能、功耗与集成度的关键。芯片中的互连线按长度、

5纳米芯片是什么概念_5纳米芯片有多少晶体管

5纳米芯片是什么概念_5纳米芯片有多少晶体管

评论