文章来源:半导体与物理

原文作者:jjfly686

本文介绍了晶体管中界面层的作用和重要性。

在芯片制造的宏大叙事中,人们常常津津乐道于光刻机如何雕刻纳米级线条,刻蚀机如何打通层层叠叠的沟槽。但有一个极其关键的薄膜,薄到只有几个原子层厚度,却决定着整个晶体管的生死——它就是界面层。

界面层是什么?为什么需要它?

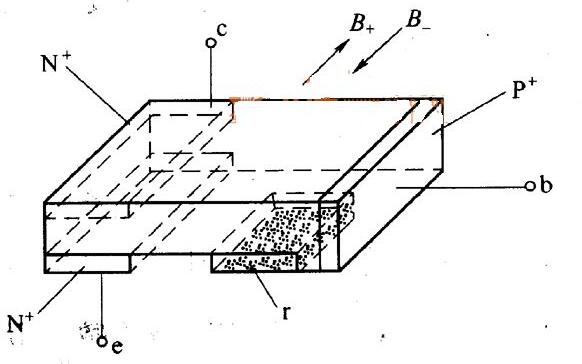

界面层,顾名思义,是位于两种不同材料交界处的那一层极薄的薄膜。在晶体管里,它特指硅衬底与栅极介质之间那道看不见的“边界墙”。

想象一下,你要把一栋高楼建在一片松软的沙滩上,直接打地基肯定不行,你得先铺一层坚硬的混凝土垫层。界面层扮演的就是这个角色——它是一层在硅衬底表面原生生长的高质量二氧化硅,厚度通常在0.5到1纳米之间,也就是大约三到五个硅原子的直径。

之所以需要这层“垫层”,是因为栅极介质(目前主流是High-K材料,比如氧化铪)如果直接沉积在硅衬底上,会带来一系列麻烦。High-K材料与硅的晶格不匹配,直接接触会产生大量的界面缺陷,这些缺陷会捕获电荷、散射载流子,严重损害晶体管的性能和可靠性。界面层就像一位和事佬,用自己完美的硅-二氧化硅界面,把这两个“性格不合”的材料平滑地连接起来。

界面层的制成:原子级“慢工出细活”

界面层的制备,是一场在原子尺度上进行的精密操作。它的核心要求就两个字:完美。

最常见的制备方法是热氧化。把清洗干净的硅片放进高温炉管里,通入高纯氧气或水蒸气,在800到1000°C的温度下,让氧原子与硅原子发生化学反应,在表面“长”出一层致密的二氧化硅。这种方法生长出来的氧化层,与硅的界面缺陷密度极低,堪称原子级的完美结合。

在先进制程中,热氧化的温度和时间被严格控制,因为界面层的厚度直接关系到晶体管的性能。太薄,起不到缓冲作用;太厚,会增加等效氧化层厚度,降低栅极的控制能力。对于5纳米及以下的工艺,界面层的厚度已经控制在0.7纳米左右,这仅仅是两到三个硅原子的厚度。

在沉积High-K介质之前,还会有一个表面预处理步骤,通常是用原子层沉积设备在界面层上再沉积一层极其均匀的超薄材料,进一步修复可能存在的缺陷,为后续的High-K沉积提供一个完美的基础。

界面层有多关键?三个维度看其重要性

第一,它决定了晶体管的开关速度。

界面层中哪怕只有几个原子的缺陷,都会成为电荷陷阱,捕获电子或空穴。这些被捕获的电荷会像“磁铁”一样,干扰栅极电场,导致阈值电压漂移、载流子迁移率下降。晶体管开关变慢,芯片主频就上不去。在先进制程中,界面态密度必须控制在每平方厘米十的十次方以下,这个标准极其苛刻。

第二,它关乎芯片的可靠性和寿命。

界面层是晶体管抵御电应力的第一道防线。在长期的电压应力下,如果界面层质量不佳,缺陷会不断积累,最终形成贯穿栅介质的导电通道,导致栅氧击穿。这就是所谓的“经时介电击穿”,是晶体管失效的主要模式之一。一个高质量的界面层,可以显著延长芯片的工作寿命。

第三,它影响漏电和功耗。

界面缺陷越多,栅极漏电就越严重。虽然High-K介质本身能有效阻挡漏电,但如果界面层没做好,电子仍然可以通过界面陷阱“跳”过去,形成漏电流。对于手机芯片来说,漏电就意味着待机时间缩短;对于数据中心来说,漏电就意味着电费飙升。

为什么先进制程更“依赖”界面层?

随着晶体管尺寸不断缩小,栅极介质变得越来越薄。在平面晶体管时代,栅氧厚度可以做到1纳米左右,界面层的质量就已经至关重要。到了FinFET时代,栅极从三个面包裹沟道,电场分布更复杂,对界面层的均匀性和一致性要求更高。而到了GAA晶体管时代,沟道变成了纳米线或纳米片,栅极360度环绕,界面层的质量直接决定了每根纳米线的电学性能是否一致。

在某种程度上,界面层已经成为制约晶体管进一步微缩的瓶颈之一。工程师们正在探索新的界面材料,比如在硅与High-K之间插入氮化层,或者用其他介质替代传统的二氧化硅,以期获得更薄的等效厚度和更好的界面质量。

结语

界面层薄到肉眼看不见,但它就像建筑物的地基,默默承载着晶体管这个“超级大楼”的每一层结构。从热氧化到原子层沉积,从几纳米到零点几纳米,界面层的每一次进步,都在为摩尔定律的延续添砖加瓦。下次你拿起手机,不妨想想那层只有几个原子厚度的薄膜,正在你的掌心深处,守护着每一次触屏的响应、每一帧画面的刷新。

-

晶体管

+关注

关注

78文章

10436浏览量

148553 -

芯片制造

+关注

关注

11文章

734浏览量

30529

原文标题:晶体管的界面层(interface layer)的秘密

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

晶体管中界面层的作用和重要性

晶体管中界面层的作用和重要性

评论