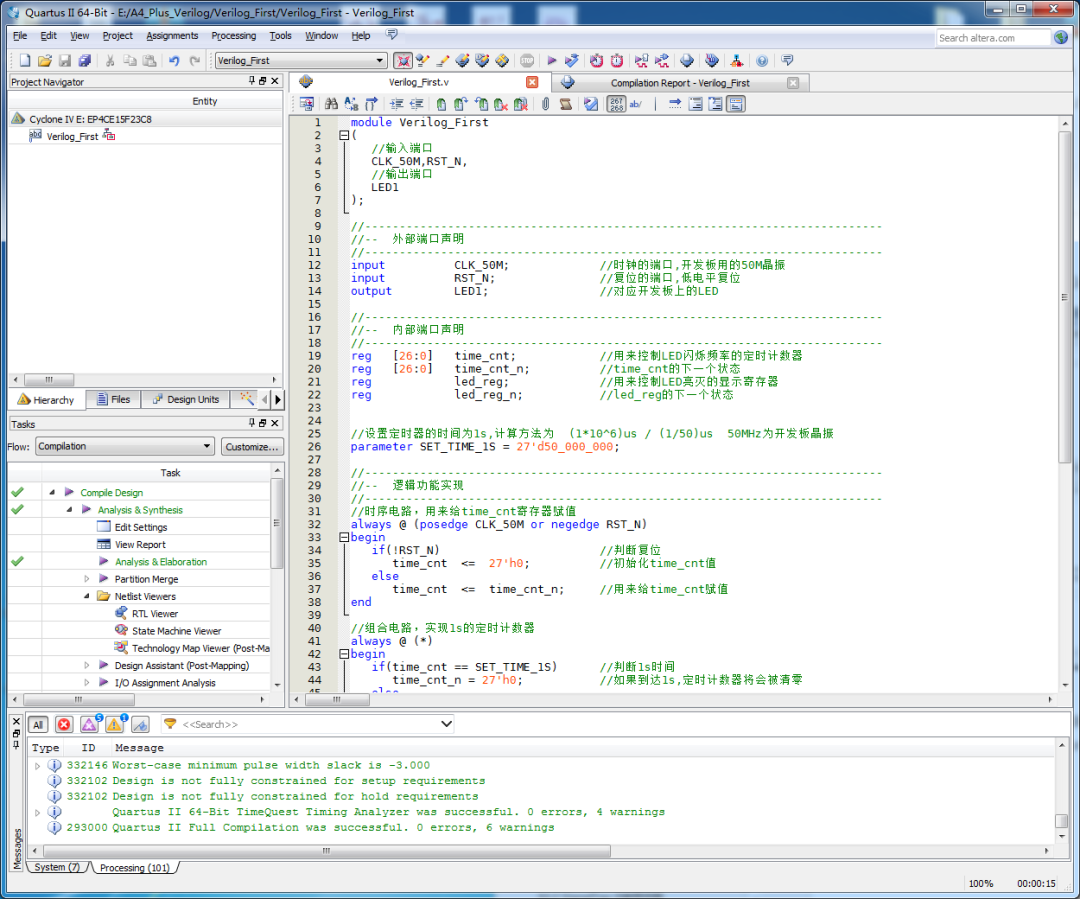

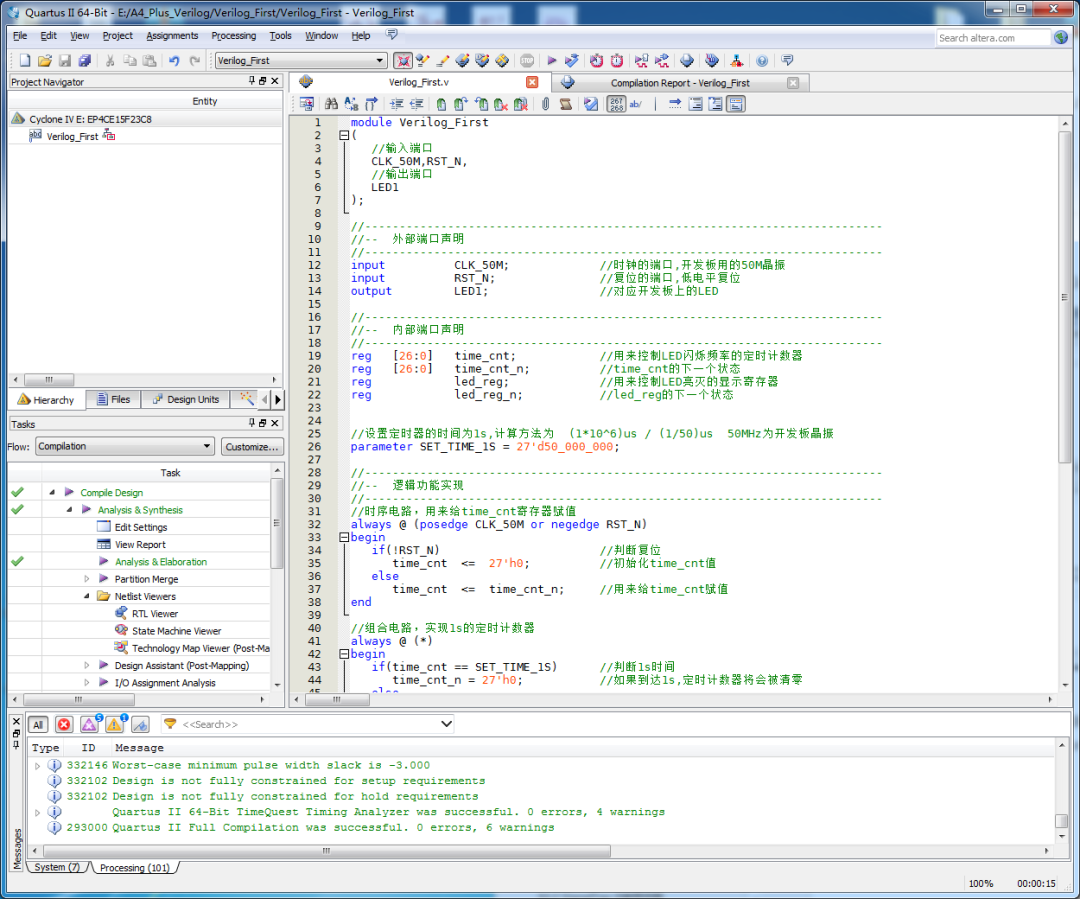

3 ModelSim工程实战之自动仿真说完了 ModelSim 的使用流程,接下来我们将会对每个流程进行详细的操作演示,一步步、手把手带领大家学习使用 ModelSim 软件。首先我们讲解的 ModelSim 自动仿真,所谓自动仿真,其实是在 Quartus II 中调用 ModelSim 软件来进行仿真,在调用过程中,Quartus II 会帮我们完成 ModelSim 中的所有操作,我们只需要分析最后的仿真结果。下面我们就以上章节中我们创建的 Quartus II 软件工程为例,进行仿真。3.1 检查 EDA 路径首先我们打开之前的 Quartus II 工程,如图 在该页面中,我们在菜单栏中找到【Tool】→【Options】按钮并打开,在打开的页面左侧,我们找到“EDA Tool Options”点击,如图

在该页面中,我们在菜单栏中找到【Tool】→【Options】按钮并打开,在打开的页面左侧,我们找到“EDA Tool Options”点击,如图

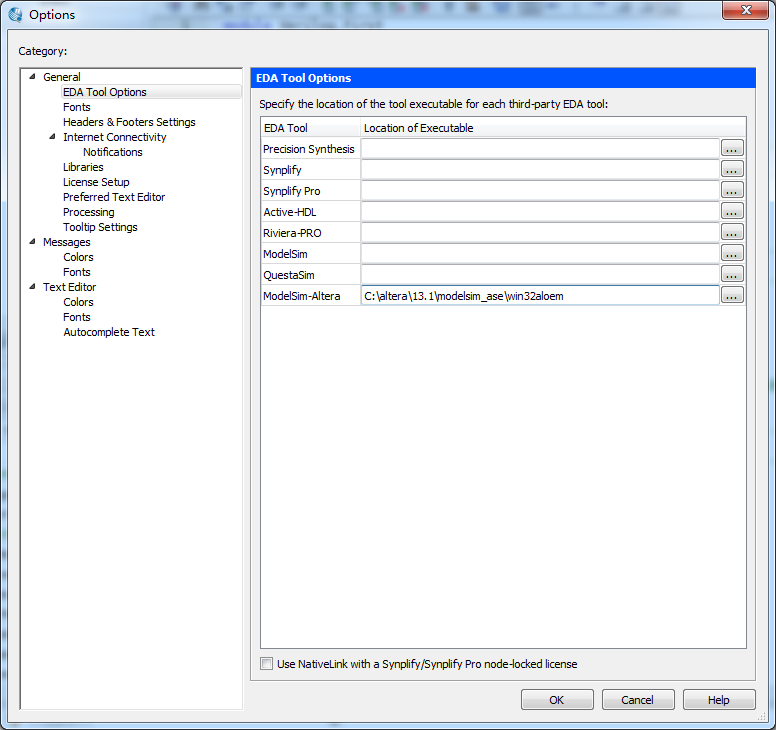

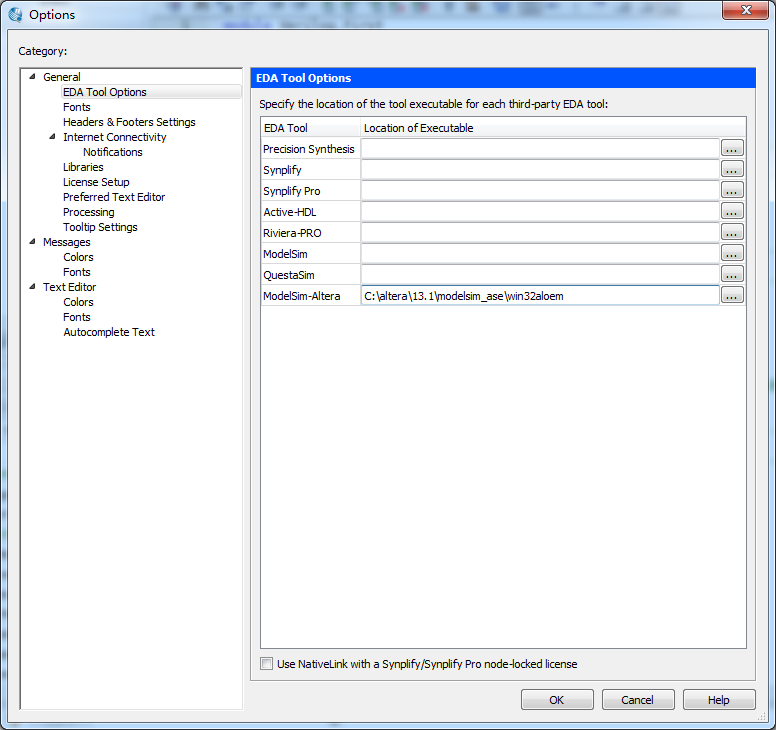

在该页面中,如果你安装的是 ModelSim 软件,那么你需要在 ModelSim 路径中进行设置,这里我们使用的 ModelSim-Altera , 所 以 我 们 将 ModelSim-Altera 路 径 设 置 成 了C:altera13.1modelsim_asewin32aloem。这里需要大家注意的是一定要选择 modelsim_ase文件夹中的 win32aloem,不要选择 modelsim_ae 文件夹中的 win32aloem。还记得我们前面说的么?ae 是收费版本,我们是不能使用的,这里的 ase 免费版本也是可以满足我们的设计的。路径设置完成以后,我们点击【OK】返回我们的 Quartus II 软件界面。3.2 选择 EDA 工具我们在 Quartus II 软件页面的菜单栏中,我们找到【Assignments】→【Settings】按钮并打开,在打开的页面左侧我们找到“EDA Tool Settings”点击,如图

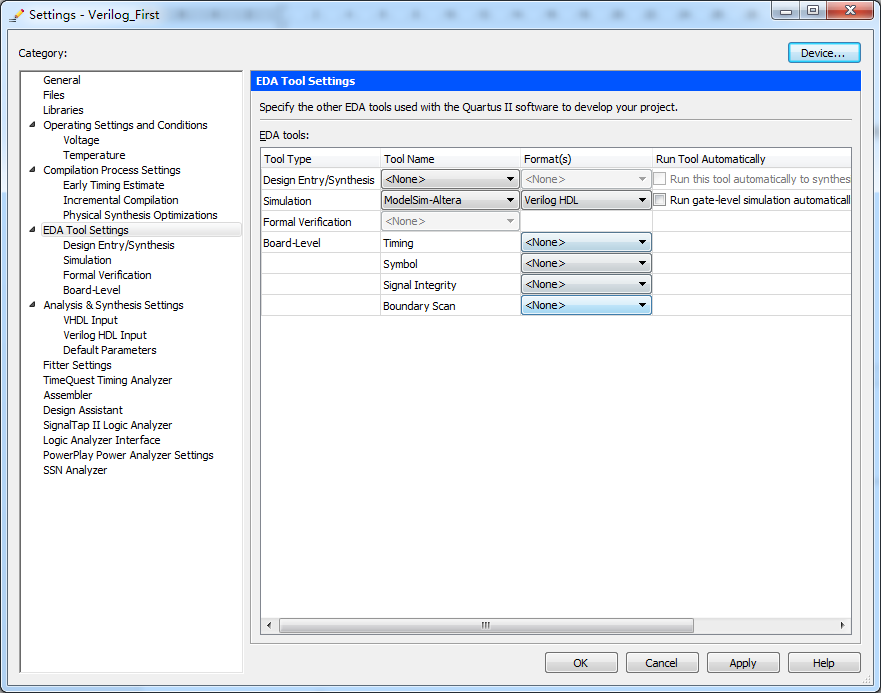

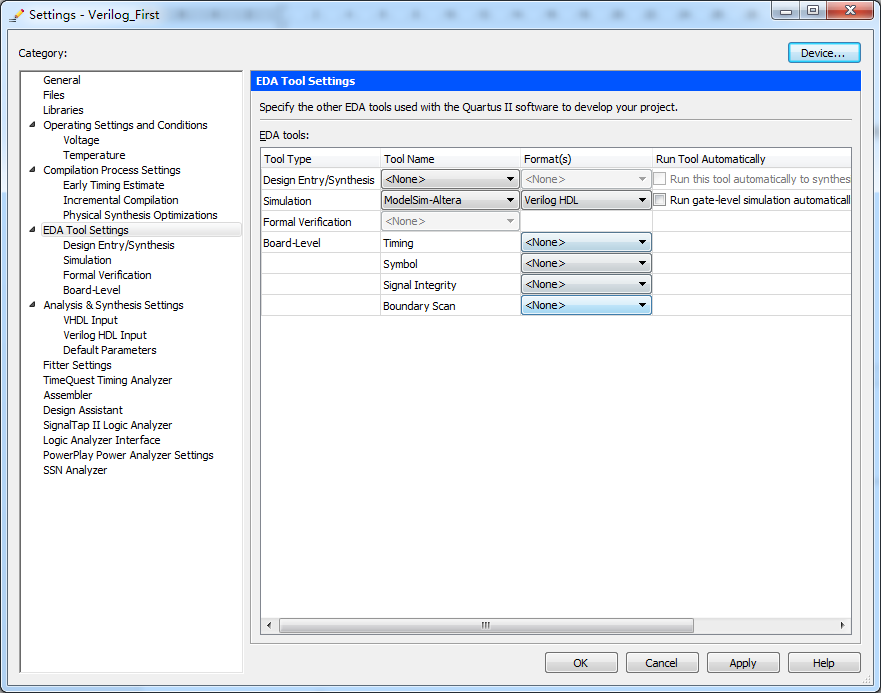

在该页面中,如果你安装的是 ModelSim 软件,那么你需要在 ModelSim 路径中进行设置,这里我们使用的 ModelSim-Altera , 所 以 我 们 将 ModelSim-Altera 路 径 设 置 成 了C:altera13.1modelsim_asewin32aloem。这里需要大家注意的是一定要选择 modelsim_ase文件夹中的 win32aloem,不要选择 modelsim_ae 文件夹中的 win32aloem。还记得我们前面说的么?ae 是收费版本,我们是不能使用的,这里的 ase 免费版本也是可以满足我们的设计的。路径设置完成以后,我们点击【OK】返回我们的 Quartus II 软件界面。3.2 选择 EDA 工具我们在 Quartus II 软件页面的菜单栏中,我们找到【Assignments】→【Settings】按钮并打开,在打开的页面左侧我们找到“EDA Tool Settings”点击,如图 还记得我们之前创建工程的时候,由于在 Quartus II 软件中我们没有用到仿真,所以我们将这里设置成了“None”,现在我们需要用到仿真工具了,我们需要在这里将 Simulation 设置成“ModelSim-Altera、Verilog HDL”。设置完成之后,我们点击【OK】返回 Quartus II 软件页 面中。3.3 编写仿真文件我们在 Quartus II 软件页面的菜单栏中,我们找到【Processing】→【Start】→【Start TestBench Template Writer】按钮并点击,这时 Message 窗口中会显示,如图

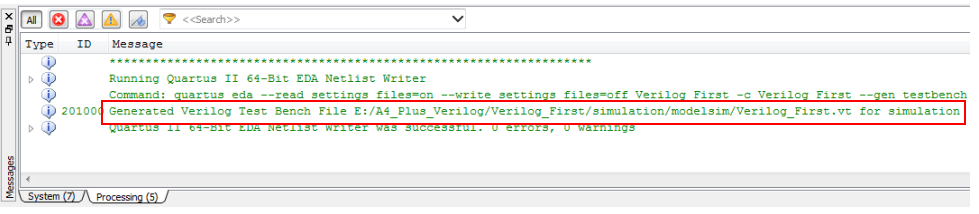

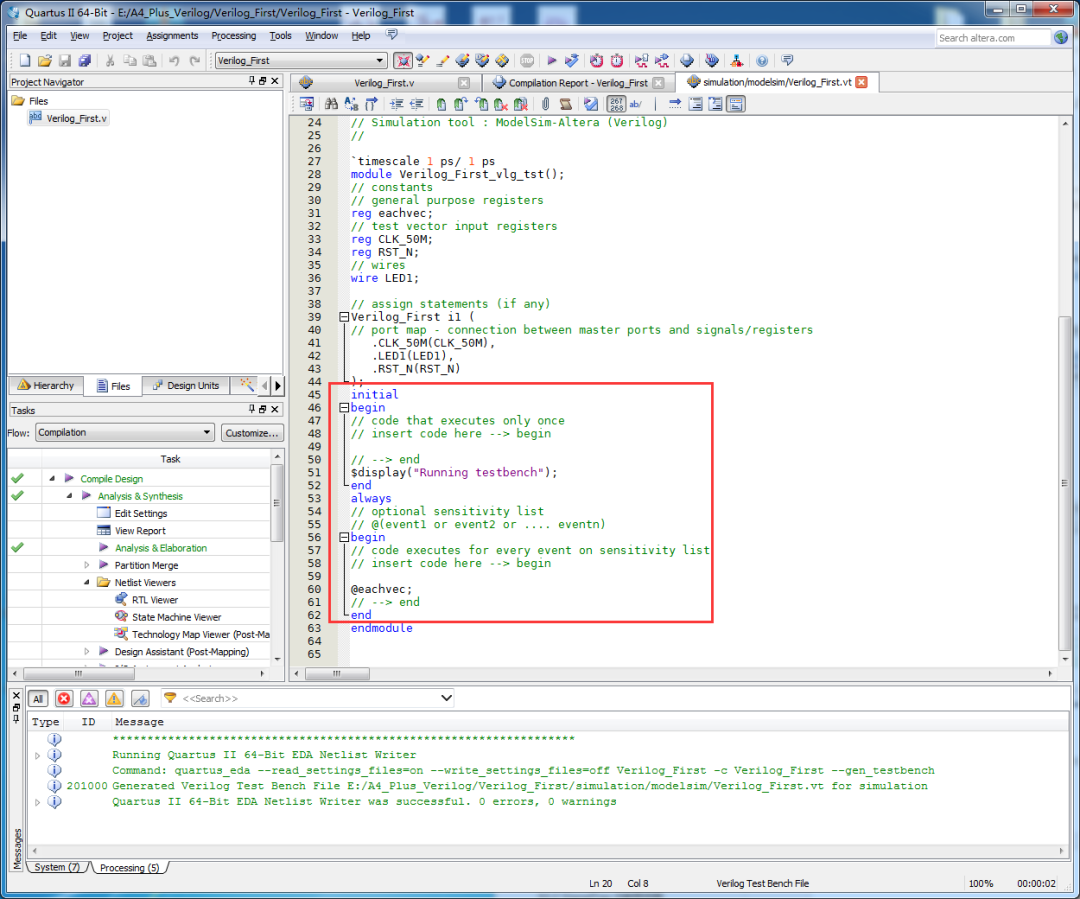

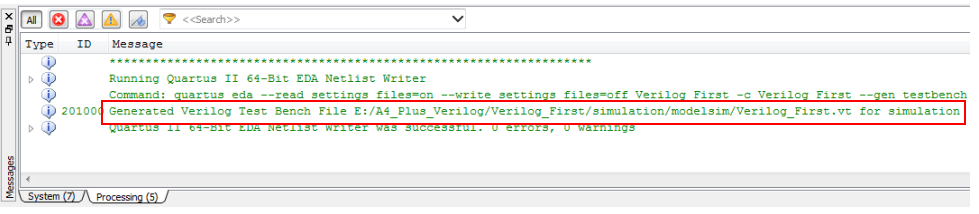

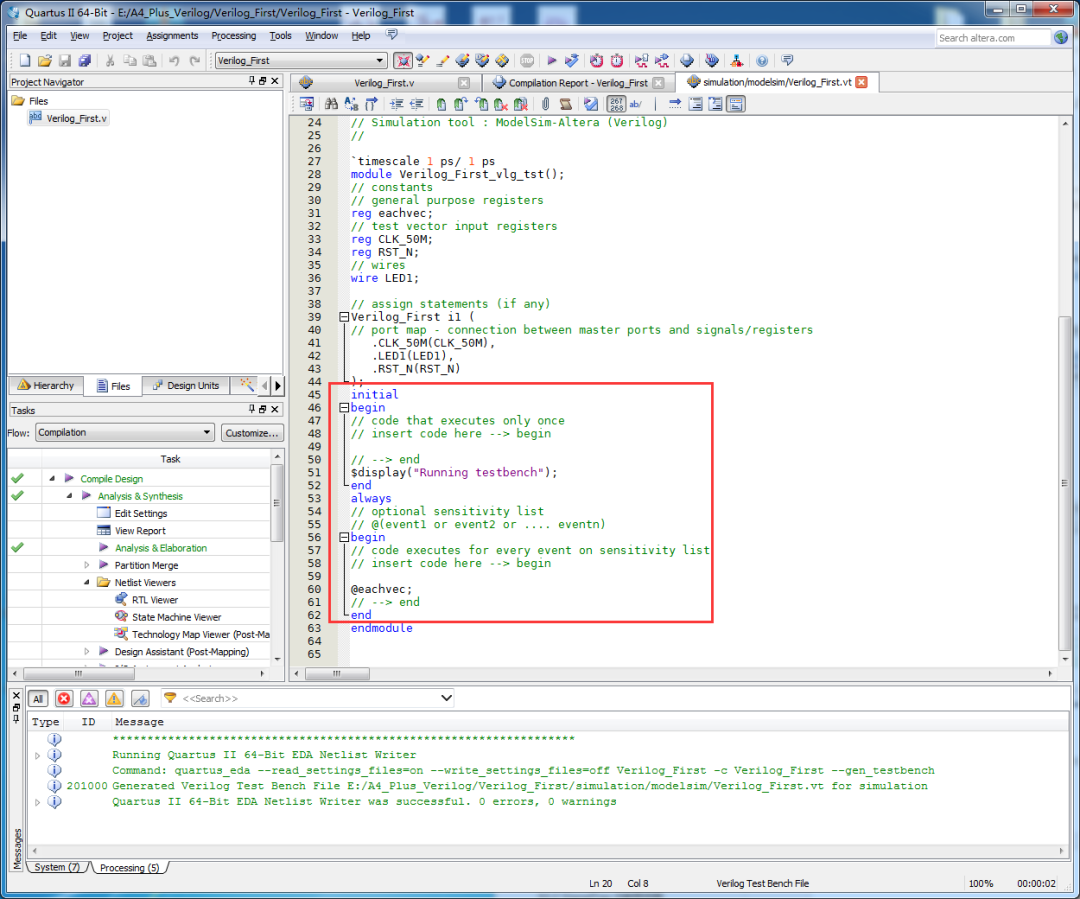

还记得我们之前创建工程的时候,由于在 Quartus II 软件中我们没有用到仿真,所以我们将这里设置成了“None”,现在我们需要用到仿真工具了,我们需要在这里将 Simulation 设置成“ModelSim-Altera、Verilog HDL”。设置完成之后,我们点击【OK】返回 Quartus II 软件页 面中。3.3 编写仿真文件我们在 Quartus II 软件页面的菜单栏中,我们找到【Processing】→【Start】→【Start TestBench Template Writer】按钮并点击,这时 Message 窗口中会显示,如图 我们可以从这条信息中知道,Quartus II 软件自动给我们生成了一个 TestBench 模板,我们只需要在这个模板上稍作修改就能直接使用了。我们在工程目录下找到 Verilog_First.vt 文件,我们可以用记事本打开进行修改,也可以使用 Quartus II 软件打开它进行修改,这里我们建议还在 Quartus II 软件中进行修改。我们在 Quartus II 软件的菜单栏中找到【File】→【Open】按钮并打开,在对话框中找到我们的 Verilog 文件,如图

我们可以从这条信息中知道,Quartus II 软件自动给我们生成了一个 TestBench 模板,我们只需要在这个模板上稍作修改就能直接使用了。我们在工程目录下找到 Verilog_First.vt 文件,我们可以用记事本打开进行修改,也可以使用 Quartus II 软件打开它进行修改,这里我们建议还在 Quartus II 软件中进行修改。我们在 Quartus II 软件的菜单栏中找到【File】→【Open】按钮并打开,在对话框中找到我们的 Verilog 文件,如图

打开之后,如图

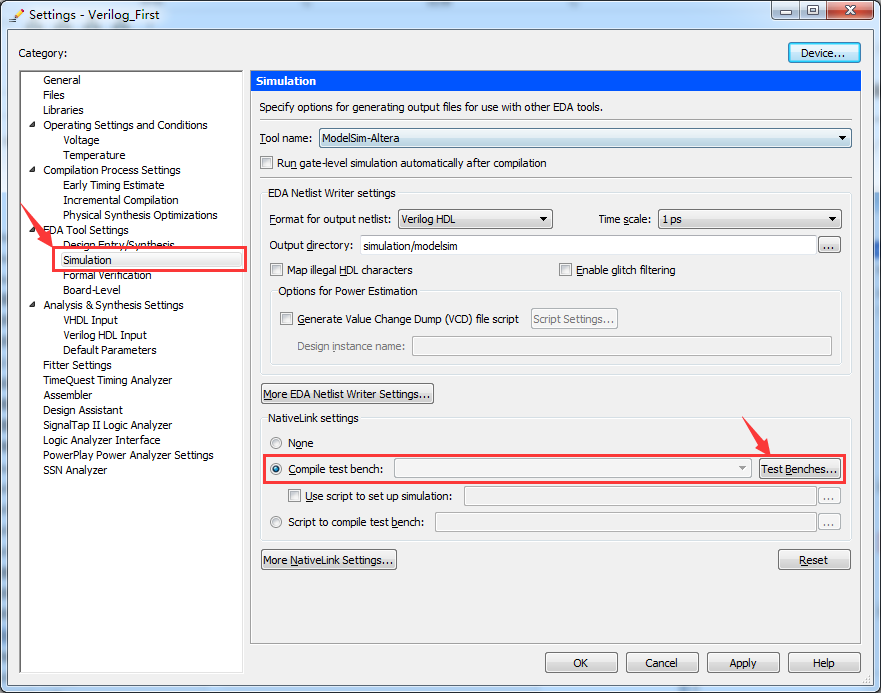

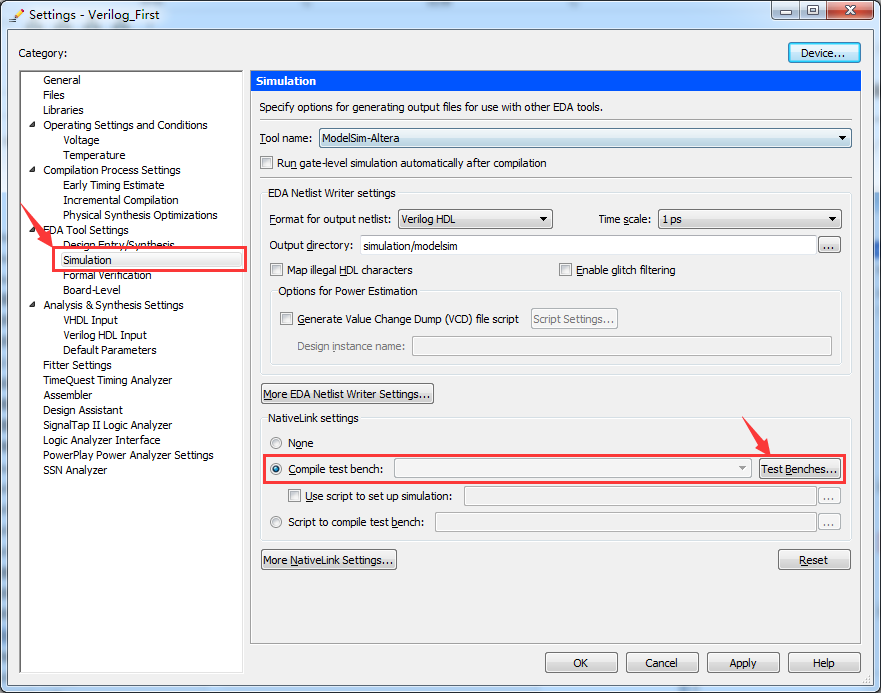

打开之后,如图 在该图中我们可以看到,Quartus II 软件已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个模板里添加我们需要的测试代码(也就是我们常说的激励)。为了让读者能够更好的理解仿真,这里我们就简单介绍一下 TestBench 源代码:代码的第 1 行,表示仿真的单位时间为 1ps,精度为 1ps。想要进行仿真首先要规定时间单位,我们建议大家最好在 Testbench 里面统一规定时间单位,不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,timescale 是 Verilog 语法中的不可综合语法。代码的第 2 行就是我们熟悉的部分了,其中第 5 行至第 10 行是我们的数据类型定义,这里我们可以看到 reg eachvec 是一个多余的信号,没有任何作用,我们也可以将它删除,接下来我们再来看第 13 行至第 18 行,这一部分就是一个模块调用,它将我们的 Verilog 模块中的信号连接到我们的 TestBench 模块中。最后,我们再来看下第 20 行至第 32 行代码,其中第 20 行至第 26 行是信号的初始化,第 28 行至第 31 行是时钟信号的生成。这里我们主要来讲讲#10000,#10000 表示的是延迟 10000ps(即 10ns),具体的延迟单位,还是要看我们的 timescale 是如何设置的。至此,整个代码都介绍完了。3.4 配置仿真功能编写完了仿真文件,接下来我们需要在 Quartus II 软件中配置仿真功能,我们在 Quartus II软件界面的菜单栏找到【Assigement】→【Settings】按钮并打开,在打开的页面中,我们找到左侧的 Simulation 点击,出现如图

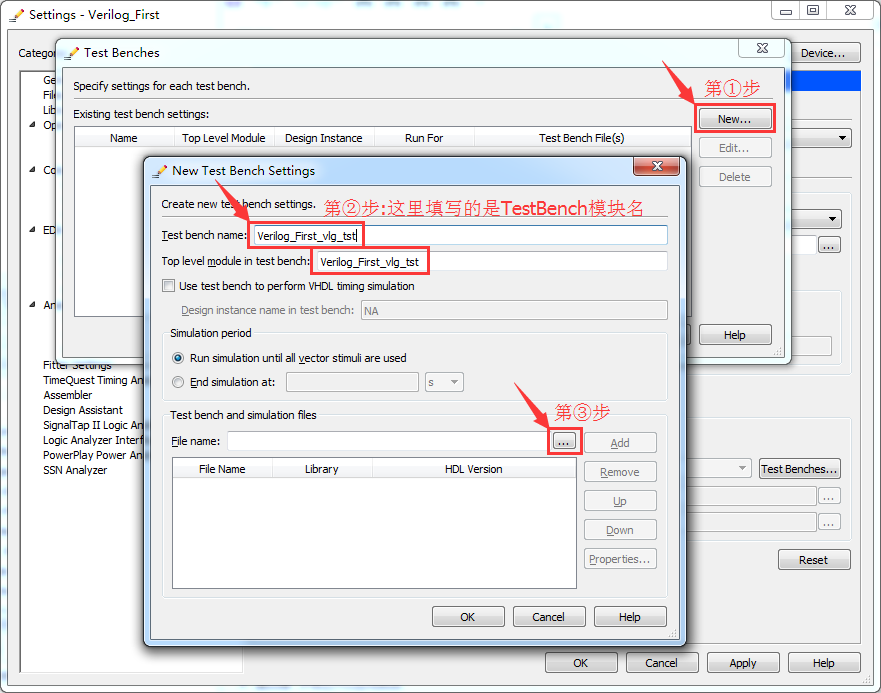

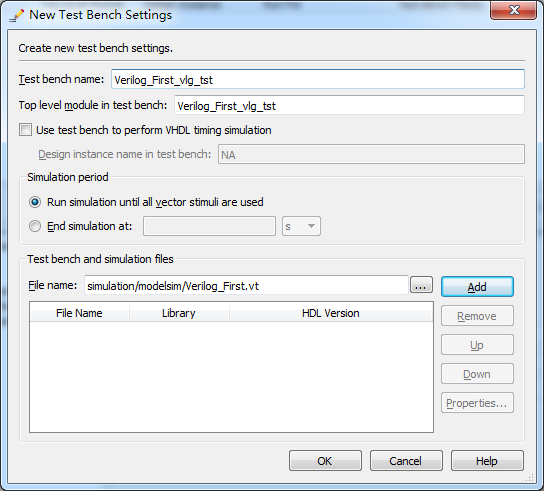

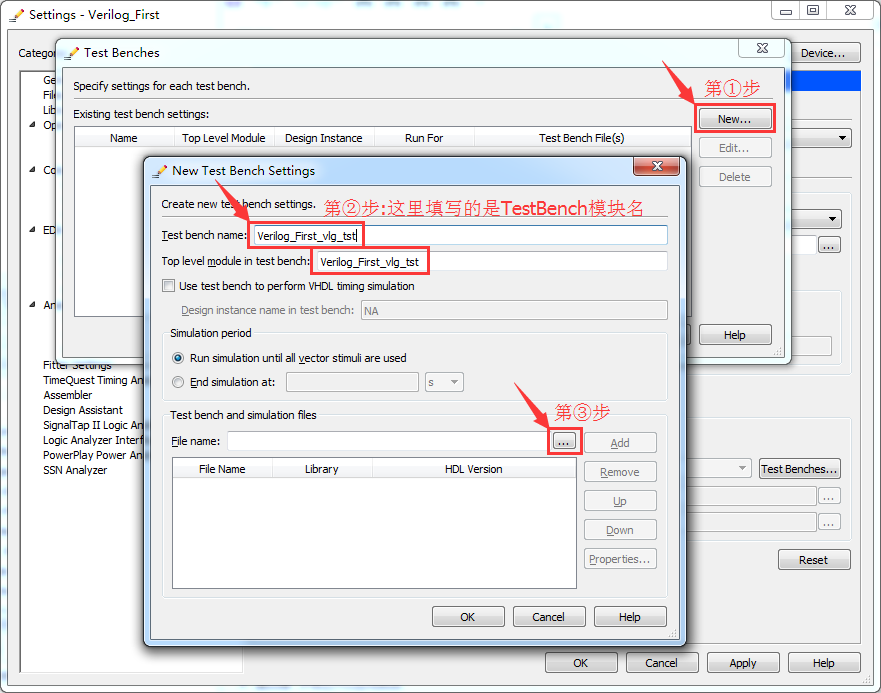

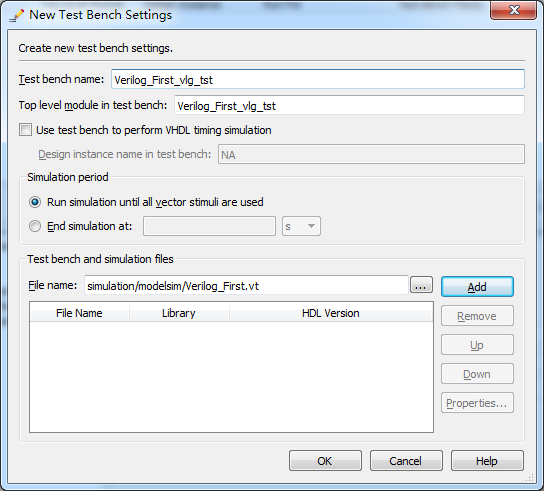

在该图中我们可以看到,Quartus II 软件已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个模板里添加我们需要的测试代码(也就是我们常说的激励)。为了让读者能够更好的理解仿真,这里我们就简单介绍一下 TestBench 源代码:代码的第 1 行,表示仿真的单位时间为 1ps,精度为 1ps。想要进行仿真首先要规定时间单位,我们建议大家最好在 Testbench 里面统一规定时间单位,不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,timescale 是 Verilog 语法中的不可综合语法。代码的第 2 行就是我们熟悉的部分了,其中第 5 行至第 10 行是我们的数据类型定义,这里我们可以看到 reg eachvec 是一个多余的信号,没有任何作用,我们也可以将它删除,接下来我们再来看第 13 行至第 18 行,这一部分就是一个模块调用,它将我们的 Verilog 模块中的信号连接到我们的 TestBench 模块中。最后,我们再来看下第 20 行至第 32 行代码,其中第 20 行至第 26 行是信号的初始化,第 28 行至第 31 行是时钟信号的生成。这里我们主要来讲讲#10000,#10000 表示的是延迟 10000ps(即 10ns),具体的延迟单位,还是要看我们的 timescale 是如何设置的。至此,整个代码都介绍完了。3.4 配置仿真功能编写完了仿真文件,接下来我们需要在 Quartus II 软件中配置仿真功能,我们在 Quartus II软件界面的菜单栏找到【Assigement】→【Settings】按钮并打开,在打开的页面中,我们找到左侧的 Simulation 点击,出现如图 我们选中“Compile Test bench”,然后单击后面的【Test Benches】按钮,则出现如图 2.9所示的“Test Benches”窗口(也就是图中上面的窗口),接着我们单击【New】按钮,则会出现如图所示的“New Test Bench Settings”窗口(也就是图中下面的窗口)。

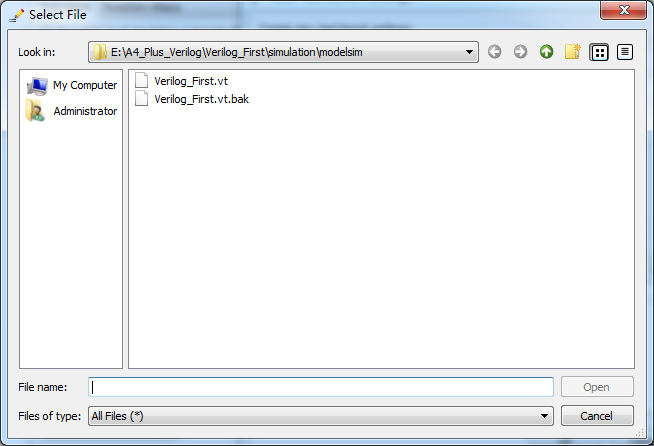

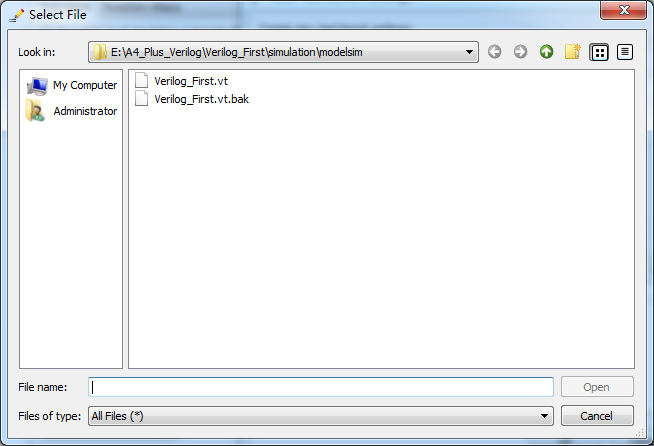

我们选中“Compile Test bench”,然后单击后面的【Test Benches】按钮,则出现如图 2.9所示的“Test Benches”窗口(也就是图中上面的窗口),接着我们单击【New】按钮,则会出现如图所示的“New Test Bench Settings”窗口(也就是图中下面的窗口)。 在该页面中,我们将 TestBench 模块名输入到“Test bench name”和 “Top level module in test bench”的编辑栏中。接着我们在“Test bench and simulation files”下拉列表框中添加仿真文件,如图 所示,点击【Open】即可。

在该页面中,我们将 TestBench 模块名输入到“Test bench name”和 “Top level module in test bench”的编辑栏中。接着我们在“Test bench and simulation files”下拉列表框中添加仿真文件,如图 所示,点击【Open】即可。 然后单击【Add】 按钮添加到最下面的列表中如图

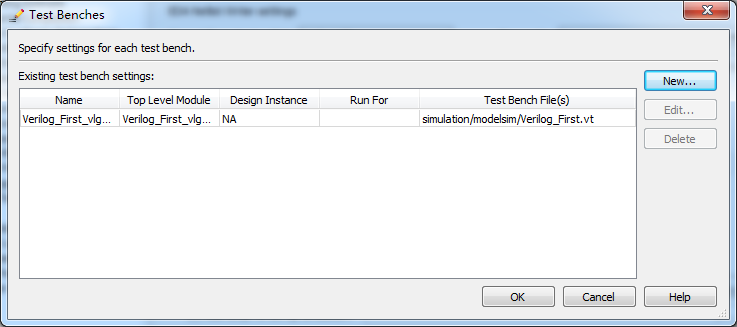

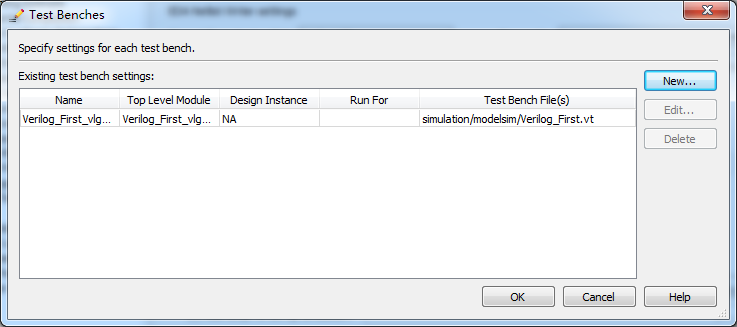

然后单击【Add】 按钮添加到最下面的列表中如图 完成后我们单击【OK】按钮,便可看到如图 2.12 所示的“Test benches”窗口的列表中出现了刚才添加的仿真文件相关信息,至此,我们仿真文件添加完成了,接着我们单击【OK】按钮,返回我们的 Quartus II 软件界面。

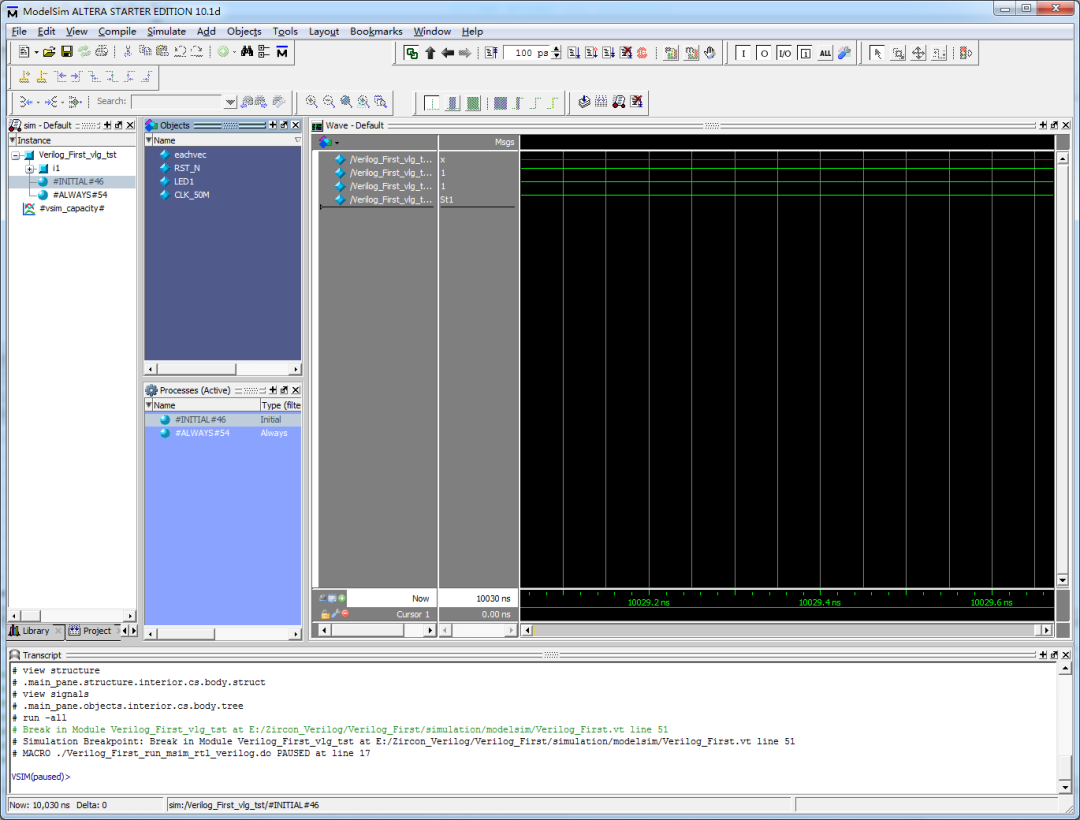

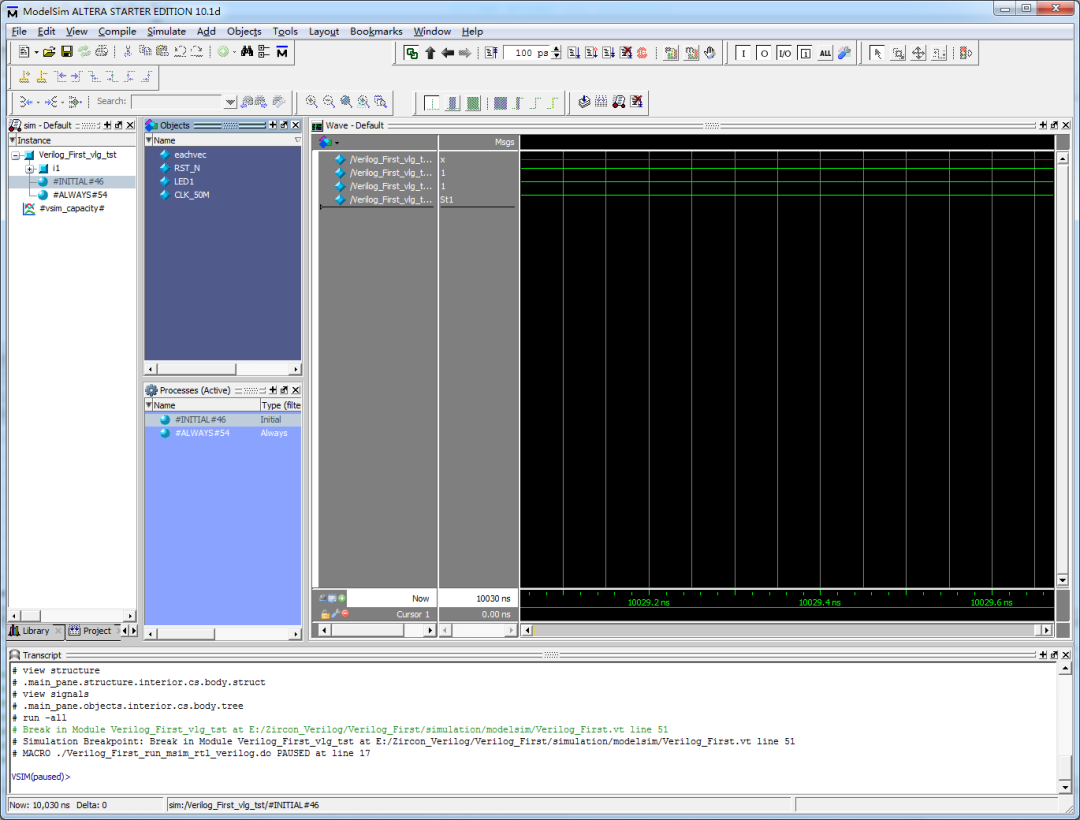

完成后我们单击【OK】按钮,便可看到如图 2.12 所示的“Test benches”窗口的列表中出现了刚才添加的仿真文件相关信息,至此,我们仿真文件添加完成了,接着我们单击【OK】按钮,返回我们的 Quartus II 软件界面。 3.5 开始功能仿真万事俱备只欠东风,经过上面这么多的操作步骤,我们终于完成了所有设置,接下来我们就可以进行仿真了,在开始仿真之前,我们这里有一点要需要注意,我们在 Quartus II 软件中实现的功能是 LED 闪烁,它的间隔时间是 1s,如果我们想要仿真这个功能,那么我们仿真软件运行时间最低就是 1s。这 1s 钟在我们看来是很短很短的,不过在仿真软件看来是很长很长的,我们的仿真软件单位可是 ps。为了便于我们仿真,这里我们需要稍微改动一下 Verilog 代码,我们需要将 parameter SET_TIME_1S = 27'd50_000_000;修改为 parameter SET_TIME_1S = 27'd50; 也就是将我们原来的 1s 钟修改成了 1us。修改完毕后,我们在 Quartus II 软件界面中的菜单栏中找到【Tools】→【Run Simulation Tool】→【RTL Simulation】按钮并点击,则会出现如图 2.13 所示界面。

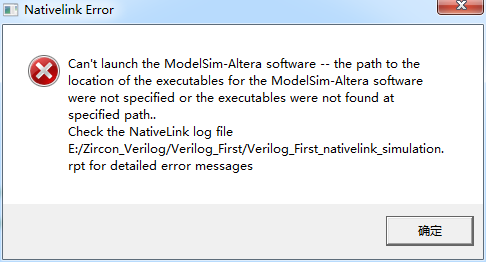

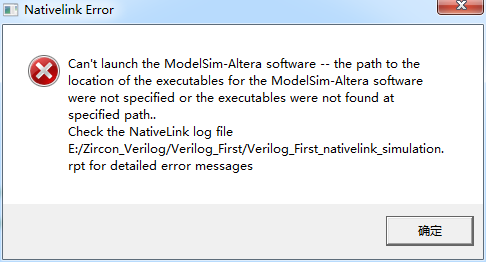

3.5 开始功能仿真万事俱备只欠东风,经过上面这么多的操作步骤,我们终于完成了所有设置,接下来我们就可以进行仿真了,在开始仿真之前,我们这里有一点要需要注意,我们在 Quartus II 软件中实现的功能是 LED 闪烁,它的间隔时间是 1s,如果我们想要仿真这个功能,那么我们仿真软件运行时间最低就是 1s。这 1s 钟在我们看来是很短很短的,不过在仿真软件看来是很长很长的,我们的仿真软件单位可是 ps。为了便于我们仿真,这里我们需要稍微改动一下 Verilog 代码,我们需要将 parameter SET_TIME_1S = 27'd50_000_000;修改为 parameter SET_TIME_1S = 27'd50; 也就是将我们原来的 1s 钟修改成了 1us。修改完毕后,我们在 Quartus II 软件界面中的菜单栏中找到【Tools】→【Run Simulation Tool】→【RTL Simulation】按钮并点击,则会出现如图 2.13 所示界面。 看到这里,也许有的朋友点击【RTL Simulation】并没有出现 Modelsim 仿真窗口界面,而是出现了如图 2.14 所示界面。

看到这里,也许有的朋友点击【RTL Simulation】并没有出现 Modelsim 仿真窗口界面,而是出现了如图 2.14 所示界面。 出现这种错误主要是因为我们前面设置的 Modelsim 路径不对造成的,如何解决这个问题呢?我们尝试将 ModelSim-Altera 路径设置成了 C:altera13.1modelsim_asewin32aloem。这和我们刚刚设置不同的是,我们在路径的最后面添加了一个反斜杠。这时,我们再点击【RTL Simulation】按钮就会出现 Modelsim 仿真窗口界面了,这里我们需要说明的是:有的电脑不添加反斜杠是可以运行的,有的电脑不添加反斜杠是不能运行。在 Modelsim 软件启动过程中,我 们不需要任何操作,它会自动完成仿真,并给出我们所需要的波形,当波形图出现之后,我们就可以查看波形来判断设计功能是否正常了。

出现这种错误主要是因为我们前面设置的 Modelsim 路径不对造成的,如何解决这个问题呢?我们尝试将 ModelSim-Altera 路径设置成了 C:altera13.1modelsim_asewin32aloem。这和我们刚刚设置不同的是,我们在路径的最后面添加了一个反斜杠。这时,我们再点击【RTL Simulation】按钮就会出现 Modelsim 仿真窗口界面了,这里我们需要说明的是:有的电脑不添加反斜杠是可以运行的,有的电脑不添加反斜杠是不能运行。在 Modelsim 软件启动过程中,我 们不需要任何操作,它会自动完成仿真,并给出我们所需要的波形,当波形图出现之后,我们就可以查看波形来判断设计功能是否正常了。

在该页面中,我们在菜单栏中找到【Tool】→【Options】按钮并打开,在打开的页面左侧,我们找到“EDA Tool Options”点击,如图

在该页面中,我们在菜单栏中找到【Tool】→【Options】按钮并打开,在打开的页面左侧,我们找到“EDA Tool Options”点击,如图

在该页面中,如果你安装的是 ModelSim 软件,那么你需要在 ModelSim 路径中进行设置,这里我们使用的 ModelSim-Altera , 所 以 我 们 将 ModelSim-Altera 路 径 设 置 成 了C:altera13.1modelsim_asewin32aloem。这里需要大家注意的是一定要选择 modelsim_ase文件夹中的 win32aloem,不要选择 modelsim_ae 文件夹中的 win32aloem。还记得我们前面说的么?ae 是收费版本,我们是不能使用的,这里的 ase 免费版本也是可以满足我们的设计的。路径设置完成以后,我们点击【OK】返回我们的 Quartus II 软件界面。3.2 选择 EDA 工具我们在 Quartus II 软件页面的菜单栏中,我们找到【Assignments】→【Settings】按钮并打开,在打开的页面左侧我们找到“EDA Tool Settings”点击,如图

在该页面中,如果你安装的是 ModelSim 软件,那么你需要在 ModelSim 路径中进行设置,这里我们使用的 ModelSim-Altera , 所 以 我 们 将 ModelSim-Altera 路 径 设 置 成 了C:altera13.1modelsim_asewin32aloem。这里需要大家注意的是一定要选择 modelsim_ase文件夹中的 win32aloem,不要选择 modelsim_ae 文件夹中的 win32aloem。还记得我们前面说的么?ae 是收费版本,我们是不能使用的,这里的 ase 免费版本也是可以满足我们的设计的。路径设置完成以后,我们点击【OK】返回我们的 Quartus II 软件界面。3.2 选择 EDA 工具我们在 Quartus II 软件页面的菜单栏中,我们找到【Assignments】→【Settings】按钮并打开,在打开的页面左侧我们找到“EDA Tool Settings”点击,如图 还记得我们之前创建工程的时候,由于在 Quartus II 软件中我们没有用到仿真,所以我们将这里设置成了“None”,现在我们需要用到仿真工具了,我们需要在这里将 Simulation 设置成“ModelSim-Altera、Verilog HDL”。设置完成之后,我们点击【OK】返回 Quartus II 软件页 面中。3.3 编写仿真文件我们在 Quartus II 软件页面的菜单栏中,我们找到【Processing】→【Start】→【Start TestBench Template Writer】按钮并点击,这时 Message 窗口中会显示,如图

还记得我们之前创建工程的时候,由于在 Quartus II 软件中我们没有用到仿真,所以我们将这里设置成了“None”,现在我们需要用到仿真工具了,我们需要在这里将 Simulation 设置成“ModelSim-Altera、Verilog HDL”。设置完成之后,我们点击【OK】返回 Quartus II 软件页 面中。3.3 编写仿真文件我们在 Quartus II 软件页面的菜单栏中,我们找到【Processing】→【Start】→【Start TestBench Template Writer】按钮并点击,这时 Message 窗口中会显示,如图 我们可以从这条信息中知道,Quartus II 软件自动给我们生成了一个 TestBench 模板,我们只需要在这个模板上稍作修改就能直接使用了。我们在工程目录下找到 Verilog_First.vt 文件,我们可以用记事本打开进行修改,也可以使用 Quartus II 软件打开它进行修改,这里我们建议还在 Quartus II 软件中进行修改。我们在 Quartus II 软件的菜单栏中找到【File】→【Open】按钮并打开,在对话框中找到我们的 Verilog 文件,如图

我们可以从这条信息中知道,Quartus II 软件自动给我们生成了一个 TestBench 模板,我们只需要在这个模板上稍作修改就能直接使用了。我们在工程目录下找到 Verilog_First.vt 文件,我们可以用记事本打开进行修改,也可以使用 Quartus II 软件打开它进行修改,这里我们建议还在 Quartus II 软件中进行修改。我们在 Quartus II 软件的菜单栏中找到【File】→【Open】按钮并打开,在对话框中找到我们的 Verilog 文件,如图

打开之后,如图

打开之后,如图 在该图中我们可以看到,Quartus II 软件已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个模板里添加我们需要的测试代码(也就是我们常说的激励)。为了让读者能够更好的理解仿真,这里我们就简单介绍一下 TestBench 源代码:代码的第 1 行,表示仿真的单位时间为 1ps,精度为 1ps。想要进行仿真首先要规定时间单位,我们建议大家最好在 Testbench 里面统一规定时间单位,不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,timescale 是 Verilog 语法中的不可综合语法。代码的第 2 行就是我们熟悉的部分了,其中第 5 行至第 10 行是我们的数据类型定义,这里我们可以看到 reg eachvec 是一个多余的信号,没有任何作用,我们也可以将它删除,接下来我们再来看第 13 行至第 18 行,这一部分就是一个模块调用,它将我们的 Verilog 模块中的信号连接到我们的 TestBench 模块中。最后,我们再来看下第 20 行至第 32 行代码,其中第 20 行至第 26 行是信号的初始化,第 28 行至第 31 行是时钟信号的生成。这里我们主要来讲讲#10000,#10000 表示的是延迟 10000ps(即 10ns),具体的延迟单位,还是要看我们的 timescale 是如何设置的。至此,整个代码都介绍完了。3.4 配置仿真功能编写完了仿真文件,接下来我们需要在 Quartus II 软件中配置仿真功能,我们在 Quartus II软件界面的菜单栏找到【Assigement】→【Settings】按钮并打开,在打开的页面中,我们找到左侧的 Simulation 点击,出现如图

在该图中我们可以看到,Quartus II 软件已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个模板里添加我们需要的测试代码(也就是我们常说的激励)。为了让读者能够更好的理解仿真,这里我们就简单介绍一下 TestBench 源代码:代码的第 1 行,表示仿真的单位时间为 1ps,精度为 1ps。想要进行仿真首先要规定时间单位,我们建议大家最好在 Testbench 里面统一规定时间单位,不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,timescale 是 Verilog 语法中的不可综合语法。代码的第 2 行就是我们熟悉的部分了,其中第 5 行至第 10 行是我们的数据类型定义,这里我们可以看到 reg eachvec 是一个多余的信号,没有任何作用,我们也可以将它删除,接下来我们再来看第 13 行至第 18 行,这一部分就是一个模块调用,它将我们的 Verilog 模块中的信号连接到我们的 TestBench 模块中。最后,我们再来看下第 20 行至第 32 行代码,其中第 20 行至第 26 行是信号的初始化,第 28 行至第 31 行是时钟信号的生成。这里我们主要来讲讲#10000,#10000 表示的是延迟 10000ps(即 10ns),具体的延迟单位,还是要看我们的 timescale 是如何设置的。至此,整个代码都介绍完了。3.4 配置仿真功能编写完了仿真文件,接下来我们需要在 Quartus II 软件中配置仿真功能,我们在 Quartus II软件界面的菜单栏找到【Assigement】→【Settings】按钮并打开,在打开的页面中,我们找到左侧的 Simulation 点击,出现如图 我们选中“Compile Test bench”,然后单击后面的【Test Benches】按钮,则出现如图 2.9所示的“Test Benches”窗口(也就是图中上面的窗口),接着我们单击【New】按钮,则会出现如图所示的“New Test Bench Settings”窗口(也就是图中下面的窗口)。

我们选中“Compile Test bench”,然后单击后面的【Test Benches】按钮,则出现如图 2.9所示的“Test Benches”窗口(也就是图中上面的窗口),接着我们单击【New】按钮,则会出现如图所示的“New Test Bench Settings”窗口(也就是图中下面的窗口)。 在该页面中,我们将 TestBench 模块名输入到“Test bench name”和 “Top level module in test bench”的编辑栏中。接着我们在“Test bench and simulation files”下拉列表框中添加仿真文件,如图 所示,点击【Open】即可。

在该页面中,我们将 TestBench 模块名输入到“Test bench name”和 “Top level module in test bench”的编辑栏中。接着我们在“Test bench and simulation files”下拉列表框中添加仿真文件,如图 所示,点击【Open】即可。 然后单击【Add】 按钮添加到最下面的列表中如图

然后单击【Add】 按钮添加到最下面的列表中如图 完成后我们单击【OK】按钮,便可看到如图 2.12 所示的“Test benches”窗口的列表中出现了刚才添加的仿真文件相关信息,至此,我们仿真文件添加完成了,接着我们单击【OK】按钮,返回我们的 Quartus II 软件界面。

完成后我们单击【OK】按钮,便可看到如图 2.12 所示的“Test benches”窗口的列表中出现了刚才添加的仿真文件相关信息,至此,我们仿真文件添加完成了,接着我们单击【OK】按钮,返回我们的 Quartus II 软件界面。 3.5 开始功能仿真万事俱备只欠东风,经过上面这么多的操作步骤,我们终于完成了所有设置,接下来我们就可以进行仿真了,在开始仿真之前,我们这里有一点要需要注意,我们在 Quartus II 软件中实现的功能是 LED 闪烁,它的间隔时间是 1s,如果我们想要仿真这个功能,那么我们仿真软件运行时间最低就是 1s。这 1s 钟在我们看来是很短很短的,不过在仿真软件看来是很长很长的,我们的仿真软件单位可是 ps。为了便于我们仿真,这里我们需要稍微改动一下 Verilog 代码,我们需要将 parameter SET_TIME_1S = 27'd50_000_000;修改为 parameter SET_TIME_1S = 27'd50; 也就是将我们原来的 1s 钟修改成了 1us。修改完毕后,我们在 Quartus II 软件界面中的菜单栏中找到【Tools】→【Run Simulation Tool】→【RTL Simulation】按钮并点击,则会出现如图 2.13 所示界面。

3.5 开始功能仿真万事俱备只欠东风,经过上面这么多的操作步骤,我们终于完成了所有设置,接下来我们就可以进行仿真了,在开始仿真之前,我们这里有一点要需要注意,我们在 Quartus II 软件中实现的功能是 LED 闪烁,它的间隔时间是 1s,如果我们想要仿真这个功能,那么我们仿真软件运行时间最低就是 1s。这 1s 钟在我们看来是很短很短的,不过在仿真软件看来是很长很长的,我们的仿真软件单位可是 ps。为了便于我们仿真,这里我们需要稍微改动一下 Verilog 代码,我们需要将 parameter SET_TIME_1S = 27'd50_000_000;修改为 parameter SET_TIME_1S = 27'd50; 也就是将我们原来的 1s 钟修改成了 1us。修改完毕后,我们在 Quartus II 软件界面中的菜单栏中找到【Tools】→【Run Simulation Tool】→【RTL Simulation】按钮并点击,则会出现如图 2.13 所示界面。 看到这里,也许有的朋友点击【RTL Simulation】并没有出现 Modelsim 仿真窗口界面,而是出现了如图 2.14 所示界面。

看到这里,也许有的朋友点击【RTL Simulation】并没有出现 Modelsim 仿真窗口界面,而是出现了如图 2.14 所示界面。 出现这种错误主要是因为我们前面设置的 Modelsim 路径不对造成的,如何解决这个问题呢?我们尝试将 ModelSim-Altera 路径设置成了 C:altera13.1modelsim_asewin32aloem。这和我们刚刚设置不同的是,我们在路径的最后面添加了一个反斜杠。这时,我们再点击【RTL Simulation】按钮就会出现 Modelsim 仿真窗口界面了,这里我们需要说明的是:有的电脑不添加反斜杠是可以运行的,有的电脑不添加反斜杠是不能运行。在 Modelsim 软件启动过程中,我 们不需要任何操作,它会自动完成仿真,并给出我们所需要的波形,当波形图出现之后,我们就可以查看波形来判断设计功能是否正常了。

出现这种错误主要是因为我们前面设置的 Modelsim 路径不对造成的,如何解决这个问题呢?我们尝试将 ModelSim-Altera 路径设置成了 C:altera13.1modelsim_asewin32aloem。这和我们刚刚设置不同的是,我们在路径的最后面添加了一个反斜杠。这时,我们再点击【RTL Simulation】按钮就会出现 Modelsim 仿真窗口界面了,这里我们需要说明的是:有的电脑不添加反斜杠是可以运行的,有的电脑不添加反斜杠是不能运行。在 Modelsim 软件启动过程中,我 们不需要任何操作,它会自动完成仿真,并给出我们所需要的波形,当波形图出现之后,我们就可以查看波形来判断设计功能是否正常了。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

仿真

+关注

关注

55文章

4536浏览量

138668 -

eda

+关注

关注

72文章

3143浏览量

183781 -

ModelSim

+关注

关注

5文章

175浏览量

49479 -

Quarus

+关注

关注

0文章

4浏览量

6552

原文标题:ModelSim 使用【二】联合Quarus自动仿真

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

网格为王,仿真破界——Altair HyperMesh 重塑CAE工程设计新范式?

的自动识别、网格的智能生成与优化,甚至能基于历史仿真数据进行预测性分析,帮助工程师提前规避设计风险,进一步缩短设计迭代周期。同时,结合GPU加速技术,实现大规模复杂系统的快速仿真,突破

发表于 04-23 14:47

智造引擎,仿真之巅:Altair HyperWorks 重塑工程研发新格局?

求解器,真正做到 “一次建模、多场景分析”,为工程师搭建高效、灵活的数字化研发桥梁。二、核心功能:覆盖全场景,解锁工程仿真无限可能1. 标杆前处理:高效建模,质量与速度双绝依托 HyperMesh

发表于 04-03 14:45

基于 Foster 模型的实战建模:如何在仿真软件中设置 SiC 模块的瞬态热阻参数

基于 Foster 模型的实战建模:如何在仿真软件中设置 SiC 模块的瞬态热阻参数 碳化硅功率模块热管理挑战与瞬态热阻抗建模的工程背景 在现代电力电子工程的宏大图景中,半导体材料的演

华清远见嵌入式全栈工程师实战课重磅升级!一站式掌握STM32+Linux核心技术,仿真教学加持,学习效率翻倍!

嵌入式学习想打通STM32+Linux全栈,却苦于入门难、课程体系不完整、Linux调试难、实战项目少?华清远见嵌入式体系课重磅升级,从课程内容、仿真平台、实战项目三大核心维度全面焕新,原600+

Renesas E1/E20 仿真器使用指南:从基础到实战

Renesas E1/E20 仿真器使用指南:从基础到实战 在嵌入式开发领域,一款高效可靠的仿真器对于调试程序、优化性能至关重要。Renesas 的 E1/E20 仿真器就是这样一款能

少走三年弯路!顶尖硬件工程师分享的“实战锦囊”!

工程师实战能力提升专家——赛盛技术赛盛技术公司专注于提供高质量的工程技术培训服务,以线下公开课、企业内训和线上网课等多元化形式,满足不同工程师的学习需求。课程内容广泛覆盖EMC、硬件设

芯片过热导致锁死?全自动烧录机温控系统的优化实战

。

额外收益:温度日志帮助发现,来自不同封装厂的芯片,其发热特性有细微差异。这为后续的芯片来料质量评估提供了一个新的观察维度。

总结与反思这次优化实战揭示了一个常见误区:全自动烧录机的可靠性,不只取决于

发表于 02-11 09:34

如何使用Modelsim仿真I2C控制器

ModelSim是Model Technology(Mentor Graphics的子公司)的HDL硬件描述语言的仿真软件。该软件可以用来实现对设计的VHDL、Verilog HDL 或是两种语言

ModelSim仿真蜂鸟E203 / 200 教程【功能验证】

一起

把子文件夹里的文件全部复制出来,不要留文件夹

perips这部分也全部挪出去

新建工程

在这

选保存的工作区

添加文件夹的所有文件(work的文件夹不用选)

用modelsim做

发表于 10-27 07:35

语法纠错和testbench的自动生成

设置中:

另外,自动纠错实际上还是用了仿真软件的工具,例如vivado、iverilog、modelsim等。下面介绍如何利用vivado的工具xvlog。

一般情况下,xvlog在vivado

发表于 10-27 07:07

Ansible代码上线项目实战案例

在DevOps浪潮中,自动化部署已经成为每个运维工程师的必备技能。今天我将分享一个完整的Ansible代码上线项目实战案例,让你的部署效率提升10倍!

是德示波器MSOX3104A自动测量功能详解与实战技巧

一、引言 在电子工程、通信调试、自动化控制等领域,示波器是工程师不可或缺的测试工具。是德科技(Keysight)的MSOX3104A示波器凭借其高精度、多功能特性,尤其在自动测量功能上

ModelSim工程实战之自动仿真

ModelSim工程实战之自动仿真

评论