简介

过去几十年来,无线系统通道数和带宽一直稳步增长。对数据速率和系统整体性能的要求成为这些现代电信、雷达和仪器仪表系统发展的驱动因素。但与此同时,这些要求也加大了电源封装和系统的复杂度,使功率密度和组件级别的功能变得更为重要。

为打破其中的一些限制,半导体行业将更多的通道整合到同一个硅封装中,借此降低每个通道的功率要求。此外,半导体公司还将更复杂的功能整合到数字前端,简化了过去在专用集成电路(ASIC)或现场可编程门阵列(FPGA)结构中才能实现的片外硬件设计。这些功能既包括滤波器、下变频器或数控振荡器(NCO)等通用组件,也有更复杂的特定应用操作。

信号调节和校准问题仅在开发多通道系统时才变得较复杂。这种架构可能需要每个通道有独立的滤波器或其它数字信号处理(DSP)模块,从而转变成对节能更为重要的强化型DSP。

本文介绍了使用16通道发射和16通道接收子阵列的实验结果,其中所有发射和接收通道都使用数字转换器集成电路(IC)中的强化型DSP模块来校准。与其它架构相比,这个多通道系统在尺寸、重量和功率上都更有优势。对比该系统的FPGA资源利用率后可发现,强化型DSP模块为多通道平台的设计人员解决了重大挑战。

数字信号处理模块

真实信号,无论是用来合成还是接收,都需要一定程度的分析或处理,才能共同满足任何应用所需的性能。信号链幅度衰减或平坦度的常见补偿办法是借助补偿滤波器。图1是增益和平坦度补偿滤波器的示例,设计用于校正给定频段内的缺陷,从而为下游应用创建更理想的响应。

图1.ADC的频率幅度平坦度响应可通过数字滤波来改善

对多通道系统而言,此处理必须能够独立控制每个通道,让通道彼此独立地运行。因此,该系统使用的是独立的DSP模块,可进行通道的相位和幅度对齐,还可在目标通带内获得平坦增益。由于每个通道和系统都是唯一的,DSP必须针对配置、环境和硬件组合专门调谐。

数字上/下变频器模块

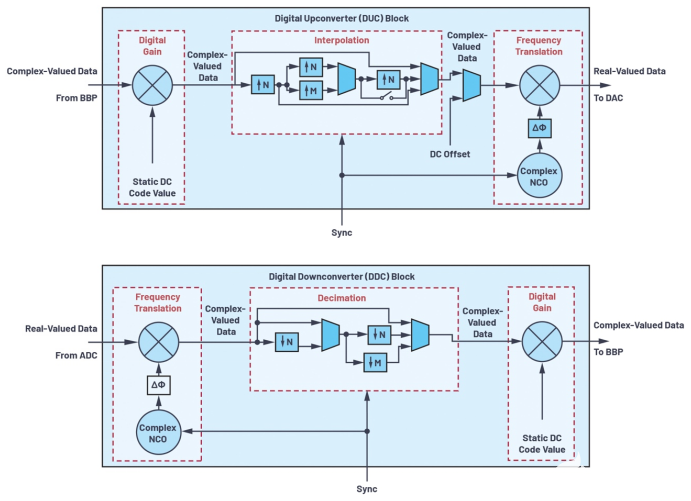

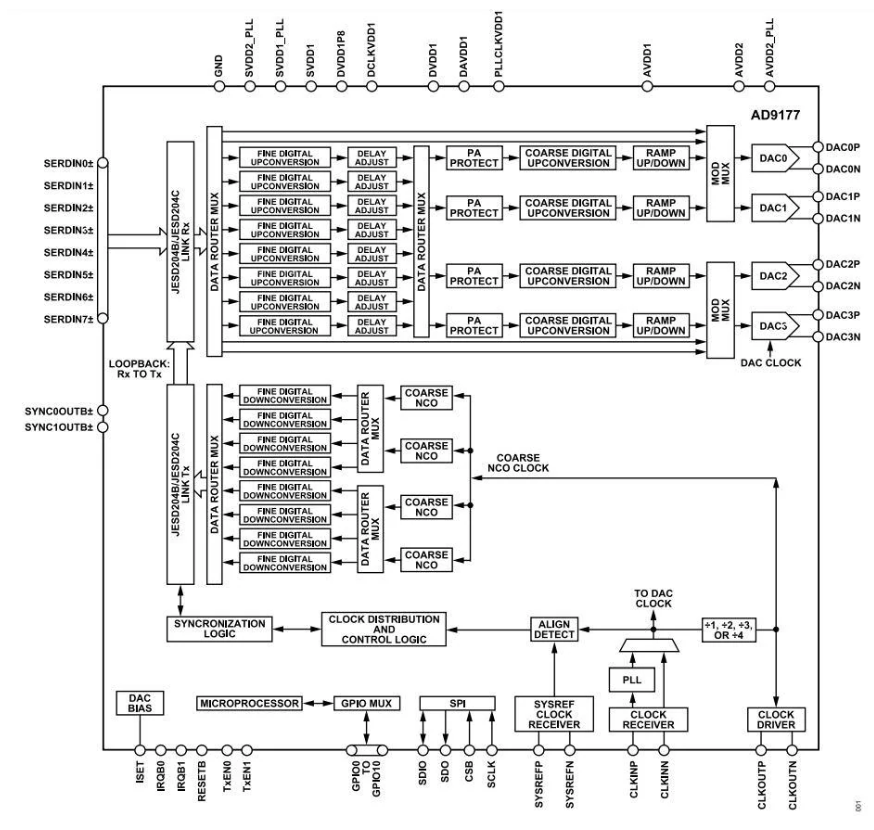

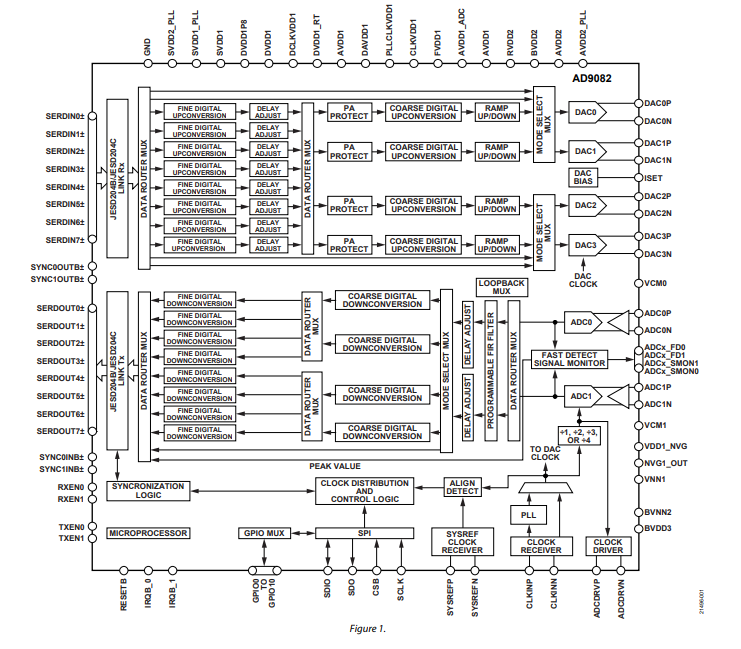

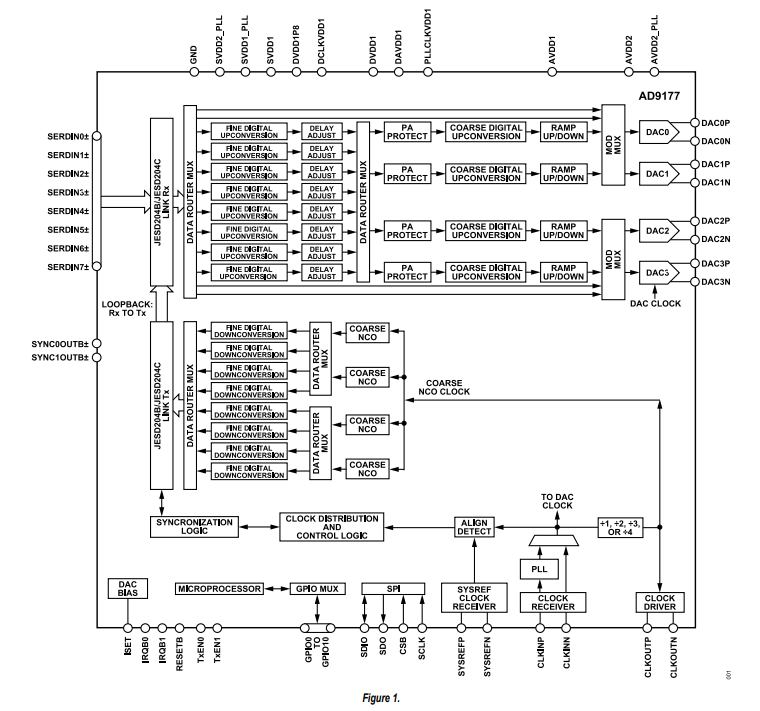

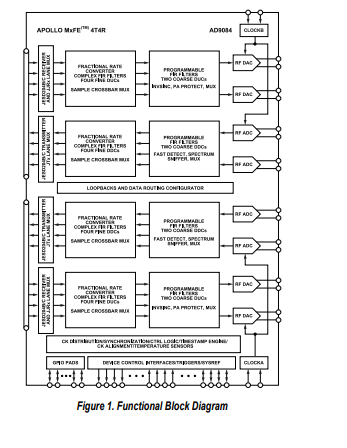

本文的结论主要依赖单芯片DAC和ADC中配置的数字上变频器(DUC) DSP模块和数字下变频器(DDC) DSP模块。图2是DUC和DDC框图示例,说明了这些数据通道常用的内部结构。这些DUC和DDC模块有许多用途:

与数字接口的数据速率相比,内插(DUC)和抽取(DDC)转换器的采样速率。

转化即将合成的DAC数据(DUC)和数字化ADC数据(DDC)的频率。

将接口的数字数据发射导向基带处理器(BBP)。

为每个通道实现数字增益,产生更接近系统满量程值的码值。

支持注入简单的数字音调,无需数字数据链路,便能简化系统快速启动。

将每个通道的相位对齐通用基准。

我们往往希望卸载到转换器或从转换器卸载的数字数据速率与转换器的采样速率不同,从而降低系统功耗,提高系统的整体灵活性。因此,通常会部署数字上变频器和下变频器模块。DUC模块使来自BBP的发射波形数据能够以低于DAC采样速率的速率发射,因此也支持DAC以更高的速率合成内插波形数据(见图2顶部的内插子模块)。同样地,DDC模块使接收输入在抽取前以更高速度的ADC采样速率数字化,之后再以更低的数据速率发送到BBP(见图2底部的抽取子模块)。

此外,与通过数字接口发送到BBP或从BBP发送出的信号相比,频率转换在数字域内常用于合成或分析更高频率的模拟信号。许多系统都在DUC和DDC中采用复值NCO,目的就是为了实现这种频率转换,如图2所示。NCO可被认为是数字信号生成器,它能提供等同于本振(LO)的信号,当信号被发送到同样在DUC/DDC中的数字混频器中时,可以提高发送到DAC的发射波形频率(和DUC的情况一样),或降低从ADC发出的接收波形频率(和DDC情况一样)。当数字频率转换发生时,DDC内这些数字混频器的输出往往变成复值,使得同相位(I)和正交相位(Q)信号沿着最终连接到单独ADC采样实值数据的单一数字通道传输。同样地,到达DUC数字增益模块数字混频器的输入复值信号在输出端变成实值,然后签发到单独DAC,合成实值信号。

图2.DUC和DDC模块提供目前转换器IC中许多有用的DSP功能

此外,DUC和DDC还使用户能够在转换器的瞬时带宽内获得多个数字通道。结果就是BBP能够合成和/或分析比子阵列本身的转换器数量还要多的数据流。因此,如果两个窄通道彼此隔得很远,就需要能提供更好的信号合成或分析能力的系统。

正如图2所示,数字增益模块也经常出现在DUC和DDC中。数字增益通过向子模块中另一个数字混频器的输入提供静态数字码值来实现。利用这个功能,用户获得的码值更接近数字接口位数所提供的满量程值。同样地,只要向数字混频器的一个端口提供连续静态码值,便可注入直流偏移连续波(CW)波信号,而非基带数据。这样用户就能通过DAC将发射CW波轻松合成至模拟域,无需通过BBP建立JESD204B或JESD204C数据链路。

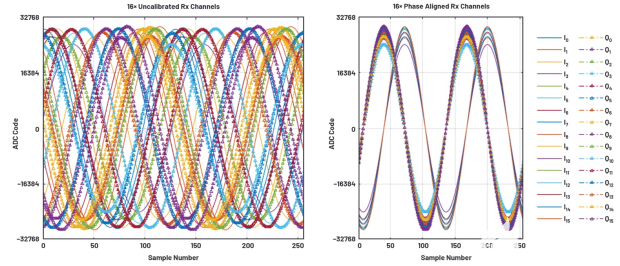

此外,相位偏移模块经常部署在NCO的输出,如图2所示。这些相位偏移可按照系统内的通用基线参考来校正通道间相位偏差。由于每个DUC和DDC都有自己的NCO,因此只需针对给定的NCO频率来偏移一个确定量的NCO相位,便可实现系统每个通道的相位对齐。这样一来,在使用时遇到可用的多芯片同步算法时,所有通道间的确定性相位关系可通过这些NCO相位偏移进行校正1。 图3显示了实现相位对齐(通过严格为每个接收数据通路设置所需的NCO相位偏移值)前后,16通道同时接收I/Q数据采集的实验结果。请注意,这些数字校正还校正了每个通道前端网络中的射频和微波损耗。

可编程有限脉冲响应滤波器

尽管NCO输出相位偏移模块可被用于单一频率的相位对齐,子阵列校准则经常要求对整个目标频带进行相位对齐。此外需要幅度均衡,即所有通道名义上拥有相对于通用基准通道的相同幅度,还需要幅度增益平坦化,即所有通道拥有相对于频率的恒定幅度响应。

为达到宽带相位和幅度校正,通常还部署另一种DSP模块。这种模块被称为有限脉冲响应滤波器(FIR)2。 FIR滤波器是一种数字滤波器,被大量用在DSP上,其系数决定了输入数字信号的幅度和相位响应。允许更改这些系数的系统被视为可编程FIR滤波器(pFIR),用户可根据每个通道生成自己需要的幅度和相位响应。

运用pFIR实现通道幅度对齐和增益平坦化

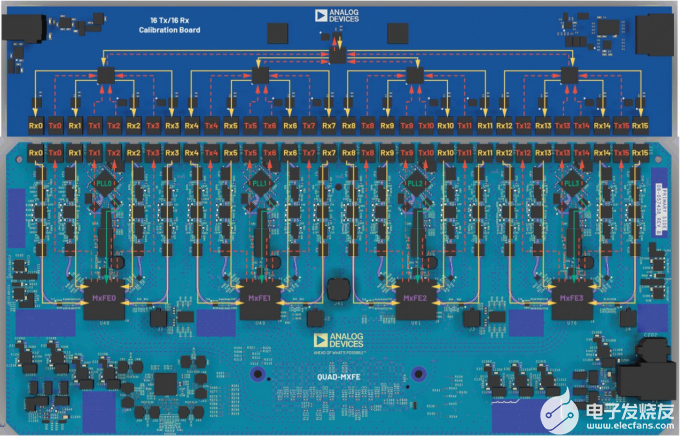

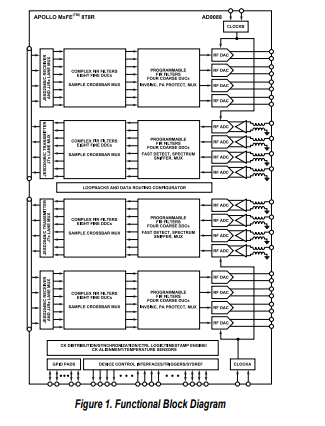

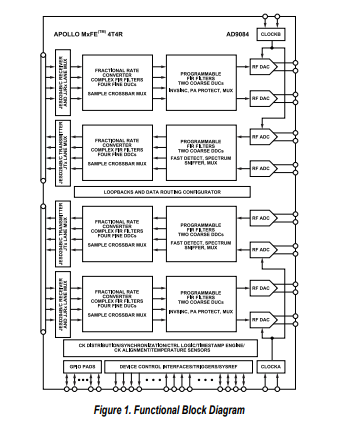

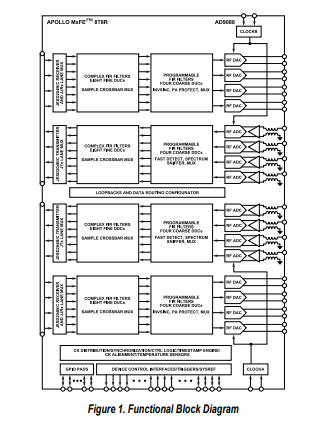

图4是用于展示宽带幅度和相位对齐以及增益平坦化的系统的高级框图。该系统采用了四个数字化IC,各包含四个发射和四个接收模拟通道,或者八个发射和八个接收数字通道。当使用系统内的所有四个数字化IC时,总共可实现16个发射和16个接收模拟通道,或者32个发射和32个接收数字通道。单独的锁相环(PLL)频率合成器IC用于给每个数字化IC提供转换器采样时钟信号。此外,时钟缓冲器IC用于提供多片同步算法所需的数字参考和系统参考时钟1。 该系统起初配置在S频段,设定NCO频率,所有发射和所有接收通道的模拟信号频率都在同样的2.7GHz。所用的DAC采样速率是12 GSPS,平台会在第一奈奎斯特区合成发射通道。ADC采样速率为4 GSPS,平台会在第二奈奎斯特区采集接收通道。

图3.实验结果表明了16个接受通道的I/Q同时采集,利用数字化仪IC上的

DDC模块提供的复杂NCO相位偏移严格进行相位对齐(而非幅度对齐)。

图4.这个高级系统框图用于证明多通道相位和幅度均衡/平坦度

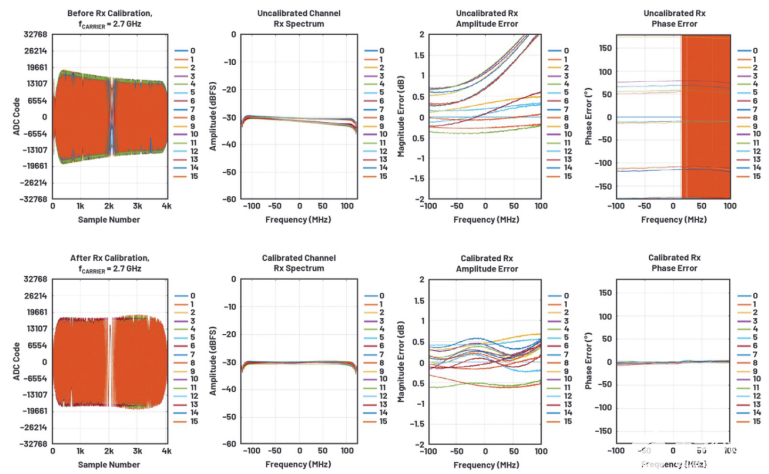

如图5所示,用连接的16发射/16接收校准板将组合通道发射信号准确地回送到每个单独的接收通道,以便同时采集所有接收通道。系统的PLL频率合成器再通过自身相位调整模块对齐,发射通道和接收通道则使用DUC和DDC各自提供的NCO相位偏移模块粗略对齐。这样一来,子系统相位大致与校准频率对齐,见图3所示曲线,但未实现任何幅度对齐。尽管本文采用了16发射/16接收校准板,用电气方法对齐系统,但还可通过系统校准反射器以无线方式获得类似的配置,这也有助于校正任何天线通道间异常。

如图4所示,96抽头pFIR滤波器位于每个ADC的输出,这样每个ADC通道的相位和幅度响应可在整个ADC采样速率的频率范围内彼此对齐。因此可将pFIR放在ADC和DDC模块之间。这样数字接口的数据速率就不同于pFIR的速率,所以需要知道系统频率转换和速率抽取的程度,以便采用pFIR进行通道幅度对齐。由于本文在每个ADC的输入端采集实际数据,pFIR输入为实值。此外,系统设计是可配置的,这样每个ADC对的一个pFIR模块就是已部署的解决方案,如图4中的双重实际模块所示。这也允许在两个独立的ADC中使用I/Q复杂输入,从而支持系统对齐。

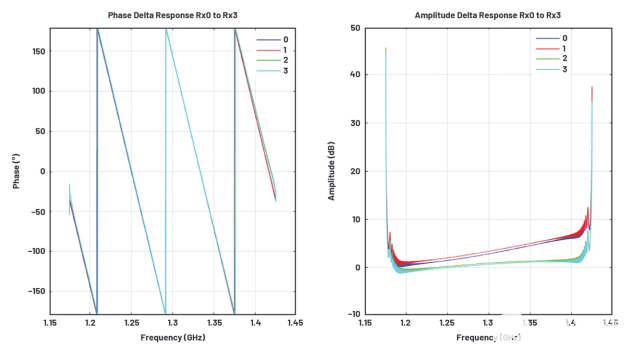

为实现系统内通道的幅度对齐和幅度平坦化,将宽带扫频波形载入每个发射通道,使得系统的I/Q带宽中包含所有频率。这样用户就能确定系统数据速率内所有频率的频率误差响应。然后,在抽取的I/Q数据速率下获得基线数据采集。本文的结论使用的是4 GSPS的ADC采样速率和250 MSPS的I/Q数据速率。这样每个发射NCO频率设置为2.7 GHz,每个接收NCO频率设置为1.3 GHz,原因是频率从第二奈奎斯特区折叠到第一奈奎斯特区。基线数据利用MATLAB?系统接口采集,针对增益平坦化Rx0计算每个通道的幅度和相位误差响应,这样所有接收通道收到的最大值就是整个I/Q频段的理想接收输入。图6显示了系统内16个接收通道中四个通道的相位和幅度误差响应。注意图6左侧,NCO相位偏移主要校正每个接收通道的相位误差,但正如图6右侧所示,系统中的幅度误差仍在。剩余的12个接收通道也有同样的误差响应。另外应注意,不仅接收幅度不同于Rx0,如果不使用其它校准技术,幅度平坦度也很差。这些异常是在ADC前端网络中使用模拟滤波器时故意引入的,以便证明幅度平坦度和均衡。

图5.测试设置了输出发射(红色)信号,然后利用连接的16发射/16接收校准板组合所有发射信号。再将组合后的信号进行均匀拆分,并回送到每个接收(橙色)通道。16发射/16接收校准板位于图片顶部,与本文使用的独立Quad-MxFE?平台对接。PLL/频率合成器信号(绿色)经过调整后可校正平台上故意引入的热损害。

图6.每个通道相对于增益平坦Rx0的相位/幅度误差响应有助于确定pFIR滤波器设计

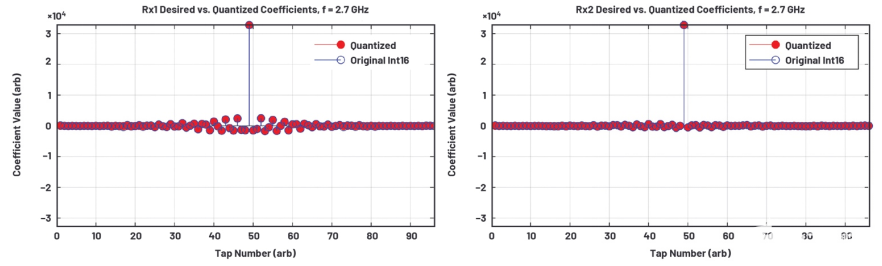

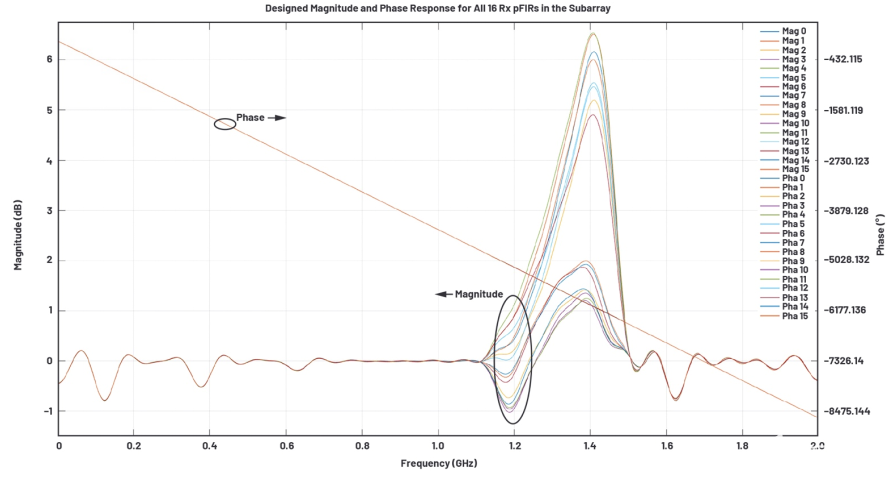

因此,为改进幅度对齐和幅度平坦度,根据每个通道相对于增益平坦Rx0的复值误差响应设计实值96抽头任意幅度和相位pFIR。应注意,pFIR设计算法更注重较窄目标I/Q波段的误差响应。但是,完整的pFIR设计覆盖更广的全速率ADC奈奎斯特区,强制处于250 MHz子带以外的区域使用统一的通带响应。因此,本文中,集中在接收NCO频率(1.3 GHz)的250 MHz子带对pFIR设计而言比奈奎斯特区的剩余频率更重要。这些pFIR采用MATLAB中DSP System Toolbox的滤波器设计功能,但同样的算法也可用到现场系统的强化型数字电路中。图7显示了本文实例所用16个接收通道中两个通道的96抽头pFIR滤波器。剩下来的14个接收通道的pFIR设计相似。图8显示了针对子阵列中所有16个接收通道设计在全奈奎斯特区的pFIR幅度和相位响应。

必须注意,pFIR设计算法通常使用介于0到1之间的连续值系数空间。但是,硬件要求量化这些持续值系数,且必须位于系统可用的特定位宽内。系统为pFIR系数空间采用不同的位宽,这样一来,一些系数是16位,一些是12位,还有一些只有6位。此外,12位系数必须在16位系数的旁边。如图7中的系数值所示,只有更大值的系数需要16位,更小值的系数只需要6位。但是,只要对理想的滤波器系数进行量化,都要引入量化误差,应注意最小化本文中的这种量化误差,设计的系数仍需拟合可用的系数空间。

量化完成后,借助数字化仪IC应用程序编程接口(API)功能,将pFIR系数载入每个通道。本文通过API使用串行外设接口(SPI)通信来修改每个通道的系数。但如果有必要,也可以使用专用的通用输入/输出接口(GPIO)信号在不同系数库间进行更快切换。

图7.单独96抽头pFIR旨在提供子阵列内的增益平坦和幅度对齐

图8.针对所有接收通道设计的pFIR频率响应显示了每个通道应用的校准响应

图9.为每个接收通道部署pFIR改进了相对于Rx0的幅度均衡和幅度平坦度

最后,获得后续接收数据采集,同时启用pFIR来分析pFIR设计的有效性。图9顶部显示了启用pFIR前的结果。应注意,在幅度均衡步骤前,16个接收通道在感兴趣的频率范围内有不同的幅度和相位。还应注意,八个接收通道的幅度平坦度响应与另外八个的不同。但在为每个接收通道设计和启用pFIR后,如图9最下方所示,所有接收通道的幅度在名义上实现了I/Q带宽内的幅度均衡、幅度平坦以及相位对齐。幅度和相位均衡还可以通过更精细的pFIR设计实现改进,但这超出了本文的范围。

数字化元件资源消耗与FPGA资源消耗

如上所述,片上强化型pFIR在抽取阶段前就存在于ADC数据通路中。正如演示的,这些pFIR为用户提供了重要的应用灵活性,但由于这个功能被卸载到数字化IC本身,因此它还使开发人员能够大大减少FPGA资源。问题就变成:为什么要在数字化IC上而不是在FPGA的硬件描述语言(HDL)结构中使用强化型pFIR?这可以从几个方面来回答:资源减少、设计复杂性和功耗。

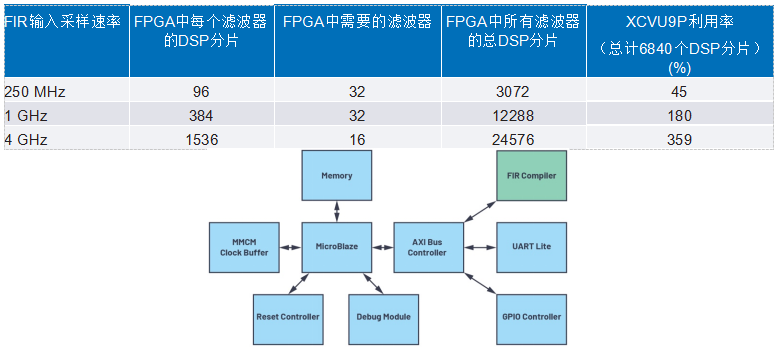

无论关注的领域是什么,资源减少向来都是一个重要的话题。数字化IC已经创建并安装了强化型pFIR模块。在FPGA中,可以从DSP分片上建立FIR滤波器,这些DSP分片包含特定的FPGA构造元件,意在提供DSP功能。FPGA DSP分片不同于传统的逻辑门,比如触发器,它会单独计入FPGA资源利用率。要确定pFIR应用于数字化IC还是FPGA,FPGA的利用率——特别是DSP分片的利用率——变得至为重要。为了作对比,所选的VCU118平台包含一个由6840个DSP分片组成的XCVU9P Virtex? Ultrascale+? Xilinx? FPGA。虽然DSP分片的数量已经相当可观,但在确定结构中到底要放置多少个滤波器时,还必须考虑通道的数量。

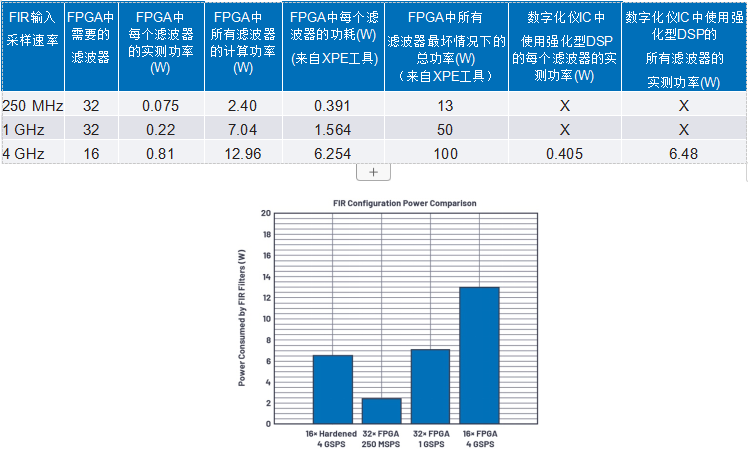

为此,必须知道滤波器所需的输入采样速率。表1显示了在FPGA上合成一个FIR设计时所需的估计资源数量,针对的是能映射潜在数字化IC数据通道配置的几个应用场景。这些为每个滤波器估计的资源来自Xilinx LogiCORE? IP FIR Compiler 7.2模块摘要。为了查看这个概要,向Xilinx Vivado? Design Suite 2018.2创建的简化MicroBlaze?设计添加了滤波器,如图10所示。250 MSPS和1 GSPS速率的情况是FIR将使用从变频器抽取的数据来运行,而4 GSPS的情况则是假设数据直接来自变频器的未抽样输入。每个FIR滤波器的运行速度为250 MHz,以便模拟FIR滤波器在基带数据通道中的运行速度,并且包含96个16位可重载系数。

鉴于XCVU9P FPGA的利用率,很显然必须要用一个更大的FPGA,比如XCVU13P(包含12,288个DSP分片),来包含所有需要的滤波器。对于4 GSPS FIR滤波器这种情况,需要至少两个XCVU13P设备来分担所有滤波器的资源负载,这相应地减少了设计成本。相比之下,上文提到的用于强化型DSP pFIR部署的全部16个通道需要的所有滤波器全部包含在数字化IC本身中,目的是为了降低系统设计方法的复杂性。

表1.提高FIR采样速率导致FPGA资源利用率超出现有能力,显著增加了系统功耗

图10.具有一个FIR滤波器的MicroBlaze设计在FPGA中启用以确定资源利用率

FPGA中FIR的另一个主要问题是设计的复杂性,这与DSP分片资源利用率高有关。考虑如何构建滤波器。在硅片上,滤波器的设计被固定在芯片的单个位置,但系数和权重可以通过数字方式改变,从而实现一个相对静态的执行。在FPGA结构中,FIR滤波器设计规定了那些DSP分片在芯片不同区域的布线。这意味着随着滤波器的增加或变动,会消耗FPGA更多的区域,DSP分片之间的布线连接也变得越来越具有挑战性。其次,扩展FIR滤波器设计可能会影响FPGA设计其余部分的布线,这会使时序关键布线变得很难,虽然在某些情况下并非不可能。

数字化元件功耗与FPGA功耗

行业总体趋势是提高变频器的采样速率和多通道集成,这往往要求系统架构师在整体设计中实施DSP模块时能分析系统功耗。过去这些DSP模块通过可编程逻辑来实施,如FPGA中可看到的。但是,在FPGA内实施可配置模块通常会产生过多的整体系统功耗。

为了尝试直接比较两个系统,我们为VCU118创建了几个简单的参考设计,目的是为了确定基于FPGA的滤波器方法在实际场景中功耗的相对差异。之所以选择VCU118,因为当时它在Xilinx直接提供和支持的评估系统中拥有最多的DSP。基于VCU118,针对每个FIR输入采样速率创建了两个Vivado项目:一个有滤波器,一个没有。对于250 MHz和1 GHz这两种情况,在设计中插入了八个FIR滤波器,如图10所示。在4 GHz情况中,由于资源利用率高,设计中只插入了两个FIR滤波器。每个滤波器使用输出Xilinx LogiCORE DDS Compiler 6.0模块馈送,以便确保使用的是有效数据。另外必须注意,在合成后要检查RTL,以便验证设计中保留了滤波器,确保它们没有被优化掉。在针对每个采样速率的第二个设计中,滤波器被移除,但所有其他IP模块保留。

实施后启动设计,采用电流测量创建一个相对功率偏差,以便隔离滤波器所需的额外功率。滤波器的电流消耗见表2每个滤波器的测量功率一栏。再通过设计中为数量有限的滤波器(八个滤波器用于250 MHz和1 GHz,以及两个滤波器用于4 GHz)采集的数据推算出所有滤波器的总功耗。这个偏差是对比的基本单位,用于扩展到VCU118无法实施,但数字化仪IC可以实施的不同配置。作者认为,这对FPGA来说相对公平或可能有利,因为一个实际系统的功耗不可能会线性扩展。最后,将结果与Xilinx功耗估计器(XPE)工具为各种滤波器生成的功耗估值进行对比3。功耗估值远远高于推测的结果,但这也说明利用率提高造成的功耗是非线性增长的。

为了比较FPGA中FIR和数字化仪IC中的强化型pFIR的功耗,我们将简单的滤波器设计测量的结果与多通道系统的实际电流消耗进行了比较,多通道系统使用数字化仪IC上的强化型pFIR DSP模块。包括所有前端网络和时钟电路在内,使用未启用强化型pFIR的数字化仪IC平台的总系统功耗大约为98.40 W。如果所有16个强化型pFIR都启用,使用数字化仪IC平台的总系统功耗大约是104.88 W。因此,在多通道平台使用强化型pFIR导致的功耗偏差总共约为6.48 W,包括了数字化仪IC系统上的所有16个接收通道。强化型pFIR直接接收来自ADC的数据,其运行速度必须为当前一代的ADC采样速率(4 GSPS)。

表2.提高FIR采样速率会导致系统功耗增加

图11.数字化仪IC中的强化型DSP模块改善了系统级功耗

但将这种功耗与假设有16个4 GSPS FPGA FIR的功耗作对比有点不切实际,因为对单个Virtex Ultrascale+系列FPGA而言,其资源利用率不可能很高。因此,将250 MSPS速率的FPGA FIR与强化型4 GSPS pFIR作对比,表2和图11显示了32个FPGA FIR(16个I FIR和16个Q FIR)的功耗是2.40 W。FPGA中的滤波器的运行速度比强化型数字化仪IC DSP模块中的慢16倍多,但FPGA的功耗仍是强化型数字化仪IC功耗的0.37倍。将32个1 GSPS FPGA FIR与强化型4 GSPS pFIR相比,FPGA FIR的功耗约为7.04 W(其功耗要比强化型pFIR的高得多),运行速度则比强化型pFIR的慢4倍。将16个4 GSPS FPGA FIR与16个强化型4 GSPS pFIR作比较,FPGA的功耗是这个系统配置的2倍。总之,图11表明数字化仪IC中强化型pFIR的功耗要低于相应的FPGA FIR滤波器的。此外,强化型pFIR降低了FPGA DSP片的利用率,这也降低了设计的复杂性和总功耗。利用更高速率的滤波器拓宽了250 MSPS滤波器数据速率不可能降低时的宽带应用场景。

最后要考虑的一个因素是在过度依赖FPGA资源的设备中(如数字化仪IC AD9081)利用强化型DSP的可扩展性。在许多应用中使用16个通道,也许只是最终系统的一个小子阵列。对许多利用强化型DSP(如AD9081中)的系统集成商而言,与通过增加FPGA资源拓展后端处理相比,可以得到更灵活的规模级解决方案以及更简单的信号链。关于这个争论,作者主要考虑了拥有中央处理模型的系统,其中所有数据最终必须聚集到单个FPGA中。在这种情况下,随着通道规模的扩大,向更多的数据变频器增加内置滤波功能就需要更多的SERDES线路,从架构方面看,管理很简单,因为并不需要更多FPGA资源。没有这些强化型DSP功能,系统集成商就需要连接多个FPGA,以便针对同样的应用获得必要的资源,情况会非常复杂。

结论

本文介绍了一个在单片数字化元件IC中整合DSP模块的系统,并用具体的例子证明了这些数字化模块可以提供相控阵、雷达、卫星通信和电子战应用所需的多通道幅度和相位均衡。一种采用pFIR数字滤波器和DUC/DDC NCO相位偏移的方法表明,无需将这些DSP模块整合到FPGA中,也可实现多通道宽带均衡。用来进行这种验证的系统见图12,称为Quad-MxFE Platform4 ,可从ADI公司购买。明确来讲,AD9081 MxFE IC已经成为子阵列设计的主干。Example HDL、MATLAB脚本和用户证明文件可在ADQUADMXFE1EBZ产品维基页面(ADI公司2020)上查看。16发射/16接收校准板(ADQUADMXFE-CAL)也已开售。仪器仪表和5G市场也许会对这些技术在子阵列测试和测量或基站开发方面的运用感兴趣。

图12.Quad-MxFE平台可从ADI公司购买

-

adc

+关注

关注

100文章

7453浏览量

553933 -

数字滤波器

+关注

关注

4文章

299浏览量

48046

发布评论请先 登录

多通道ADC数模转换器电池管理系统解决方案

Analog Devices Inc. AD9177 16位数模转换器(带宽带信道发生器)数据手册

STM32多通道FFT运算异常的原因?怎么解决?

AD9082四通道16位12GSPS RFDAC和双通道12位6GSPS RFADC技术手册

AD9088八通道、16 位、16 GSPS RF DAC和八通道、12位、8 GSPS RF ADC技术手册

AD9084 Apollo MxFE四通道、16位、28 GSPS RF DAC和四通道、12位、20 GSPS RF ADC技术手册

AD9177具有宽带信道选择器的四路、16位、12 GSPS RF DAC技术手册

AD9088 Apollo MxFE 八通道、16位、16 GSPS RF DAC和八通道、12位、8 GSPS RF ADC技术手册

AD9084 MxFE 四通道、16位、28 GSPS RF DAC和四通道、12位、20 GSPS RF ADC技术手册

ADC/DAC IC上的集成强化型DSP改进宽带多通道系统

ADC/DAC IC上的集成强化型DSP改进宽带多通道系统

![AN-283: Σ-Δ<b class='flag-5'>型</b><b class='flag-5'>ADC</b>和<b class='flag-5'>DAC</b>[中文版]](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

评论