在多个第三方IP核、外部接口和低功耗设计驱动下,数十亿门级的专用集成电路(ASIC)已具备几十甚至数百个异步时钟域,而要解决跨时钟域(CDC)问题,RTL仿真和静态时序分析(STA)都不是最理想的解决方案。

对数字开发者而言,CDC问题主要源于以下四种常见的跨时钟域场景。

如果没有合适的时钟同步器,由异步时钟域之间的抖动引起的亚稳态可能会导致功能故障。此外,设计中还存在更复杂的路径和场景,例如多条同步后的路径经过组合逻辑汇聚在一起可能会由于同步器的不确定性而导致时序不匹配。此类缺陷通常无法在流片前解决,因此出错后可能会导致芯片设计返工,从而付出高昂的代价!

CDC验证是流片前的关键签核标准。那么要实现这一标准,ASIC开发团队将会面临哪些挑战呢?

周转时间

CDC违规清零是芯片签核的必要条件。

解决CDC问题的难度与芯片的设计规模成正比。在数十亿门级的ASIC设计中可能存在数百个异步时钟和数百万个跨异步路径。开发者通常需要消耗万亿字节内存,并花费数天时间才能完成全芯片的扁平级CDC分析。在此过程中,周转时间非常重要。

在进行CDC分析时,开发者们可采取自下而上的分层分析法,就像进行综合和静态时序分析那样,每次分析一个模块,逐个模块解决CDC错误。在向上一个层级移动的过程中,开发者们可以用抽象的CDC模型替换CDC违例已经清理干净的模块。这一模型将只包含与上一层相关的时钟路径,而不考虑所有内部跨异步路径,每清理完一个层级,就会继续进行下一层级的CDC清理,以此类推。

通过这种方式,CDC分析可左移到开发流程的早期阶段,而无需等到流片前才完成。如果在临近流片时还在修复CDC错误,会对设计造成极大的破坏性,代价极其高昂!

新思科技VC SpyGlass CDC拥有CDC签核以及层次化验证流程,采用高效的分层方法,在不改变结果质量(QoR)的情况下,减少了内存需求,将周转时间提高至少3倍。

误报问题

CDC分析的另一个重大挑战是误报问题。

当设计中有数以百万计的CDC跨异步路径时,出现的违例数量也会非常庞大,那么要确定问题究竟出在哪就会如同大海捞针一般,非常困难,这就导致开发者可能会遗漏一些十分重要的CDC违例从而没有进行bug修复。因此,对于大型ASIC开发者来说,CDC分析十分棘手。

幸运的是,数据科学为我们提供了解题思路──机器学习(ML)技术可以成为解决这一问题的关键。ML技术可以根据问题根源对违例行为进行分类,我们会发现,很多违例行为都可以归因为同一个问题,且归类的前五大问题几乎可以覆盖95%以上的违例行为,只要解决这五大问题,就可以极大减少违例误报,对开发者来说,发现并解决剩余5%的问题也将容易不少。

VC SpyGlass CDC通过采用ML技术对违例误报执行根本原因分析(RCA)来解决误报问题。这种ML RCA方法不仅可以分门别类地识别违例,还可以通过调试线索提示根本原因,助力开发者高效找到解决方案。例如,由于缺少同步机制,开发者们可以通过更改RTL来纠错,但更常规的做法是对CDC约束文件进行优化或补充。这种约束优化过程能够快速迭代,大幅减少违例行为,并快速识别需要在设计中修复的真正的CDC问题。

约束是否正确

CDC分析是由约束驱动的,约束由开发者编写,不正确的约束可能会导致不正确的CDC分析,比如约束错误可能会导致真正的CDC违例没有被发现,因此没有被修复并最终导致流片失败。当芯片设计中需要输入约束文件(如新思科技设计约束(SDC)文件)时,检查这些输入文件的正确性至关重要。确保这些约束文件正确的方法之一是将约束转化为断言并把他们放到动态仿真环境里去验证。这种方法将为开发者们提供更高级别的约束验证。

豁免是否正确

除约束外,还可以运用违例豁免。豁免也是CDC分析工作流所需的输入文件,通过分析手动生成。错误地运用豁免可能会导致CDC的真实错误被掩盖。即使豁免最初是正确的,但为解决功能或性能问题,开发者也可能需要修改RTL或网表ECO。在这种情况下,开发者需要对豁免进行核查,因为之前有效的条件可能不再成立。

更困难的收敛问题

大多数CDC问题都可以进行静态结构性分析,但在某些情况下动态分析也是有必要的,比如在设计中存在很复杂的汇聚问题,尤其是时序汇聚深度很深并且工具默认检查深度不够的话,就会遗漏这类问题。

所以比较好的解决办法是使用亚稳态注入进行仿真。VC SpyGlass CDC将生成亚稳态模型的CDC数据库,该数据库将在仿真运行时动态注入随机抖动。

新思科技的VCS仿真可在运行时进行本地数据库读取,新思科技的Verdi自动调试系统可以对故障进行调试,并对亚稳态注入信号进行监控,生成覆盖率报告注入了多少次亚稳态抖动。

处理第三方IP核

大多数数十亿门级ASIC会集成多个第三方IP核,这些IP核可能提供了CDC约束,但没有提供签核CDC抽象模型。开发者们肯定不希望对所有IP核都进行扁平化CDC分析,因此开发者们可以针对IP生成其对应的SAM 抽象模型并把它集成到顶层的CDC验证流程。

调试效率

与验证一样,调试工具的有效性也会极大地影响开发者的工作效率。以CDC调试为例,最有效的解决方案是将良好的图形可视化与波形分析相结合。此外,熟悉的调试环境和在多个验证平台使用统一的调试工具对开发者来说也十分重要。新思科技的Verdi调试器能够确保跨平台一致性,提高CDC的调试效率。

如何处理MBIST

最后一个要考虑的问题是如何处理MBIST插入。

MBIST通常在产品开发生命周期要结束时完成,可能占最终设计总逻辑的3%左右。MBIST的插入可能会导致芯片设计中CDC跨异步路径大幅增加。这一点在流片前的CDC签核过程中一定不能忽略。开发者们可以先单独对MBIST做CDC分析,清理CDC违例,之后再插入MBIST,从而减少设计迭代。

结 语

VC SpyGlass CDC是新思科技在Verification Continuum平台上集成的静态分析解决方案之一,可提供全面的CDC签核方法,实现高效能、大容量和高调试效率。该方法原生地与VCS仿真工具等其他工具协同工作,并通过与Verdi调试器集成为开发者们提供高效的调试体验。

原文标题:CDC验证:数十亿门级ASIC设计的最大挑战之一

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

芯片

+关注

关注

463文章

54378浏览量

468988 -

集成电路

+关注

关注

5463文章

12669浏览量

375607 -

asic

+关注

关注

34文章

1277浏览量

124928

原文标题:CDC验证:数十亿门级ASIC设计的最大挑战之一

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

没有研发团队时,手电项目灯珠方案一般怎么推进?

Questa One 智能验证:释放人工智能在功能验证中的潜力

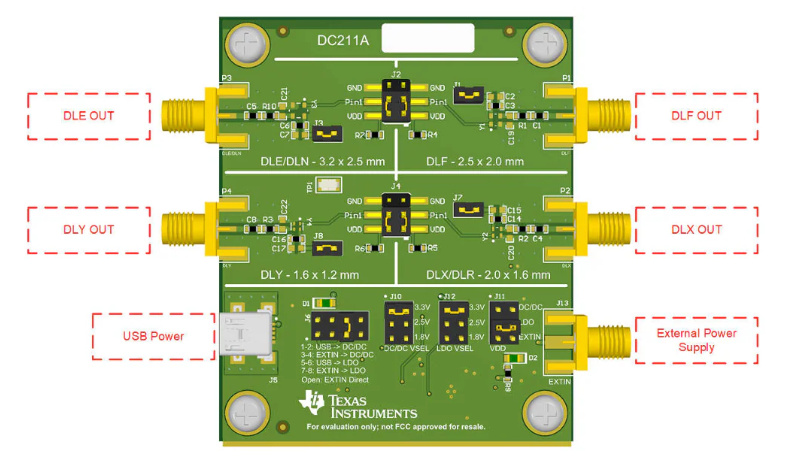

探索CDC516:高性能3.3V锁相环时钟驱动器

Texas Instruments CDC351/CDC351I 时钟驱动器:特性、参数与应用详解

芯片可靠性面临哪些挑战

告别资源瓶颈与漫长周期:覆盖自动驾驶全研发周期的SiL验证方案

开发无线通信系统所面临的设计挑战

【「AI芯片:科技探索与AGI愿景」阅读体验】+AI芯片的需求和挑战

技术解读 | 光庭信息虚拟ECU技术赋能SOA化MCU软件的早期验证与集成加速

开芯院采用芯华章P2E硬件验证平台加速RISC-V验证

Texas Instruments CDC6CEVM评估模块数据手册

要实现CDC验证标准,ASIC开发团队将会面临哪些挑战

要实现CDC验证标准,ASIC开发团队将会面临哪些挑战

评论