作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果BWJIT并非最佳选择,首先要做的仍是寻找最优环路带宽。

图1中,锁相环(PLL)与压控振荡器(VCO)噪声交叉处的偏移,BWJIT(约为140kHz)通过减少曲线下方的面积来优化抖动。

尽管此带宽BWJIT对抖动而言是最优的,但对于相位噪声、锁定时间或杂散却并非如此。表1给出了环路带宽对这些性能指标的影响的大致参考。

| 性能指标 | 最优带宽 | 备注 |

| 抖动 | BWJIT | 最优值一般为BWJIT。在低集成限制更高的一些情况下,有时较窄的环路带宽实际上效果更好。 |

| 锁定时间 | 无限 | VCO锁定时间随着环路带宽的增加而提高,但有时会受到VCO校准时间(用于集成VCO)的限制,或因VCO输入电容等寄生电容而使带宽无法增加。 |

| 杂散 | 0Hz | 一般而言环路带宽越窄,杂散越好,但有时会由环路滤波器周围来自主板或芯片上的串扰所主导。 |

| 相位噪声 | 0Hz或无限 |

如果相位噪声低于最优抖动带宽,相位噪声会随着带宽的变宽而增大,直到变成仅为输入基准和PLL造成的噪声。 如果相位噪声偏移大于最优抖动带宽,相位噪声会随着环路带宽的变窄而增大,直到变成仅为独立的VCO噪声。 |

表1:环路带宽对关键参数的影响

为了说明表1,图2中的模拟显示了变化的环路带宽的影响。锁定时间与抖动标准化指标为图2中从最小值增加的百分比。杂散与相位噪声指标为图2中从最小值增加的分贝。

如图1所预测,环路带宽为140kHz左右时,最优抖动确实为最佳。环路带宽超出此范围会有利于锁定时间和10kHz相位噪声,但是会降低杂散和1MHz偏移的相位噪声。

因此,选择环路带宽的一种较好的方法是先选择最优抖动带宽(BWJIT),然后增加带宽提高锁定时间或低频偏相位噪声,或者降低带宽提高高频偏相位噪声或杂散。

选择正确的环路带宽遇到问题?登录并在下方评论。

审核编辑:金巧

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

振荡器

+关注

关注

28文章

4192浏览量

143166 -

噪声

+关注

关注

13文章

1162浏览量

49428 -

模拟

+关注

关注

7文章

1447浏览量

85513

发布评论请先 登录

相关推荐

热点推荐

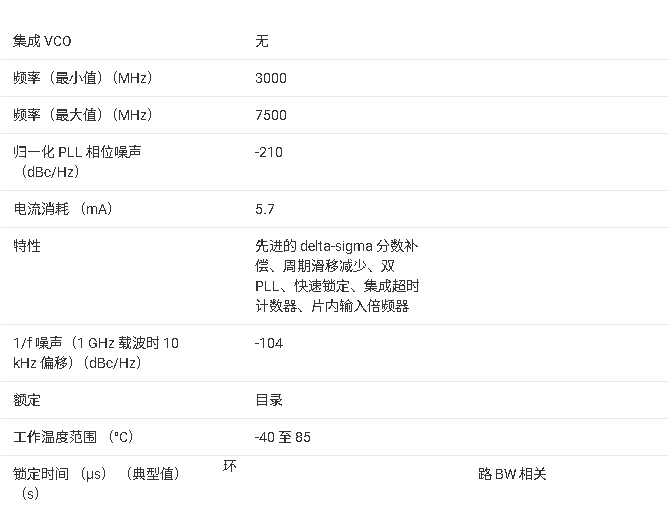

高性能低噪声锁相环LTC6948:设计与应用全解析

的高性能、低噪声的6.39GHz锁相环,看看它究竟有何独特之处,以及在实际设计中如何发挥其优势。 文件下载: LTC6948.pdf 一、LTC6948概述 LTC6948是一款集成了VCO的高性能低噪声

相位噪声分析仪(相噪仪)使用与选型指南

相位噪声分析仪功能强大,例如安铂克科技APPH系列用于评估信号源(晶体振荡器、VCO、发射器、锁相环、频率合成器等,范围从 VHF 到微波频

TLC2932A高性能锁相环芯片详解:设计与应用指南

TLC2932A高性能锁相环芯片详解:设计与应用指南 在电子设计领域,锁相环(PLL)是一种至关重要的电路,它能够实现信号的相位同步和频率合成,广泛应用于通信、雷达、仪器仪表等众多领域。今天要给大家

探索TLC2933A高性能锁相环:特性、应用与设计要点

,了解其特性、工作原理及应用中的设计要点。 文件下载: tlc2933a.pdf 一、TLC2933A概述 TLC2933A专为锁相环系统设计,主要由电压控制振荡器(VCO)和边缘触发型相位频率检测

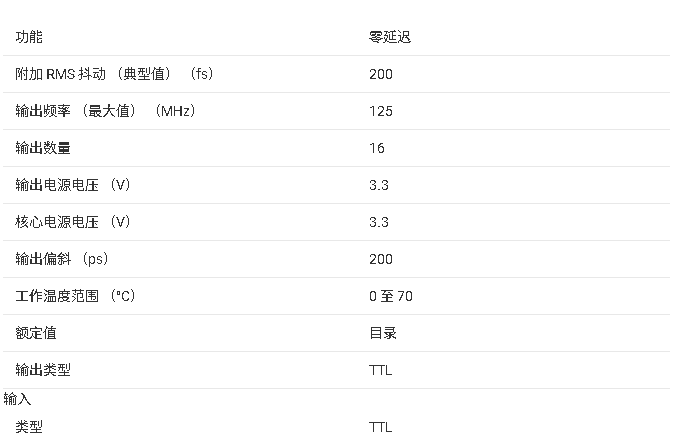

CDCVF2510 3.3V锁相环时钟驱动器技术文档总结

该CDCVF2510是一款高性能、低偏斜、低抖动、锁相环 (PLL) 时钟驱动器。它使用锁相环 (PLL) 将反馈 (FBOUT) 输出与时钟 (CLK) 输入信号在频率和相位上精确对

CDC516 3.3V相位锁定环时钟驱动器技术文档总结

CDC516 是一款高性能、低偏斜、低抖动、锁相环时钟驱动器。它使用锁相环 (PLL) 将反馈输出 (FBOUT) 与时钟 (CLK) 输入信号在频率和相位上精确对齐。它专为与同步 D

基于锁相环的无轴承同步磁阻电机无速度传感器检测技术

使用场合。为实现无轴承同步磁阻电机高速超高速、低成本、实用化运行,提出了一种基于锁相环法的无速度传感自检测技术。通过应用锁相环原理,设计出无轴承同步磁阻电机无速度传感器,并基于 Matlab

发表于 07-29 16:22

ADF4151小数N/整数N分频PLL频率合成器技术手册

= (INT + (FRAC/MOD))]。RF输出相位可通过编程设置,适合要求输出与基准之间存在特定相位关系的应用。ADF4151还具有周跳减少电路,可进一步缩短锁定时间,而无需修改环路

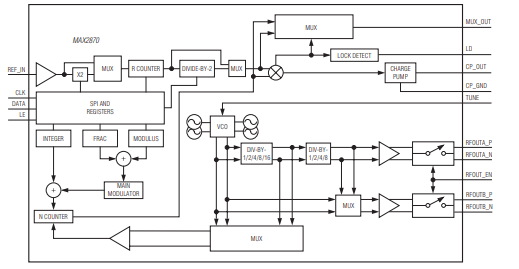

MAX2870 23.5MHz至6000MHz分数/整数N分频合成器/VCO技术手册

MAX2870为超宽频带锁相环(PLL),集成压控振荡器(VCO),能够工作在整数和分数N分频模式。配合外部参考时钟振荡器和环路滤波器,MA

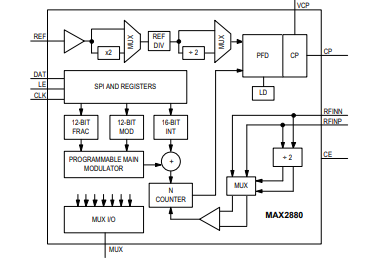

MAX2880 250MHz-12.4GHz、高性能、分数/整数型N分频PLL技术手册

MAX2880为高性能锁相环(PLL),提供整数或分数N分频工作模式。器件配合外部参考时钟振荡器、环路滤波器和VCO,可以构成超低噪声、低

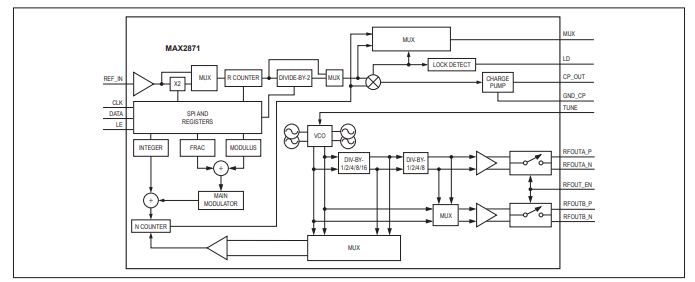

MAX2871 23.5MHz至6000MHz小数/整数N分频频率合成器/VCO技术手册

MAX2871是一款超宽带锁相环(PLL),集成压控振荡器(VCO),可在整数N分频和小数N分频模式下工作。与外部基准振荡器和环路滤波器结合

发现相位噪声、锁定时间或杂散问题请检查锁相环的环路滤波器带宽

发现相位噪声、锁定时间或杂散问题请检查锁相环的环路滤波器带宽

评论