锁相环(PLL)是一种反馈系统,其中电压控制振荡器(VCO)和相位比较器相互连接,使得振荡器可以相对于参考信号维持恒定的相位角度。在使用PLL的过程中您都遇到过哪些问题呢?咱们工程师整理了PLL芯片接口方面最常见的11个问题,这里分享给大家!

1参考晶振有哪些要求?该如何选择参考源?

波形: 可以使正弦波,也可以为方波。

功率: 满足参考输入灵敏度的要求。

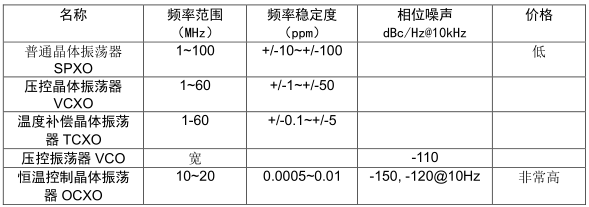

稳定性: 通常用 TCXO,稳定性要求《 2 ppm。这里给出几种参考的稳定性指标和相位噪声指标。

频率范围: ADI 提供的 PLL 产品也可以工作在低于最小的参考输入频率下,条件是输入信号的转换速率要满足给定的要求。

建议

在PLL 频率综合器的设计中,我们推荐使用温度补偿型晶振(TCXO)。在需要微调参考的情况下使用 VCXO,需要注意 VCXO 灵敏度比较小,比如 100Hz/V,所以设计环路滤波器的带宽不能很大(比如 200Hz),否则构成滤波器的电容将会很大,而电阻会很小。普通有源晶振,由于其温度稳定性差,在高精度的频率设计中不推荐使用。

2能详细解释下控制时序、电平及要求吗?

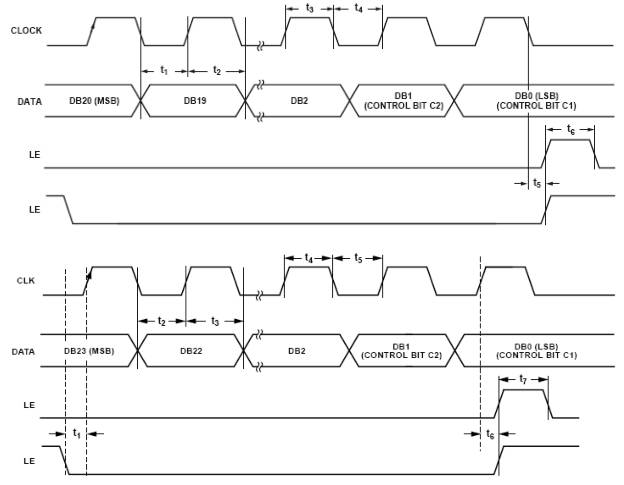

ADI 的所有锁相环产品控制接口均为三线串行控制接口,如图 1所示。要注意的是:在 ADI 的PLL 产品中,大多数的时序图如图 1中上面的图所示,该图是错误的,正确的时序图如图 1中下面的图所示,LE 的上升沿应跟 Clock 的上升沿对齐,而非 Clock 的下降沿。

图 1. PLL 频率合成器的串行控制接口(3 Wire Serial Interface)

控制接口由时钟 CLOCK,数据 DATA,加载使能 LE 构成。加载使能 LE 的下降沿提供起始串行数据的同步。串行数据先移位到 PLL 频率合成器的移位寄存器中,然后在 LE 的上升沿更新内部相应寄存器。注意到时序图中有两种 LE 的控制方法。

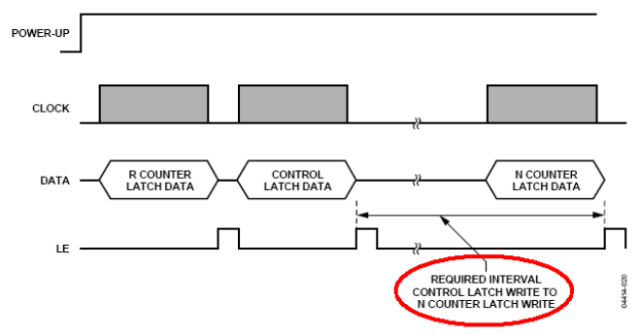

SPI 控制接口为 3V/3.3V CMOS 电平。另外,需要注意的是对 PLL 芯片的寄存器进行写操作时,需要按照一定的次序来写,具体请参照芯片资料中的描述。特别地,在对 ADF4360 的寄存器进行操作时,注意在写控制寄存器和 N计数器间要有一定的延时。

控制信号的产生,可以用 MCU,DSP,或者 FPGA。产生的时钟和数据一定要干净,过冲小。当用 FPGA 产生时,要避免竞争和冒险现象,防止产生毛刺。如果毛刺无法避免,可以在数据线和时钟线上并联一个 10~47pF 的电容,来吸收这些毛刺。

3控制多片 PLL 芯片时,串行控制线是否可以复用?

一般地,控制 PLL 的信号包括:CE,LE,CLK,DATA。CLK 和 DATA 信号可以共用,即占用2 个 MCU 的 IO 口,用 LE 信号来控制对哪个 PLL 芯片进行操作。多个 LE 信号也可以共用一个MCU 的 IO 口,这时需要用 CE 信号对芯片进行上电和下电的控制。

4可否简要介绍环路滤波器参数的设置?

ADIsimPLL V3.3 使应用工程师从繁杂的数学计算中解脱出来。我们只要输入设置环路滤波器的几个关键参数,ADIsimPLL 就可以自动计算出我们所需要的滤波器元器件的数值。这些参数包括,鉴相频率 PFD,电荷泵电流 Icp,环路带宽 BW,相位裕度,VCO 控制灵敏度 Kv,滤波器的形式(有源还是无源,阶数)。计算出的结果往往不是我们在市面上能够买到的元器件数值,只要选择一个最接近元器件的就可以。

通常环路的带宽设置为鉴相频率的 1/10 或者 1/20。

相位裕度设置为 45 度。

滤波器优先选择无源滤波器。

滤波器开环增益和闭环增益以及相位噪声图之间的关系。闭环增益的转折频率就是环路带宽。相位噪声图上,该点对应于相位噪声曲线的转折频率。如果设计的锁相环噪声太大,就会出现频谱分析仪上看到的转折频率大于所设定的环路带宽。

5环路滤波器采用有源滤波器还是无源滤波器?

有源滤波器因为采用放大器而引入噪声,所以采用有源滤波器的 PLL 产生的频率的相位噪声性能会比采用无源滤波器的 PLL 输出差。因此在设计中我们尽量选用无源滤波器。其中三阶无源滤波器是最常用的一种结构。PLL 频率合成器的电荷泵电压 Vp 一般取 5V 或者稍高,电荷泵电流通过环路滤波器积分后的最大控制电压低于 Vp 或者接近 Vp。

如果VCO/VCXO 的控制电压在此范围之内,无源滤波器完全能够胜任;如果VCO/VCXO 的控制电压超出了 Vp,或者非常接近 Vp 的时候,就需要用有源滤波器。在对环路误差信号进行滤波的同时,也提供一定的增益,从而调整VCO/VCXO控制电压到合适的范围。

那么如何选择有源滤波器的放大器呢?这类应用主要关心一下的技术指标:

低失调电压(Low Offset Voltage) [通常小于 500uV]

低偏流(Low Bias Current) [通常小于 50pA]

如果是单电源供电,需要考虑使用轨到轨(Rail-to-Rail)输出型放大器。

6PLL 对于 VCO 有什么要求?如何设计 VCO 输出功率分配器?

选择 VCO 时,尽量选择 VCO 的输出频率对应的控制电压在可用调谐电压范围的中点。选用低控制电压的 VCO 可以简化 PLL 设计。

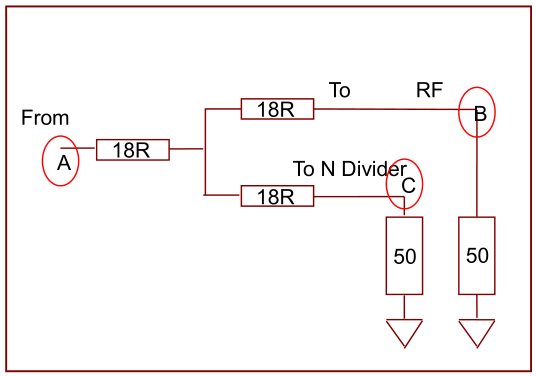

VCO 的输出通过一个简单的电阻分配网络来完成功率分配。从 VCO 的输出看到电阻网络的阻抗为 18+(18+50)//(18+50)=52ohm。形成与 VCO 的输出阻抗匹配。下图中 ABC 三点功率关系。B,C 点的功率比 A 点小 6dB。

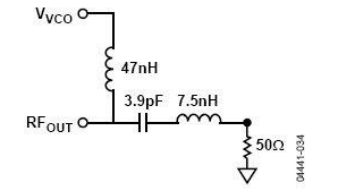

如下图是 ADF4360-7 输出频率在 850MHz~950MHz 时的输出匹配电路,注意该例是匹配到 50 欧的负载。如果负载是 75 欧,那么匹配电路无需改动,ADF4360-7 的输出级为电流源,负载值的小变动不会造成很大的影响,但要注意差分输出端的负载需相等。

7如何设置电荷泵的极性?

在下列情况下,电荷泵的极性为正。

环路滤波器为无源滤波器,VCO 的控制灵敏度为正(即,随着控制电压的升高,输出频率增大)。

在下列情况下,电荷泵的极性为负。

环路滤波器为有源滤波器,并且放大环节为反相放大;VCO 的控制灵敏度为正。

环路滤波器为无源滤波器,VCO 的控制灵敏度为负。

PLL分频应用,滤波器为无源型。即参考信号直接 RF 反馈分频输入端,VCO 反馈到参考输入的情况。

8锁定指示电路如何设计?

PLL 锁定指示分为模拟锁定指示和数字锁定指示两种。

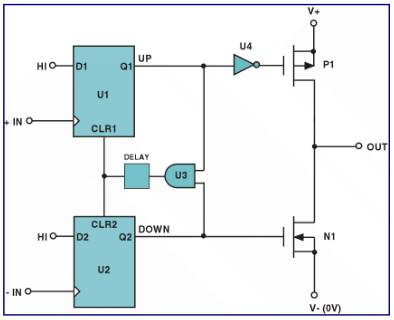

鉴相器和电荷泵原理图

数字锁定指示:

当 PFD 的输入端连续检测到相位误差小于 15ns 的次数为 3(5)次,那么 PLL 就会给出数字锁定指示。

数字锁定指示的工作频率范围:通常为 5kHz~50MHz。在更低的 PFD 频率上,漏电流会触发锁定指示电路;在更高的频率上,15ns 的时间裕度不再适合。在数字锁定指示的工作频段范围之外,推荐使用模拟锁定指示。

模拟锁定指示:

对电荷泵输入端的 Up 脉冲和 Down 脉冲进行异或处理后得出的脉冲串。所以当锁定时,锁定指示电路的输出为带窄负脉冲串的高电平信号。图为一个典型的模拟锁定指示输出(MUXOUT 输出端单独加上拉电阻的情况)。

模拟锁定指示的输出级为 N 沟道开漏结构,需要外接上拉电阻,通常为 10KOhm~160kohm。我们可以通过一个积分电路(低通滤波器)得到一个平坦的高电平输出,如图所是的蓝色框电路。

误锁定的一个条件:

参考信号REFIN信号丢失。当REFIN信号与PLL频合器断开连接时,PLL显然会失锁;然而,ADF41xx 系列的 PLL,其数字锁定指示用 REFIN 时钟来检查是否锁定,如果 PLL 先前已经锁定,REFIN 时钟突然丢失,PLL 会继续显示锁定状态。解决方法是使用模拟锁定指示。

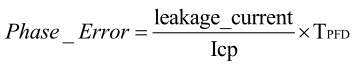

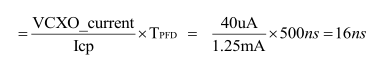

当 VCXO 代替 VCO 时,PLL 常常失锁的原因。以 ADF4001 为例说明。VCXO 的输入阻抗通常较小(相对于 VCO 而言),大约为 100kohm。这样 VCXO 需要的电流必须由 PLL 来提供。PFD=2MHz, Icp=1.25mA,Vtune=4V,VCXO 输入阻抗=100kohm,VCXO 控制口电流=4/100k=40uA。在 PFD 输入端,用于抵消 VCXO 的输入电流而需要的静态相位误差

16ns》15ns,所以,数字锁定指示为低电平。

解决方法1,使用模拟锁定指示。

解决方法2,使用更高的电荷泵电流来减小静态相位误差。增大环路滤波器电容,使放电变缓。

9PLL 对射频输入信号有什么要求?

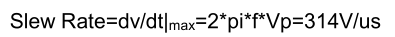

频率指标:可以工作在低于最小的射频输入信号频率上,条件是 RF 信号的 Slew Rate 满足要求。

例如,ADF4106 数据手册规定最小射频输入信号 500MHz,功率为-10dBm,这相应于峰峰值为200mV,slew rate=314V/us。如果您的输入信号频率低于 500MHz,但功率满足要求,并且slew rate 大于 314V/us,那么 ADF4106 同样能够正常工作。通常 LVDS 驱动器的转换速率可以很容易达到 1000V/us。

10PLL 芯片对电源的要求有哪些?

要求 PLL 电源和电荷泵电源具有良好的退耦,相比之下,电荷泵的电源具有更加严格的要求。具体实现如下:

在电源引脚出依次放置 0.1uF,0.01uF,100pF 的电容。最大限度滤除电源线上的干扰。大电容的等效串联电阻往往较大,而且对高频噪声的滤波效果较差,高频噪声的抑制需要用小容值的电容。下图可以看到,随着频率的升高,经过一定的转折频率后,电容开始呈现电感的特性。不同的电容值,其转折频率往往不同,电容越大,转折频率越低,其滤除高频信号的能力越差。

另外在电源线上串联一个小电阻(18ohm)也是隔离噪声的一种常用方法。

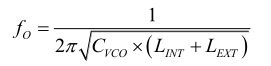

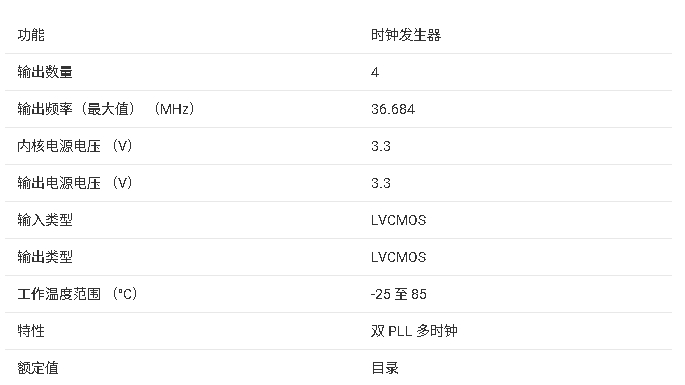

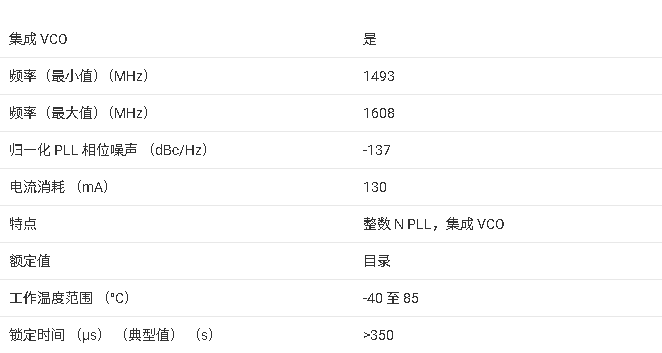

11集成VCO 的ADF4360-x ,其中心频率如何设定?

VCO 的中心频率由下列三个因素决定。

1)VCO 的电容 C VCO

2)由芯片内部 Bond Wires 引入的电感 L BW

3)外置电感 L EXT 。即

其中前2项由器件决定,这样只要给定一个外置电感,就可以得到VCO的输出 中心频率。VCO的控制灵敏度在相应的数据手册上给出。作为一个例子,下图给出了 ADF4360-7 的集成 VCO 特性。

电感的选取,最好选用高 Q 值的。Coilcraft 公司是不错的选择。市面上常见的电感基本在 1nH以上。更小的电感可以用 PCB 导线制作。这里给出一个计算 PCB 引线电感的简单公式,如下图所示。

责任编辑:haq

-

芯片

+关注

关注

462文章

53533浏览量

458943 -

接口

+关注

关注

33文章

9443浏览量

156118 -

pll

+关注

关注

6文章

976浏览量

137575

原文标题:接下来是答疑环节——常见PLL芯片接口问题11则

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

频谱芯片常见故障和预防措施

网络接口:数字世界的“门铃”,你了解多少?

PLL1707/PLL1708 双PLL多时钟发生器技术文档总结

TRF3761系列整数N锁相环(PLL)与集成VCO芯片技术文档总结

易灵思 FPGA TJ375的PLL的动态配置

智多晶PLL使用注意事项

PLL用法

充电接口你真的了解吗?

ESD防护设计中的10个常见误区,你中招了吗?

函数指针的六个常见应用场景

PLL芯片接口方面最常见的11个问题

PLL芯片接口方面最常见的11个问题

评论