西电刘艳团队于IEEE EDL四月刊发布了基于静电掺杂的铁电晶体管器件,相比化学掺杂工艺,其具有非挥发、可重构、轻掺杂漏极、高源漏掺杂浓度、低源漏电阻等优良特性,对于先进集成电路工艺微缩和后摩尔新型器件提供了更多的解决路径。

研究背景

化学掺杂技术被大规模运用于半导体器件的制造,但其技术有着包括较高的掺杂活化热预算、低于固溶极限的掺杂浓度、杂质散射和掺杂梯度在内各种问题。相应地,静电掺杂技术被认为是最具有替代化学掺杂技术的新路线。通过这种技术,掺杂可以被能带和临近电极费米能级的相对能量差所控制,通过功函数调控或外偏置可实现有效控制。

作为化学掺杂技术的替代,静电掺杂技术因其非易失性、载流子可控的特性,基于该技术的可重构晶体管被提出,但这需要额外偏置条件来克服易挥发性。由于非易失性和可控的极化状态,铁电材料在非易失性存储器方面的应用越来越广,这为实现非易失性和可重构性提供了技术路径。

西电刘艳教授团队与新加坡国立大学及印度理工学院联合课题组在这一研究方向上取得了重要进展,以“Proposal of Ferroelectric Based Electrostatic Doping for Nanoscale Devices”为题发表于IEEE Electron Device Letters,郑思颖为第一作者,西电刘艳教授和新加坡国立大学的Jiuren Zhou为共同通讯作者。

研究内容

在本项研究中,团队提出了基于铁电材料的经典掺杂技术,通过插入极性门的铁电薄膜实现了非挥发性和可重构性,可在不需要恒定偏置条件的情况下制备基于铁电材料静电掺杂技术的可重构纳米片场效应晶体管,具有自然形成的轻掺杂漏极(LDD)*和每立方厘米超过1021的极高的源漏区掺杂浓度,可改善晶体管亚阈值摆幅*、抑制漏极感应势垒降低(DIBL)*、获得超低源漏区电阻。

*轻掺杂漏极:全称Lightly doped drain,在双扩散漏(double diffuse drain)工艺上发展而来,在MOS侧墙形成之前增加一道轻掺杂的离子注入流程,侧墙形成后依然进行源漏重掺杂离子注入,漏极和沟道之间会形成一定宽度的轻掺杂区域;相比DDD工艺降低了器件漏极附近峰值电场,削弱了热载流子注入效应。

*亚阈值摆幅:Subthreshold swing,是衡量晶体管开启与关断状态之间相互转换速率的性能指标,它代表源漏电流变化十倍所需要栅电压的变化量,又称为S因子,S越小意味着开启关断速率ON/OFF越快。

漏极感应势垒降低:Drain induction barrier lower,也称漏极诱导势垒降低,短沟道效应之一,当沟道长度减小、VDS增加、使得漏结与源结的耗尽层靠近时,沟道中的电力线可以从漏区穿越到源区,并导致源极端势垒高度降低,从而源区注入到沟道的电子数量增加,结果漏极电流增加。

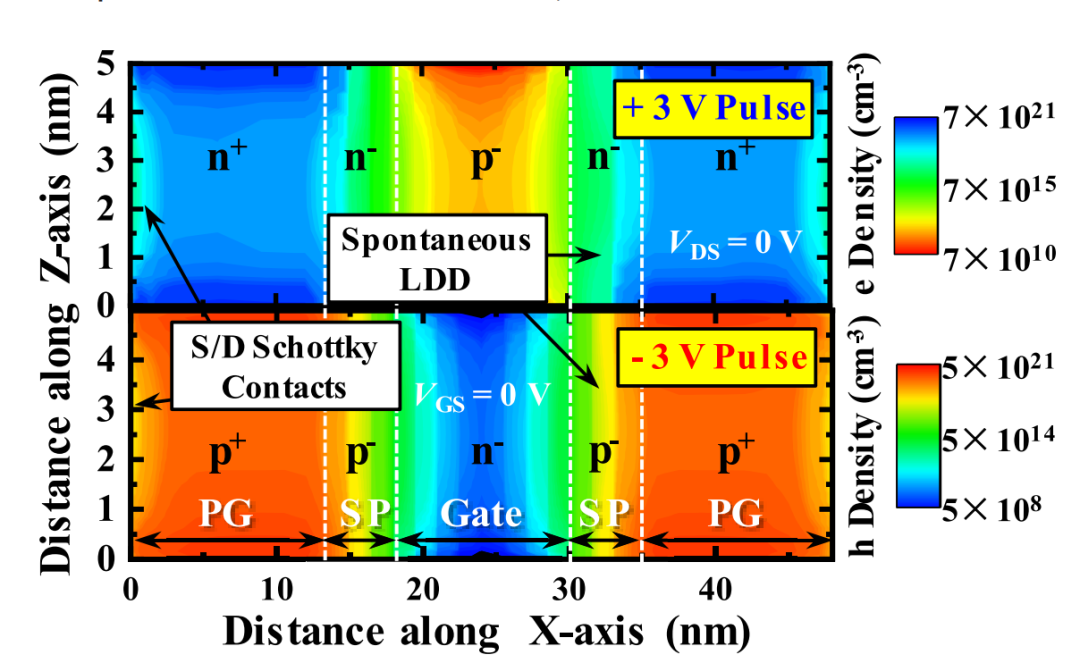

晶体管参数表

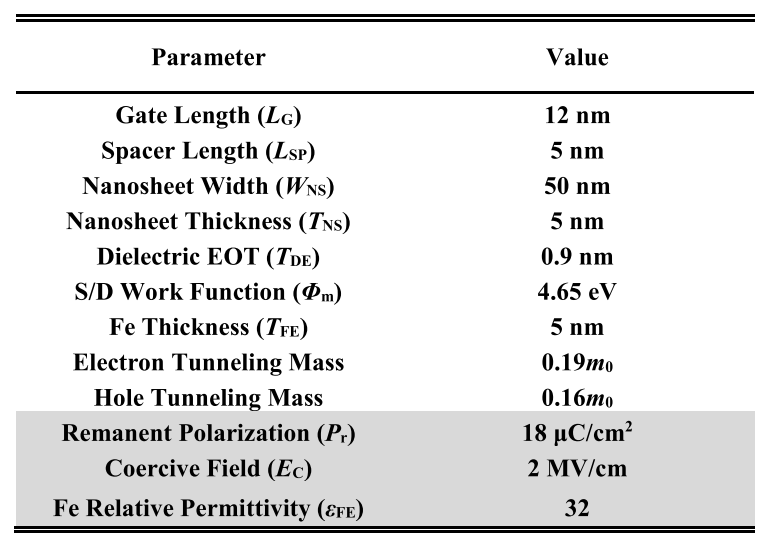

图(a)铁电纳米片晶体管示意图

图(b)铁电薄膜的自极化和可控极化

图(c)可重构晶体管能带图

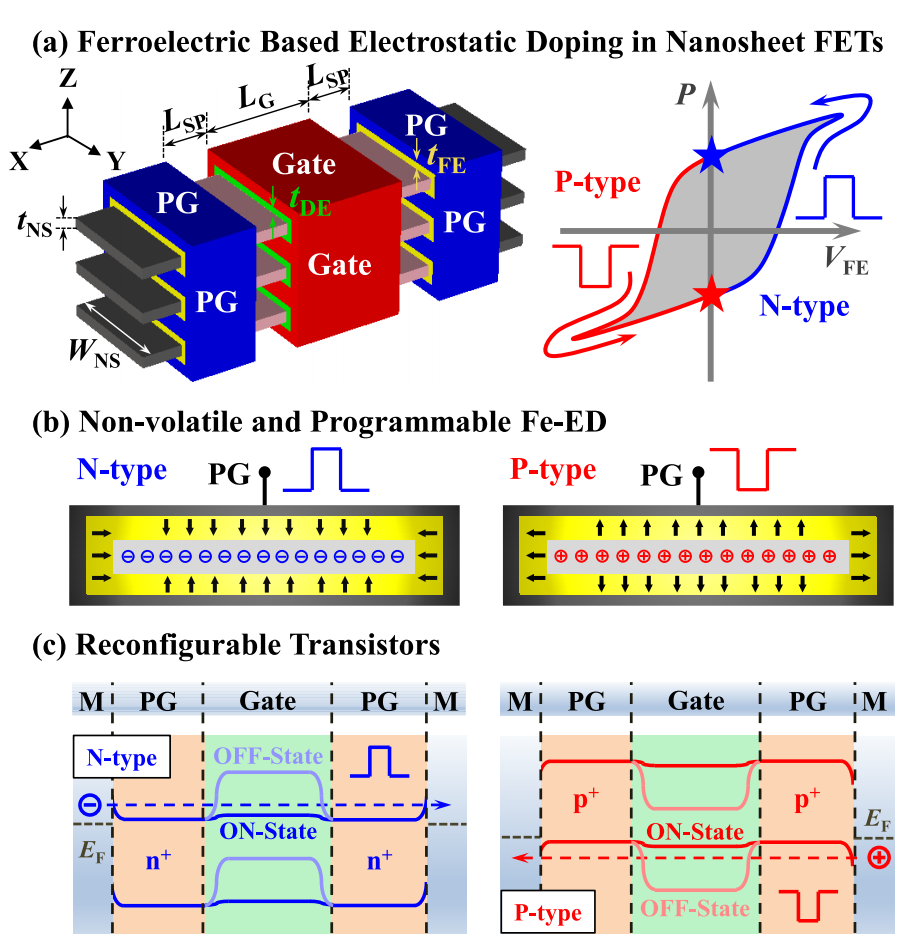

制备过程关键三步:

极性栅极-自对准控制栅-源漏接触

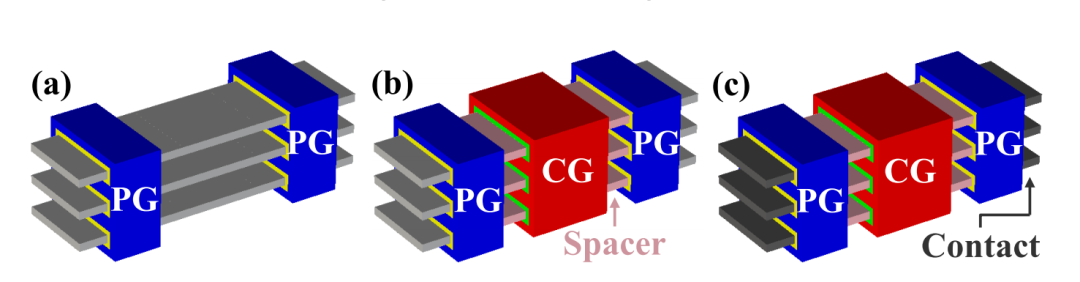

VPG、VGS、VDS均为0时的载流子浓度分布

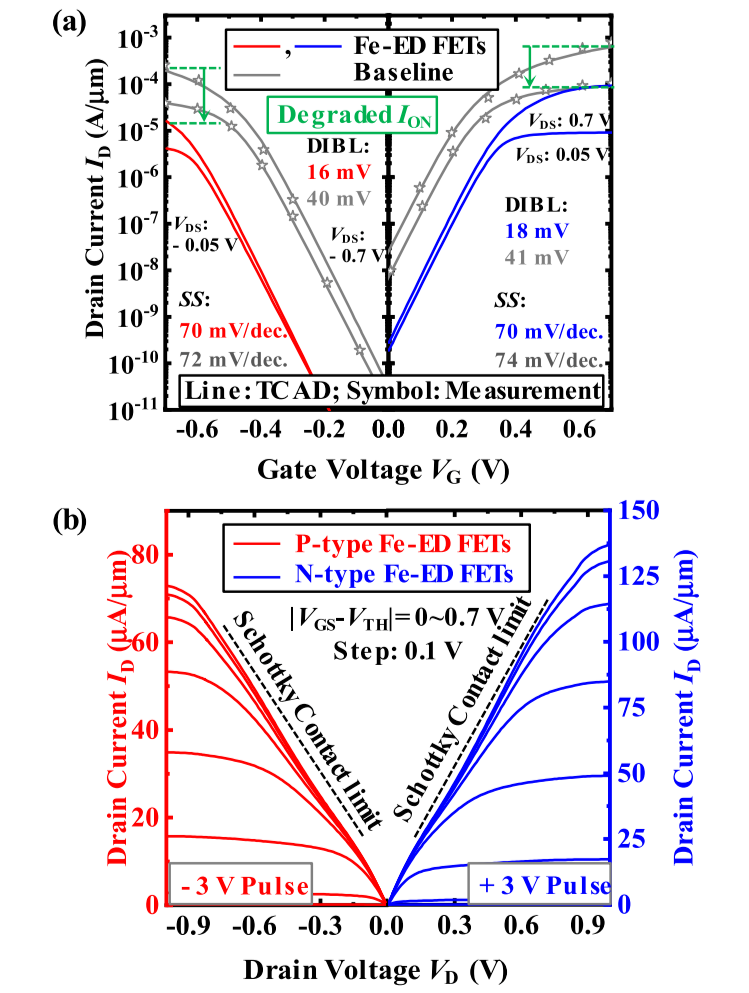

ID-VG曲线和ID-VD曲线

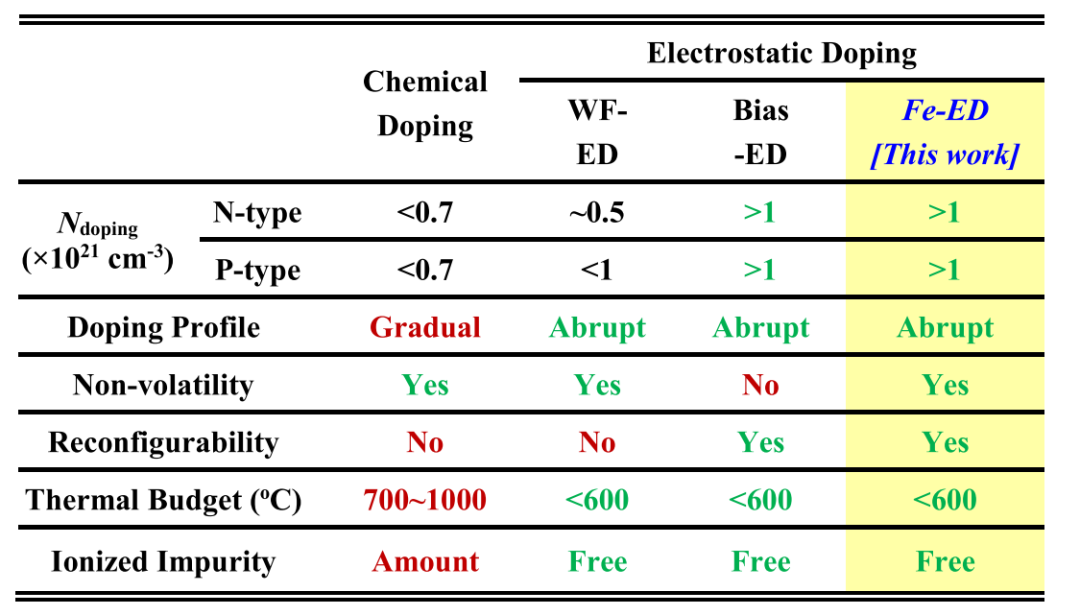

几类掺杂技术的成果对比

前景展望

本文所介绍的研究成果实现了无恒定偏置下实现晶体管的非挥发性和可重构性,并具有各种良好的性能改进,但对于超低漏源电阻的改进,还需要进一步的研究。总而言之,该技术为先进纳米器件和和后摩尔新型器件提供了一种新的解决路径,在forksheet*等高集成度的先进工艺中非挥发性和可控掺杂是必要的。

*forksheet:通过在nanosheet结构中加入电介质“墙”隔离同型沟道实现晶体管单元面积缩小的一种晶体管结构。

原文标题:科研前线 | 西电静电掺杂新成果推动新型器件研发

文章出处:【微信公众号:芯片揭秘】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

电阻

+关注

关注

88文章

5812浏览量

179927 -

晶体管

+关注

关注

78文章

10439浏览量

148582

原文标题:科研前线 | 西电静电掺杂新成果推动新型器件研发

文章出处:【微信号:ICxpjm,微信公众号:芯片揭秘】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何在 S32K3 上实现自旋锁?

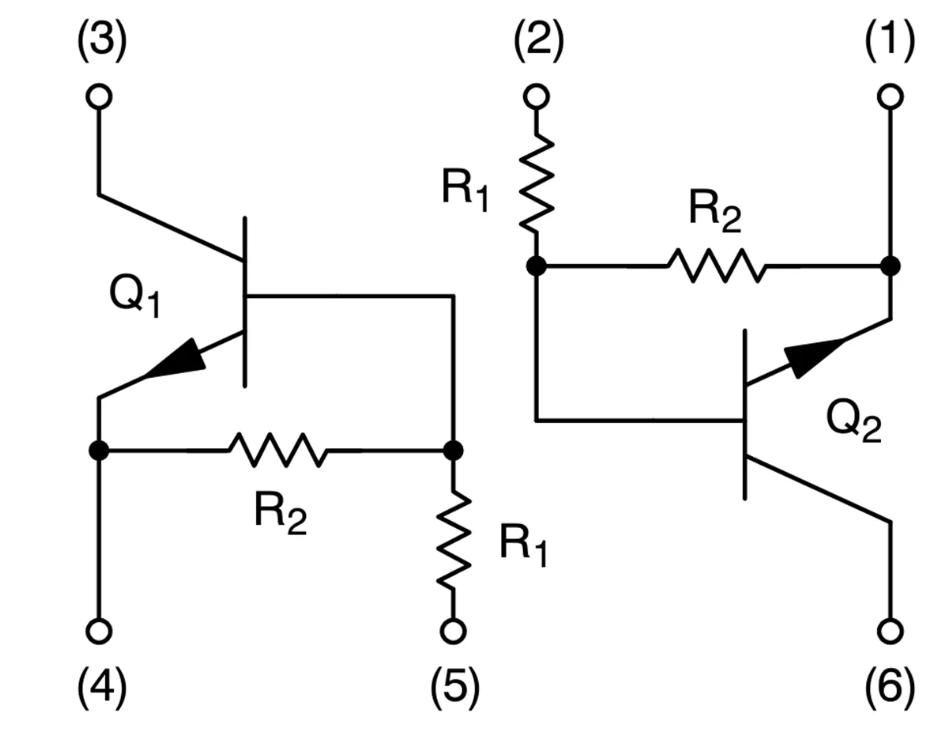

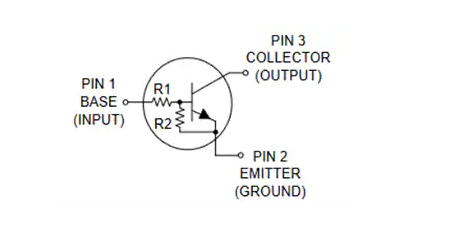

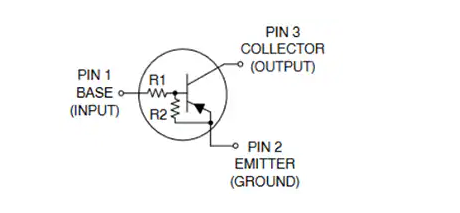

基于偏置电阻晶体管(BRT)的数字晶体管系列MUN2231等产品解析

安森美双NPN偏置电阻晶体管:简化电路设计的理想之选

NSBCMXW系列偏置电阻晶体管(BRT)技术解析与应用指南

深入解析onsemi偏置电阻晶体管(BRT)NSBAMXW系列技术特性与应用

电压选择晶体管应用电路第二期

晶体管的定义,晶体管测量参数和参数测量仪器

英飞凌功率晶体管的短路耐受性测试

多值电场型电压选择晶体管结构

Sensirion的SGP4x传感器对挥发性有机物和H2等气体的敏感性

下一代高速芯片晶体管解制造问题解决了!

薄膜晶体管技术架构与主流工艺路线

什么是晶体管?你了解多少?知道怎样工作的吗?

耐辐射光电晶体管非密封表面贴装光耦合器 skyworksinc

无恒定偏置下实现晶体管的非挥发性和可重构性

无恒定偏置下实现晶体管的非挥发性和可重构性

评论