安森美 (onsemi) NSBCMXW NPN 偏置电阻晶体管 (BRT) 设计用于替代单个设备及其相关的外部偏置电阻网络。 这些安森美 (onsemi) BRT集成了单个晶体管和一个单片偏置网络,该网络由一个系列基极电阻和一个基极-发射极电阻组成。BRT将所有组件集成到单个设备中,从而消除了单个组件。使用BRT可以降低系统成本和电路板空间。NSBCMXW组件采用XDFNW3封装,具有卓越的散热性能。这些晶体管非常适合用于电路板空间和可靠性至关重要的表面贴装应用。

数据手册;*附件:onsemi NSBCMXW NPN偏置电阻晶体管数据手册.pdf

特性

- 内置偏置电阻器

- XDFNW3外壳521AC封装,安装高度低至0.44mm(最大值)

- 可湿性侧翼封装,实现最佳自动光学检测(AOI)

- 静电放电 (ESD) 等级 (HBM):级别1B

- NSV前缀适用于汽车和其他需要独特现场和控制变更要求的应用;符合AEC-Q101标准并具备PPAP功能

- 无铅、无卤/无溴化阻燃剂(BFR),符合RoHS指令

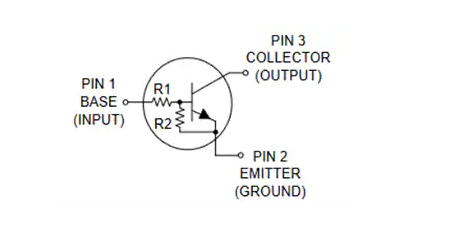

引脚连接

NSBCMXW系列偏置电阻晶体管(BRT)技术解析与应用指南

一、产品概述与技术原理

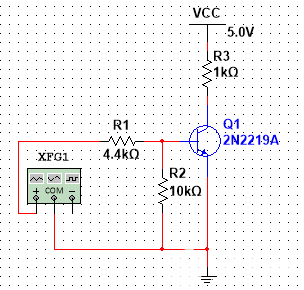

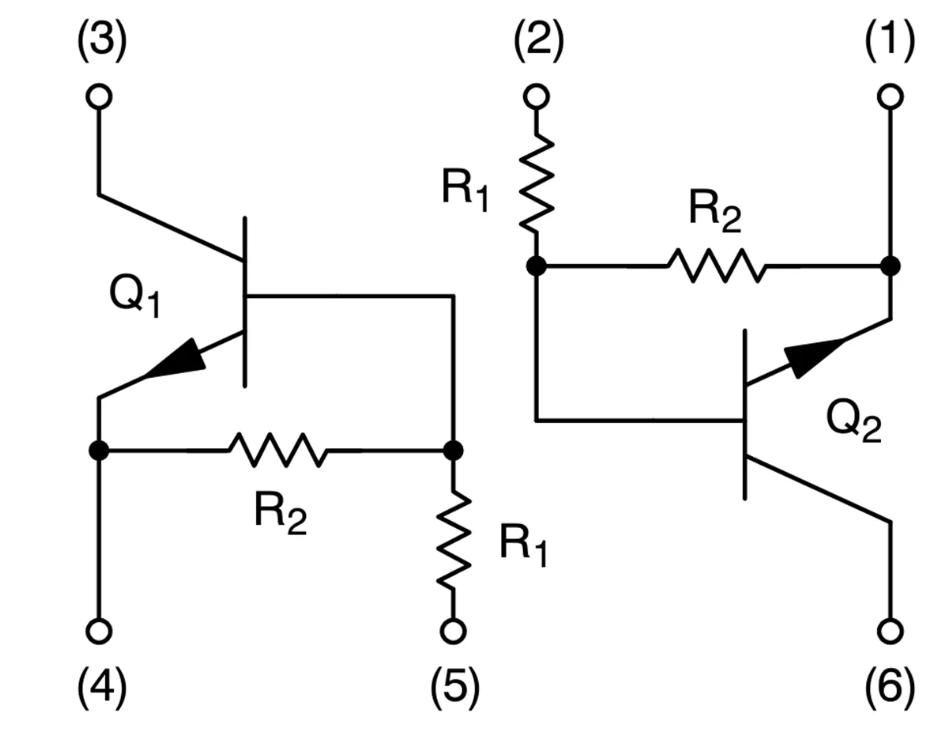

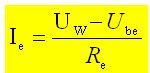

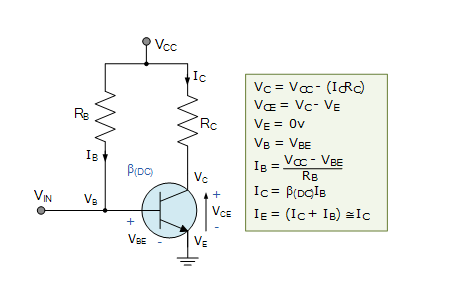

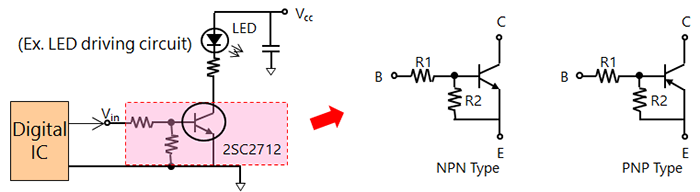

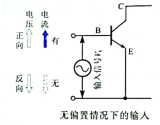

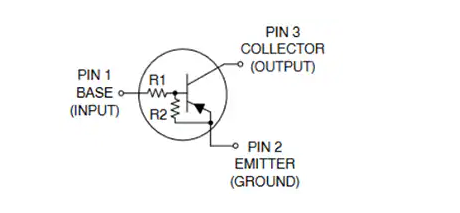

NSBCMXW系列是安森美半导体推出的NPN偏置电阻晶体管(Bias Resistor Transistors),设计用于替代传统分立晶体管及其外部偏置电阻网络。该系列器件单片集成一个晶体管和由两个电阻构成的偏置网络:一个串联基极电阻(R1)和一个基极-发射极电阻(R2)。这种创新设计通过器件集成化显著节省系统成本和PCB空间,特别适用于板面空间和可靠性要求严苛的表面贴装应用。

核心技术特征

- 电压电流规格:集电极-发射极电压50V,集电极电流100mA

- 封装优势:采用DFN1010-3封装,最大安装高度仅0.44mm

- 质量认证:提供汽车级NSV前缀版本,通过AEC-Q101认证并具备PPAP能力

- 环保合规:无铅、无卤素/BFRfree,符合RoHS标准

二、关键电气参数深度分析

2.1 极限工作条件

在25°C环境温度下,器件的最大额定值包括:

- 集电极-发射极电压(VCEO):50V

- 集电极-基极电压(VCBO):50V

- 输入电压范围:根据不同型号从-10V到+40V不等

注意事项:超出最大额定值的应力可能损坏器件,此时不应假定器件功能正常,可能发生损坏并影响可靠性

2.2 静态特性参数

以NSBC144E型为例的典型电气特性:

- 直流电流增益(hFE) :VCE=10V,IC=5mA时,典型值为80

- 集电极-发射极饱和电压:IC=10mA,IB=0.3mA时最大0.25V

- 关断输入电压:VCE=5V,IC=100mA时,典型值1.2V

- 导通输入电压:VCE=0.3V条件下,各型号的导通阈值从0.9V到2.0V不等

2.3 集成电阻规格

内置偏置电阻的标称值:

- NSBC114E:R1=10kΩ,R2=10kΩ

- NSBC124E:R1=22kΩ,R2=22kΩ

- NSBC143Z:R1=4.7kΩ,R2=47kΩ

- 电阻比值(R1/R2)根据不同型号在0.1到1之间

三、热管理与可靠性设计

3.1 热特性参数

- 总功耗:在TA=25°C时最大450mW

- 热阻:结到环境的热阻(RθJA)为145°C/W

- 工作温度范围:结温和存储温度范围-65°C至+150°C

3.2 散热设计考虑

根据图6的降额曲线,环境温度升高时需要相应降低功耗要求。在高温环境中设计时,必须参考瞬态热阻特性(图7)确保散热充分。

四、典型应用场景与设计指南

4.1 主要应用领域

4.2 电路设计要点

- 偏置设计简化:利用集成电阻网络,无需外部分立电阻

- 开关时序优化:参考图3、图4的输入输出特性曲线

- 布局建议:充分利用DFN1010-3封装的散热优势

五、选型指南与订购信息

5.1 型号对比选择

不同型号的主要差异在于内置电阻值和电阻比例:

- 需要较小基极电流时选择R1较大的型号(如NSBC124E)

- 对开关速度要求高时选择R1较小的型号

5.2 封装与标记

- 封装类型:XDFNW3(无铅)

- 标记规则:"XXM"格式,XX为具体器件代码,M为日期代码

- 包装方式:磁带和卷盘包装,每卷3000件

-

晶体管

+关注

关注

78文章

10272浏览量

146345 -

NPN

+关注

关注

11文章

2687浏览量

51068 -

偏置电阻

+关注

关注

1文章

44浏览量

8795

发布评论请先 登录

如何设置晶体管的Q点偏置?看看这篇文章就知道了

PNP晶体管的工作原理,如何识别PNP晶体管

NPN型和PNP型晶体管的工作状态解析

晶体管开关电路设计——晶体管选型与确定偏置电阻

安森美双NPN偏置电阻晶体管:简化电路设计的理想之选

基于偏置电阻晶体管(BRT)的数字晶体管系列MUN2231等产品解析

NSBCMXW系列偏置电阻晶体管(BRT)技术解析与应用指南

NSBCMXW系列偏置电阻晶体管(BRT)技术解析与应用指南

评论