常见的晶体管有二极管、三极管和MOS管,主要的逻辑门电路:与门、或门、非门、与非门、或非门、异或门等,这篇文章介绍用晶体管搭建常见的逻辑门电路。

废话不多说,直接上图。

1. 二极管

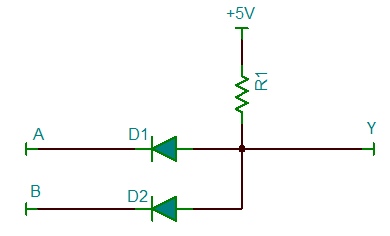

① 二极管与门

用两个二极管组成的与门,A和B都为高电平时,Y才为高电平。

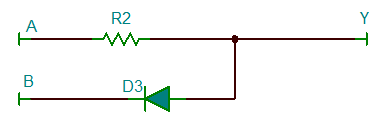

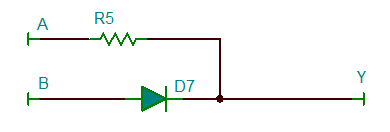

用1个二极管和1个电阻也可以组成与门。

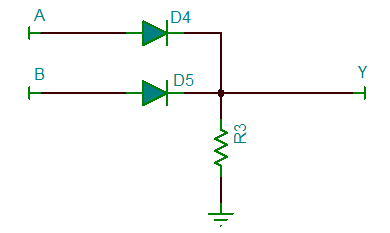

② 二极管或门

从下图两个或门电路可以看出,A和B只要有一个为高电平,输出Y就为高电平。

同样的,用1个电阻和1个二极管也可以组成或门。

2. 三极管

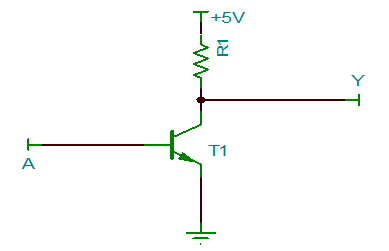

① 三极管非门

A为高电平,T1导通,Y为低电平;A为低电平,T1截止,Y为高电平。

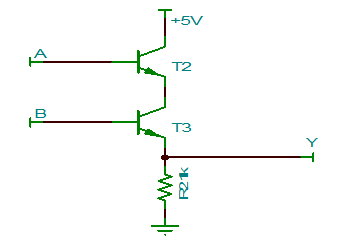

② 三极管与门

用2个NPN三极管搭建与门;A和B都为高电平时,T2和T3都导通,此时Y为高电平。

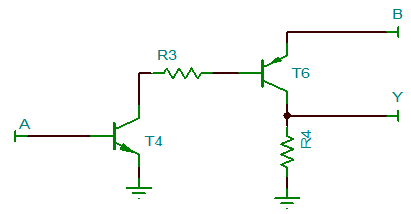

用1个NPN和1个PNP搭建的与门,当A和B均为高电平时,T4和T6都导通,Y为高电平。

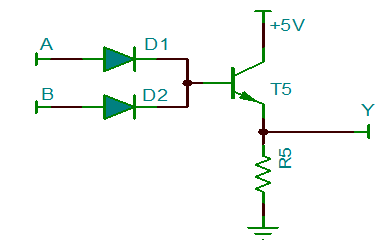

③ 三极管或门

在二极管或门基础上,可以加一个NPN三极管,也可以组成或门,A和B只要有一个高电平,T5就会导通,Y会由低电平变为高电平;当A和B都为低电平时,T5才截止,Y为低电平。

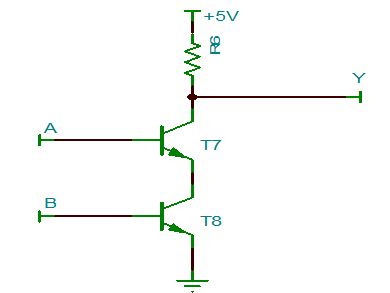

④ 三极管与非门

与非门由与门和非门组成,在三极管与门基础上稍作修改,可以变为三极管与非门。

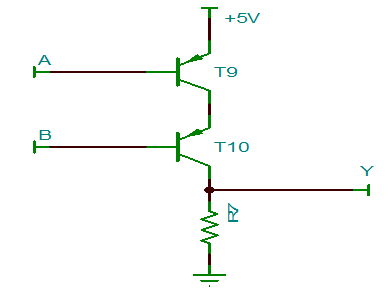

⑤ 三极管或非门

用2个PNP三极管搭建的或非门,A和B只要有一个高电平,Y就为低电平;当A和B都为低电平时,T9和T10均导通,Y为高电平。

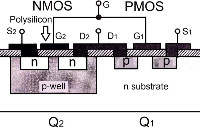

3. MOS管

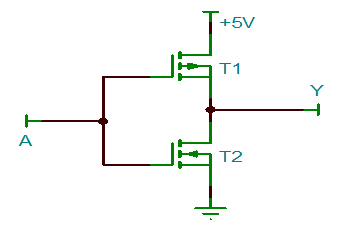

① MOS管非门

用1个NMOS和1个PMOS搭建的非门;当A为高电平时,T1截止,T2导通,Y为低电平;当A为低电平时,T1导通,T2截止,Y为高电平。

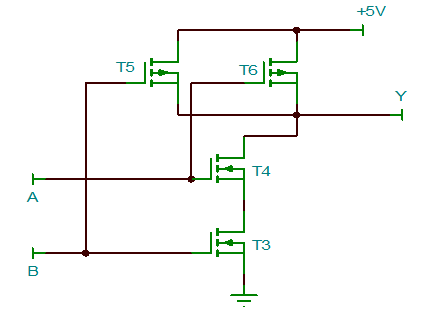

② MOS管与非门

备注:T3和T4为NMOS,T5和T6为PMOS;

A=0,B=0时,T5和T6导通,T3和T4截止,Y=1

A=1,B=0时,T3和T6截止,T4和T5导通,Y=1

A=0,B=1时,T3和T6导通,T4和T5截止,Y=1

A=1,B=1时,T5和T6截止,T3和T4导通,Y=0

③ MOS管或非门

备注:T7和T8为NMOS,T9和T10为PMOS;

A=0,B=0时,T9和T10导通,T7和T8截止,Y=1

A=1,B=0时,T7和T9截止,T8和T10导通,Y=0

A=0,B=1时,T7和T9导通,T8和T10截止,Y=0

A=1,B=1时,T9和T10截止,T7和T8导通,Y=0

4. 真值表

通过真值表能反映一个电路的功能,优秀的记得诚给出了如下门电路的真值表,小伙伴门可以巩固下各个门电路的功能。

① 与门

与门功能:输入都为1,输出才为1,只要有一个0,输出就为0,记作Y=A*B或者Y=AB;

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

② 或门

或门功能:输入只要有一个1,输出就为1,记作Y=A+B;

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

③ 非门

非门:非门也叫反相器,即输入1,输出0,输入0,输出1,记作Y=A';

| A | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

④ 与非门

与非门:与非门是与门与非门的结合,先与后非,记作Y=(AB)';

| A | B | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

⑤ 或非门

或非门:或非门是或门与非门的结合,先或后非,记作Y=(A+B)';

| A | B | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

5. 小结一下

用晶体管绘制常见的逻辑门电路,会让我们对晶体管的特性更加熟悉,在电路设计时更加的从容淡定,也常出现在硬件工程师的笔试题中,总之一句话,会了这些,你就是街上最靓的GAI;

责任编辑:lq

-

二极管

+关注

关注

149文章

10309浏览量

176449 -

晶体管

+关注

关注

78文章

10250浏览量

146254 -

逻辑门电路

+关注

关注

2文章

68浏览量

12442

原文标题:手把手教你用晶体管搭建逻辑门电路

文章出处:【微信号:strongerHuang,微信公众号:strongerHuang】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于偏置电阻晶体管(BRT)的数字晶体管系列MUN2231等产品解析

电压选择晶体管应用电路第二期

下一代高速芯片晶体管解制造问题解决了!

无结场效应晶体管详解

实用电子电路设计(全6本)——晶体管电路设计 下

多值电场型电压选择晶体管结构

浮思特 | CMOS技术原理与应用:从晶体管结构到反相器设计

用晶体管搭建常见的逻辑门电路

用晶体管搭建常见的逻辑门电路

评论