如今半导体的制程工艺已经进步到了7nm,再往后提升会越来越难。想要提升芯片性能还可以从晶圆封装上下文章。

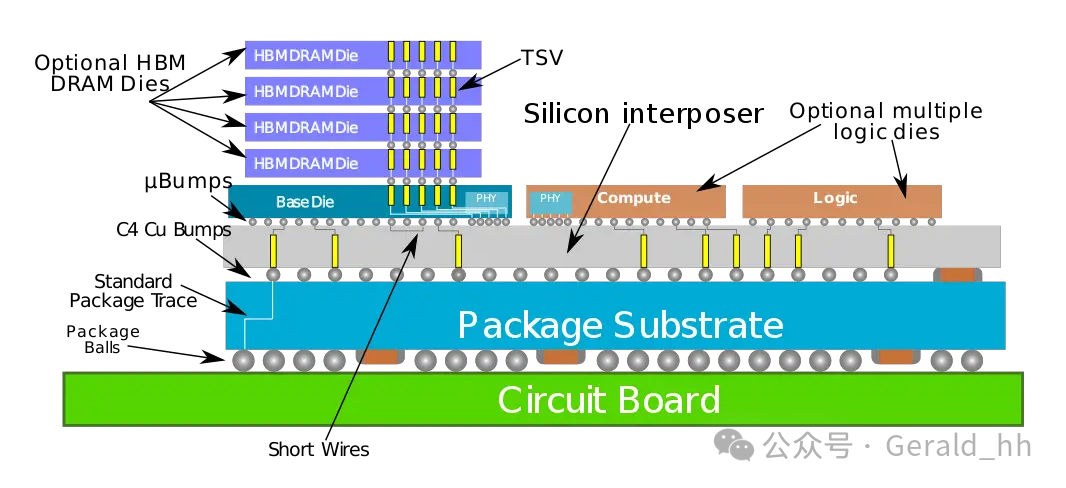

此前台积电曾推出过CoWoS(Chip on Wafer on Substrate)封装技术,将逻辑芯片和DRAM 放在硅中介层(interposer)上,然后封装在基板上。这是一种2.5D/3D封装工艺,可以让芯片尺寸更小,同时拥有更高的I/O带宽。不过由于成本较普通封装高了数倍,目前采用的客户并不多。

3月3日,台积电宣布将与博通公司联手推出增强型的CoWoS解决方案,支持业界首创的两倍光罩尺寸(2Xreticlesize)之中介层,面积约1,700平方毫米。

新的增强型CoWoS平台能够容纳将多个逻辑系统单晶片(SoC),最高提供96GB的HBM内存(6片),带宽高达2.7TB/s。相较于前代CoWoS提升了2.7倍。如果是和PC内存相比,提升幅度在50~100倍之间。

台积电表示此项新世代CoWoS平台能够大幅提升运算能力,藉由更多的系统单芯片来支援先进的高效能运算系统,并且已准备就绪支援台积电下一代的5纳米制程技术。

博通Engineering for the ASIC Products Division副总裁GregDix表示,很高兴能够与台积电合作共同精进CoWoS平台,解决许多在7nm及更先进制程上的设计挑战。

责任编辑:wv

-

芯片

+关注

关注

463文章

54432浏览量

469390 -

台积电

+关注

关注

44文章

5811浏览量

177055 -

博通

+关注

关注

36文章

4350浏览量

109314 -

CoWoS

+关注

关注

0文章

170浏览量

11536

发布评论请先 登录

创通联达与RidgeRun及ams OSRAM达成战略合作

台积电CoWoS平台微通道芯片封装液冷技术的演进路线

HBM技术在CowoS封装中的应用

TE推出AC DC电源管理产品特性和优点-赫联电子

化圆为方,台积电整合推出最先进CoPoS半导体封装

力旺NeoFuse于台积电N3P制程完成可靠度验证

西门子推出用于EDA设计流程的AI增强型工具集

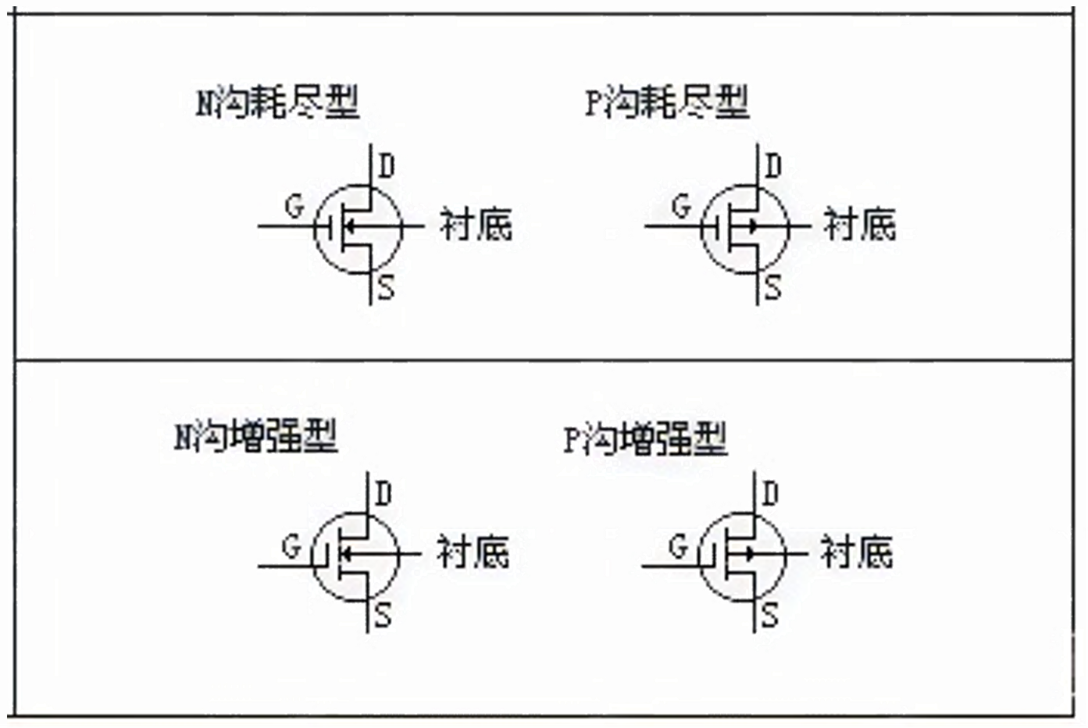

增强型和耗尽型MOS管的应用特性和选型方案

台积电宣布将与博通联手推出增强型CoWoS解决方案 最高可提供96GB的HBM内存

台积电宣布将与博通联手推出增强型CoWoS解决方案 最高可提供96GB的HBM内存

评论