实际上信号的谐波频率比信号本身的重复频率高,是信号快速变化的上升沿与下降沿引发了信号传输的非预期结果。因此,通常约定如果走线传播延时大于20%驱动端的信号上升时间,则认为此类信号是高速信号并可能产生传输线效应。

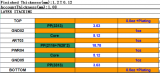

定义了传输线效应发生的前提条件,又如何判断传播延时是否大于20%驱动端的信号上升时间呢?信号上升时间的典型值一般可通过器件手册查出,而信号的传播时间在PCB设计中由实际布线长度和传播速度决定。例如,“FR4”板上信号传播速度大约为6in/ns(1in=2.54 cm),但如果过孔多,器件引脚多,速度将降低,高速逻辑器件的信号上升时间大约为0.2ns,则安全的走线长度将不会超过0.24in。

假设“Tr”为信号上升时问,“TD”为信号线传播延时,有如下经验法则:如果民≥5TD,信号落在安全区域;如果2TD≥Tr≥5TD,信号落在不确定区域;如果Tr≤2TD,信号落在问题区域。对于落在不确定区域及问题区域的信号,应该使用高速电路设计方法。

与低速情况下的数字设计相比,高速数字设计着重强调了数字电路之间用来传输信号的路径和互连,从发送信号芯片到接收信号芯片间的完整的电流路径,包括封装、走线、连接器、插座,以及许多其他的结构。高速数字电路的设计主要研究互连对信号传播的影响、信号间的相互作用,以及和外界的相互作用。

-

pcb

+关注

关注

4391文章

23742浏览量

420762 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44387

发布评论请先 登录

为什么高速信号链路 = 芯片 + PCB + 极细同轴线束三者匹配?

PCB分板切割就选Sycotec高速电主轴的硬核理由

高速PCB铺铜到底怎么铺

高频高速PCB板材材料技术解析与应用趋势

高速PCB布局/布线的原则

高速PCB板的电源布线设计

高速PCB设计基础篇

揭秘PCB阻抗在高速信号传输中的重要性

怎么设计ADS828E的高速PCB板,要注意哪些问题?

应变计的测量范围和精度是如何界定?

pcb的高速是怎样界定的

pcb的高速是怎样界定的

评论