"Cadence Sigrity X 工具已成为我们高速 PCB 设计流程中不可或缺的一部分。它不仅增强了我们的能力,也巩固了我们作为复杂项目首选合作伙伴的声誉。"

——CHRIS HALFORD,ALS 公司首席工程师

Advanced Layout Solutions(ALS)是英国专注于高速 PCB 领域最大的设计公司。面对项目日益增长的复杂性,他们需要更高的精度和更快的设计周期。通过采用 Cadence Sigrity X 信号与电源完整性工具,ALS 彻底革新了其 PCB 设计流程,显著为其欧洲客户减少了设计迭代次数并缩短了产品上市时间。增强的能力巩固了 ALS 作为尖端 PCB 项目 trusted partner 的地位。

作为高速 PCB 开发领域的先锋,ALS 在英国建立了作为首选设计公司的良好声誉。他们的专业知识涵盖众多复杂设计,服务于对精度和创新至关重要的行业。随着客户期望的不断提高以及 PCB 布局日益复杂,ALS 寻求一种强大且尖端的解决方案,以保持竞争优势并提供卓越成果。

业务挑战

高速 PCB 项目日益复杂,导致客户期望值升高

需要更快的设计周期以保持市场竞争优势

由于设计流程过时,存在无法满足客户满意度的风险

设计挑战

难以在设计早期识别信号与电源完整性 (SI/PI) 问题,导致代价高昂的后期返工

由于反复迭代以及性能与成本优化的挑战,导致设计周期冗长

Cadence解决方案

Sigrity X 平台

挑战

如果没有 Cadence Sigrity X 工具,ALS 将难以应对众多设计挑战。现代 PCB 日益增长的复杂性——更高的频率、更紧凑的元件间距以及严苛的电源要求——给传统设计流程带来了压力。

关键问题包括:

难以在设计流程早期识别信号与电源完整性 (SI/PI) 问题,导致代价高昂的后期返工

以所需的精度和速度仿真高速接口和高密度布局的能力有限

由于反复迭代和延迟的故障排除而导致设计周期冗长

在性能、可靠性和成本之间进行权衡取舍的挑战,特别是在优化去耦电容器和电源分配网络 (PDN) 方面

如果没有先进的工具来简化流程并提高仿真精度,ALS 将面临无法满足客户期望的风险——在竞争激烈的市场中,这是他们无法承受的风险。

解决方案

为了应对这些挑战,ALS 将 Cadence Sigrity X 这一尖端信号完整性 (SI) 和电源完整性 (PI) 分析工具融入其工作流程。这些工具为 ALS 提供了一个全面且灵活的框架,以满足下一代 PCB 设计的需求。实施的关键方面包括:

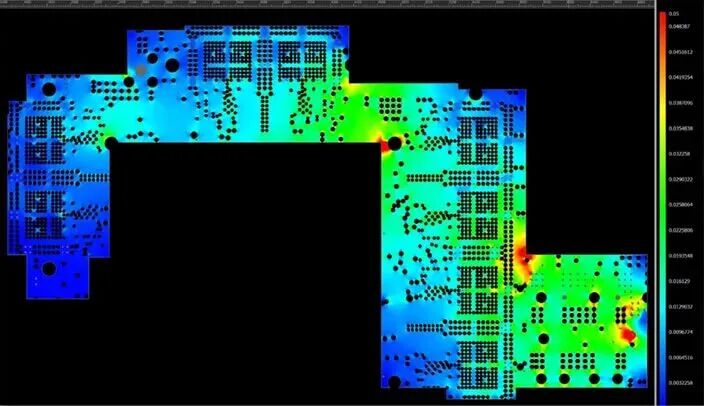

利用在板分析进行早期 SI/PI 问题检测

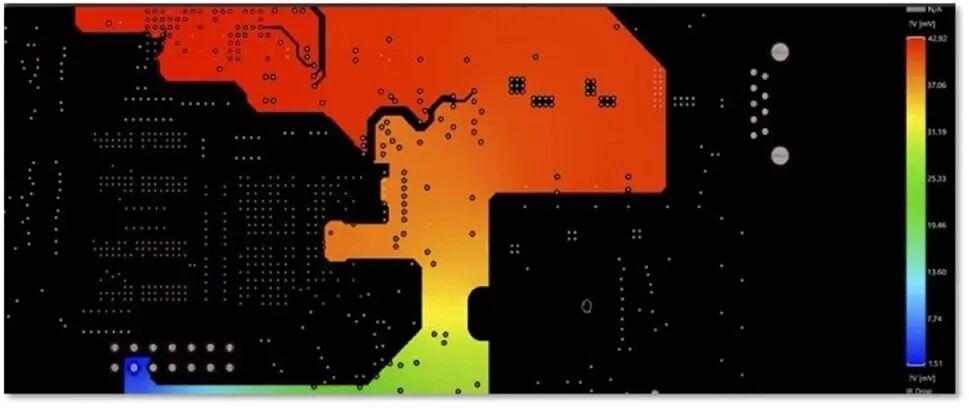

ALS 利用 Sigrity X 的在板分析功能,在 PCB 初始布局阶段检测和解决 SI/PI 问题。通过 Sigrity X PowerDC 仿真,ALS 能够优化层叠结构、铜厚以及整个电源分配网络,通常还能通过减少铜用量或移除不必要的层来发现节约成本的机会。

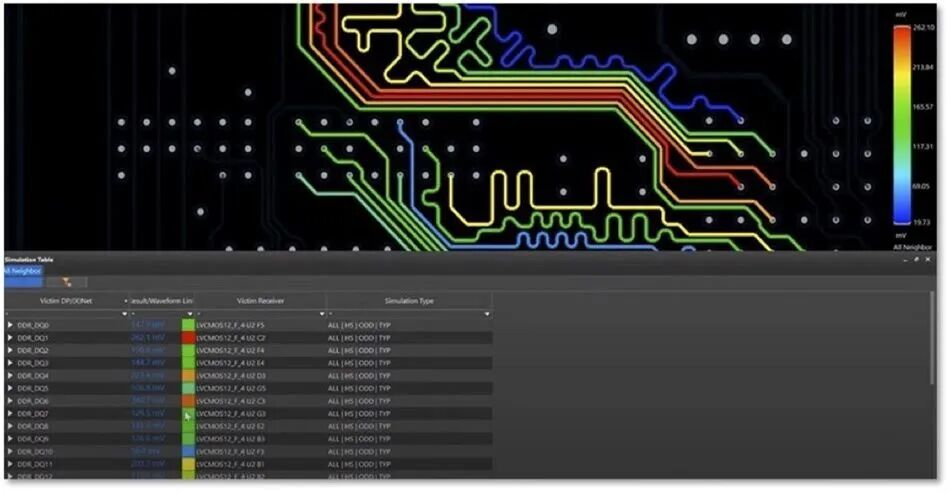

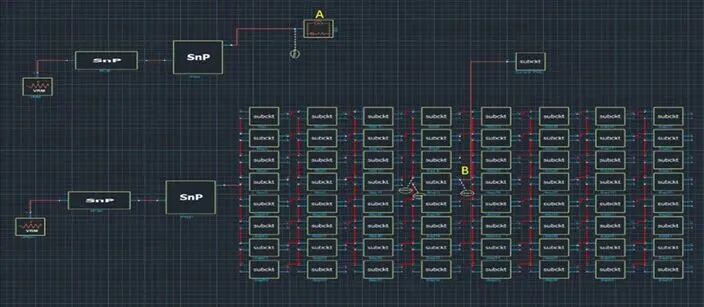

用于高速接口的 Hybrid Plus 3D 求解器

对于复杂的 DDR 接口,ALS 将 Cadence Clarity 3D Solver 的提取功能与 Sigrity X PowerSI 强大的 hybrid solver 方法相结合,后者能够处理数百个端口的仿真。这使得团队在仿真考虑电源影响的 SI 问题时能够平衡精度和效率,确保在密集、高频设计中实现可靠性能。在极端情况下,内存高效且快速的 3D 求解器(如 Clarity 3D Solver)将为 DDR 接口的签核提供额外的保障。

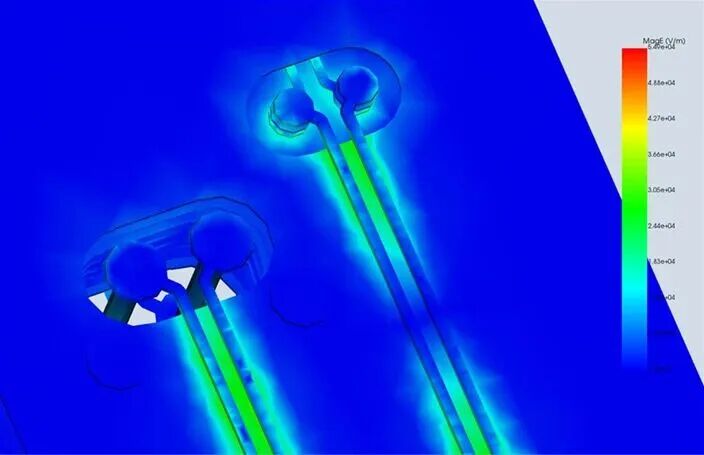

过孔结构优化

过孔设计是影响信号完整性的关键因素,通过 Clarity 3D Solver 仿真得到了增强。通过在设计流程早期优化过孔,ALS 最大限度地减少了信号损耗并消除了潜在问题,从而实现了更顺畅的工作流程和更高质量的成果。

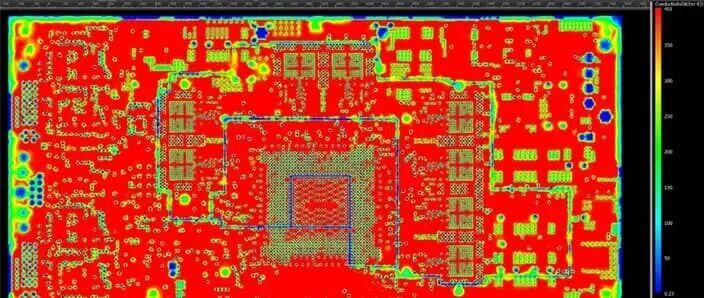

去耦电容器优化

利用 Sigrity X OptimizePI 技术,ALS 通过消除不必要的去耦电容器并重新利用设计空间,实现了性能与成本之间的理想平衡。对成本-性能权衡的交互式评估进一步简化了 PCB 开发流程。

多板、多结构 PDN 验证

Sigrity X SystemPI 技术使 ALS 能够确保互联 PCB 之间的正常供电,全面的交流 (AC)、直流 (DC) 和板间连接分析可防止系统级的电源传输故障。在与 IC 供应商合作时,封装 PDN 模型可以提供从电压调节模块 (VRM) 到跨多块板卡上的多个负载/芯片的完整 PDN 路径。

成果

通过将 Sigrity X 工具集成到工作流程中,ALS 取得了显著成果:

缩短产品上市时间:大幅缩短设计周期,能够更快地向欧洲客户交付多款高速 PCB

提高设计精度:早期问题检测和先进的仿真能力最大限度地减少了错误和迭代,实现了可靠的一次性成功设计

优化成本:去耦电容器优化和电源层削减节省了材料和设计资源,同时保持了性能

增强声誉和客户信心:凭借创新技术能力,ALS 巩固了其作为应对挑战性高速 PCB 项目的 trusted partner 的地位

结论

通过采用 Sigrity X SI/PI 工具,ALS 转变了其高速 PCB 设计方法,积极应对挑战并为客户交付了卓越成果。ALS 与 Cadence 的合作使 ALS 能够突破 PCB 设计的界限,在这个快速发展的行业中确保提供稳健、高效且及时的解决方案。

随着电子设计日趋复杂,ALS 对满足未来需求充满信心。他们与 Cadence 的合作确保持续获得最新工具和专家支持,使他们能够应对更高级的挑战。

-

Cadence

+关注

关注

68文章

1029浏览量

147334 -

PCB设计

+关注

关注

396文章

4939浏览量

95780 -

als

+关注

关注

0文章

22浏览量

19325

发布评论请先 登录

Cadence 与 Google 合作,利用 ChipStack AI Super Agent 在 Google Cloud 上扩展 AI 驱动的芯片设计

Cadence与Google合作,利用ChipStack AI Super Agent在Google Cloud上扩展AI驱动的芯片设计

深入解析FAIRCHILD DM74ALS161B、DM74ALS162B、DM74ALS163B同步四位计数器

德州仪器MSP430i204x/3x/2x混合信号微控制器深度解析

【「玩转高速电路:基于ANSYS HFSS的无源仿真实例」阅读体验】+基础篇

高速差分线驱动芯片SN75ALS191的设计与应用指南

SN65ALS180和SN75ALS180差分驱动器与接收器对的技术解析

深入了解SN65ALS176和SN75ALS176系列差分总线收发器

Cadence公司成功流片第三代UCIe IP解决方案

2025 Cadence 中国技术巡回研讨会即将开启 ——系统设计与分析专场研讨会(上海站)

成功案例 I ALS 利用 Cadence Sigrity X 加速高速 PCB 设计

成功案例 I ALS 利用 Cadence Sigrity X 加速高速 PCB 设计

评论