具有12至14位高分辨率的现代高速数模转换器(DAC)为采用直接调制方案的新型发射器设计奠定了基础。在此类设计中,调制后的传输信号直接在基频上生成。到目前为止,这种方法仅用于生成有线电视系统中正交调幅(QAM)多载波信号的传输,或雷达设备和军事通信系统采用的微波系统的中频信号。现在,进一步发展使得将这些射频(RF)DAC用于其他类型的通信系统成为可能。

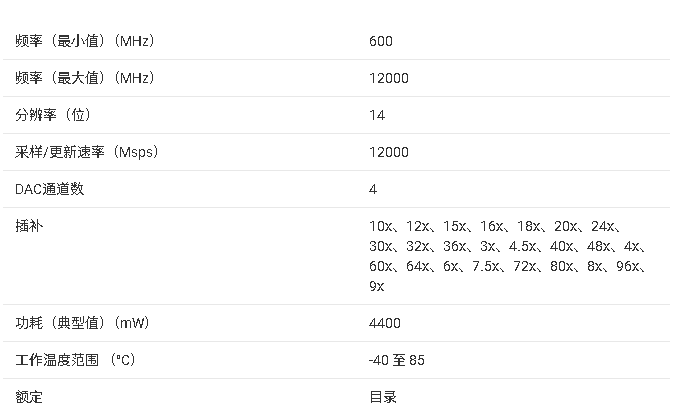

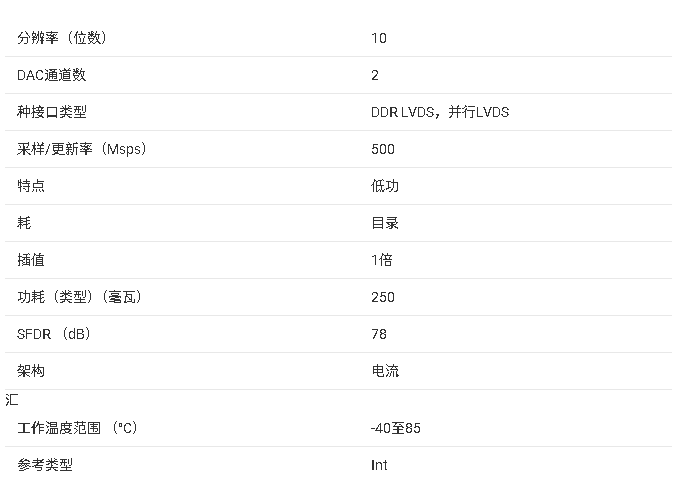

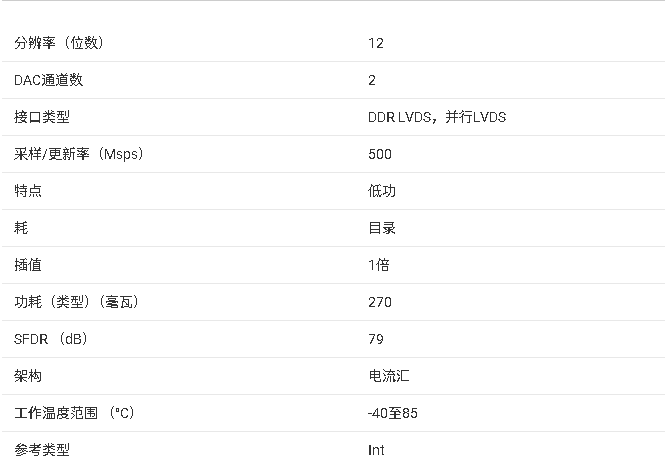

如今,分辨率为12至14位的CMOS RF DAC具有超过4Gsps的更新速率。结合采用CMOS技术的信号处理组件,它们可以以数字方式生成高达2GHz的传输信号。

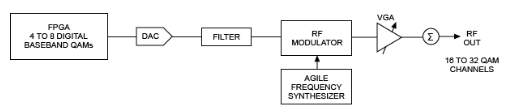

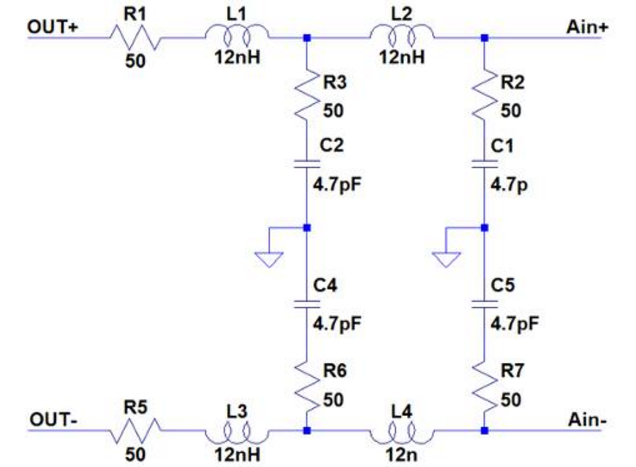

图1显示了模拟多载波QAM发射路径的典型框图。要生成多个QAM传输通道,必须使用加法器将多个单独的传输链组合在一起。此外,每个RF调制器都通过自己的频率合成器供电。由于每个功能块都有自己的元件容差、温度漂移、转换损耗等,因此在系统配置过程中必须通过执行容差计算来考虑这些因素。

图1.模拟多载波QAM发射器框图。

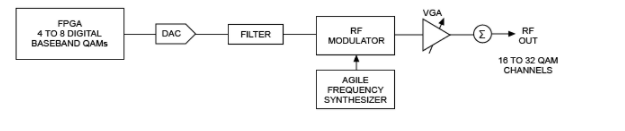

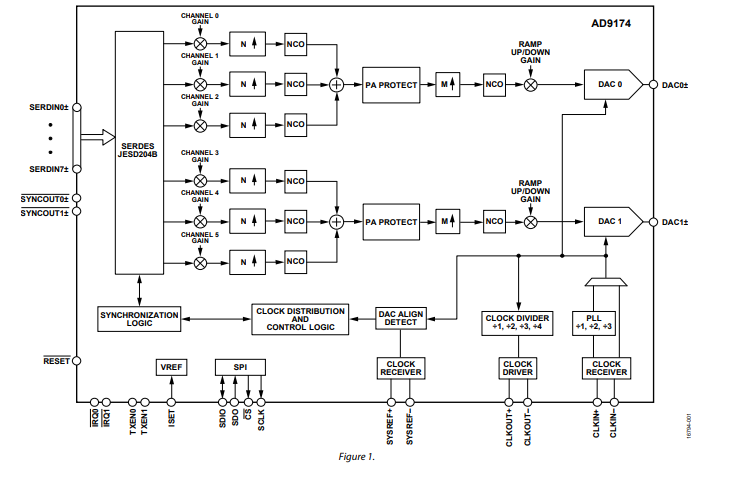

图2显示了数字多载波QAM发射路径的框图。例如,生成 32 个 QAM 通道不需要组合多个传输路径,单个传输路径可以处理这个问题。在这种情况下,传输路径由一个带有下游滤波器的RF DAC和一个VGA组成。这也消除了在每个发射分支中安装RF调制器或频率合成器的需求。

图2.带RF DAC的数字多载波QAM发射器框图。

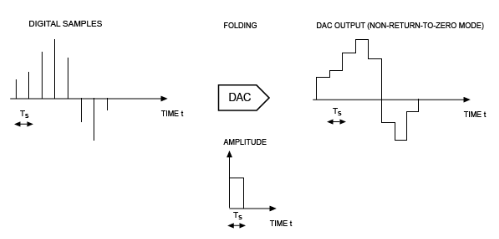

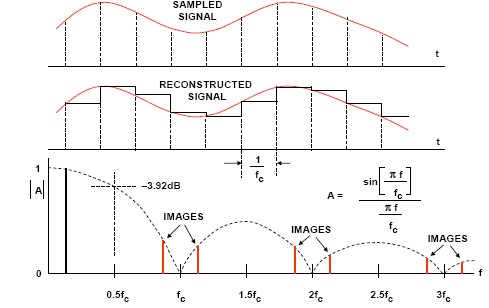

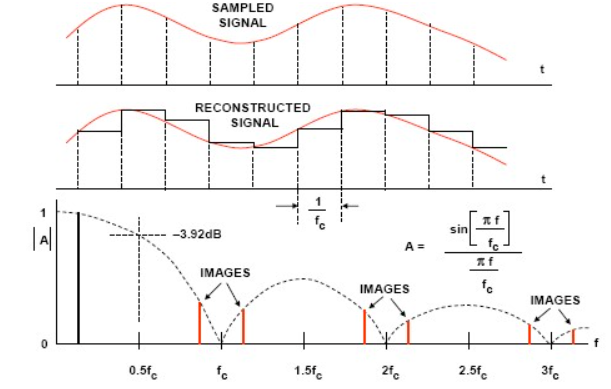

采样理论使得在时域和频域中描述DAC的输出信号成为可能。图3显示了DAC的输出信号。这里,这是一个矩形脉冲序列,其幅度与相应的数字值相匹配。由于这些矩形脉冲的持续时间是有限的,因此Ts> 0 时,这将产生输出频谱。在频域中,该输出频谱用sinx/x函数描述。sinx/x 函数,也称为 sinc 函数,在频率 f 处为零s= 1/Ts.

图3.DAC输出信号为一系列矩形脉冲。Ts= 采样时间。

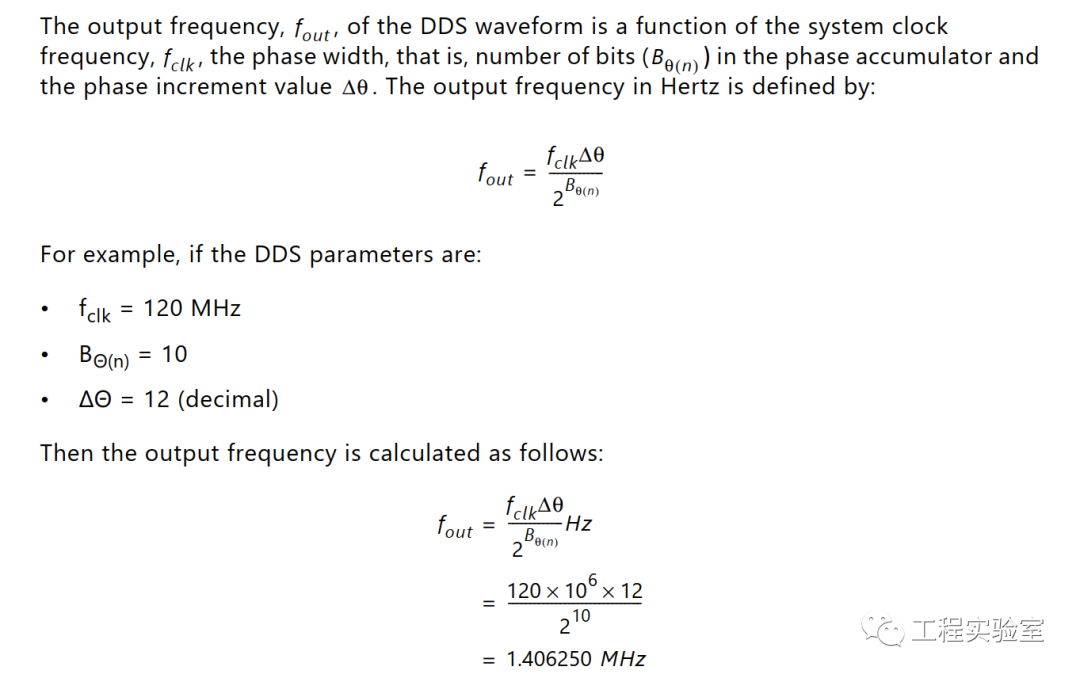

在频域中,频率为 f 的理想正弦信号0在 f 处有一条谱线0.如果正弦信号现在由DAC产生,除了f处的谱线0,在更高的频率下会产生额外的变频产物(见图4)。

图4.在频率范围内描述的正弦信号,以及用DAC生成的信号的输出频谱。

这些变频产品可以使用公式1来描述:

|K × fs ± f0| K = 1, 2, 3, …

等式2定义了N阶的“奈奎斯特区”。

[(N - 1) × fs/2, N × fs/2] K = 1, 2, 3, ...

如图4所示,DAC输出信号不是由f处的单条谱线组成。0;相反,它还具有更高频率的更多频谱分量。这意味着必须对DAC的输出信号进行滤波。除了这些杂散发射之外,还会产生额外的变频产品。例如,这些是由DAC的非线性输出特性引起的。

利用在较高奈奎斯特区产生额外频谱分量的事实,以便使用“亚奈奎斯特DAC”在高输出频率下产生信号。为此,例如,用带通滤波器滤除信号的第一个谐波。与直接在基频上生成输出信号的DAC相比,这里的优势在于基带中的数据速率更低,耗散损耗更小。

MAX5879 RF DAC具有14位分辨率和2.3Gsps采样速率,非常适合基站。此外,MAX5879的输出脉冲响应可以设置为四种不同的工作模式,我们将更仔细地研究(图5)。

图5.MAX5879 RF DAC在a)NRZ模式下的脉冲响应;b) RZ 模式;c) 射频模式;和 d) 射频模式。

默认脉冲响应为非归零 (NRZ) 脉冲响应(图 5a)。采样周期与时间 T 相同s.sinc函数的零位于更新时钟速率f的倍数时钟= 1/Ts.当使用此脉冲响应时,DAC的频率响应会产生以下功能:

ANRZ = A0[sin(πfOUTTs)/(πfOUTTs)]

f外为DAC输出频率,Ts= 1/f时钟是DAC更新时钟速率,A0是幅度因子。

在归零 (RZ) 模式下,DAC 输出幅度在 50% 的时间内为零(图 5b)。这会产生以下频率响应:

ARZ = A0/2[sin(πfOUTTs/2)/(πfOUTTs/2)]

第三个可编程脉冲响应是射频(RF)模式。如图5c所示,DAC输出信号在时钟周期中途的每个时钟周期内发生反相。DAC的频率响应如下所述:

ARF = A0[sin(πfOUTTs/2)/(πfOUTTs/2) × sin(πfOUTTs/2)]

第四种新的操作模式是RFZ模式,代表“射频归零模式”。其脉冲响应如下:

ARFZ = A0/2[sin(πfOUTTs/4)/(πfOUTTs/4) × sin(πfOUTTs/4)]

图6给出了MAX5879在四种工作模式下的频率响应。该图的x轴显示了归一化为输入数据采样率的输出频率。从 0 到 0.5 的范围描绘了第一个奈奎斯特区。NRZ 模式在第一奈奎斯特区提供最大的输出信号。相对而言,RZ模式在第一和第三奈奎斯特区具有最平坦的频率响应。RF模式的特点是第二和第三奈奎斯特区的最大输出功率。此外,第二奈奎斯特区的频率响应比其他两种工作模式的上升更平坦。在所有工作模式中,RFZ模式在所有奈奎斯特区中具有最平坦的脉冲响应。

图6.MAX5879 RF DAC的归一化频率响应适用于四种可能的工作模式。

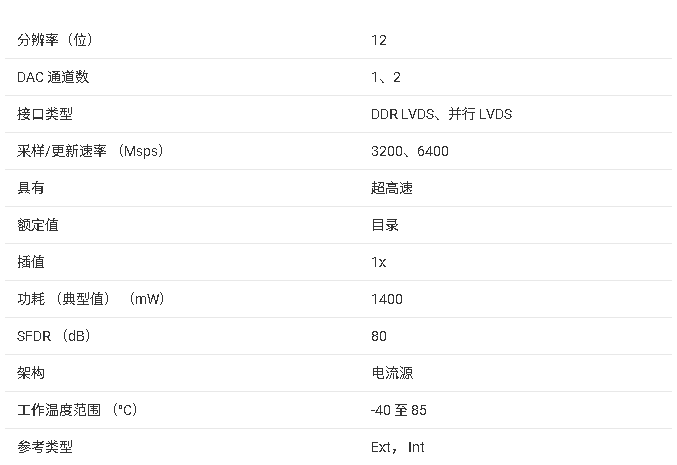

MAX5882直接采样DAC输出端的更新速率为4.6Gsps。这使得使用直接调制来生成频率范围为47MHz至1003MHz的传输信号成为可能。MAX5882专为有线电视应用而开发,符合数据电缆服务接口规范(DOCSIS)第3版。®

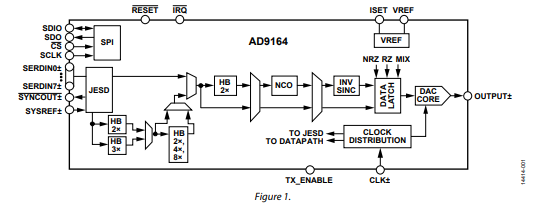

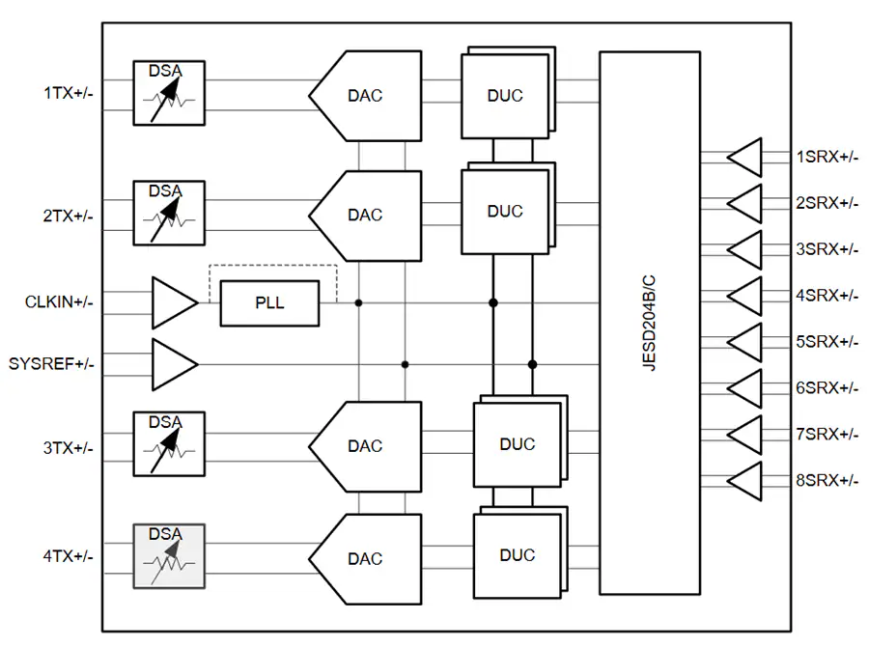

利用数字上变频器 (DUC) 简化 DAC 控制

到目前为止,要为高速DAC提供高数据速率,需要使用具有高额定功率的现场可编程门阵列(FPGA)。数据的数字上转换在FPGA中完成。这种解决方案的缺点包括高耗散损耗和较高的系统成本。此外,升级系统以获得更高的调制方案只能非常困难。如果改变发射系统的功能分布,以便使用专用芯片实现数字上变频功能,则可以使用额定功率较低的FPGA。这反过来又降低了系统成本和耗散损耗。副作用是,这简化了RF DAC和FPGA之间的接口,因为DUC非常适合RF DAC。

MAX5880 QAM调制器和DUC专为电缆系统应用而开发。此外,它还具有传输信号的数字预失真功能。其接口经过优化,可满足MAX5879和MAX5882高速DAC的要求。

此后,Maxim将MAX5880和MAX5882的功能集成到单个封装中,现在提供MAX5862/MAX5860高密度QAM调制器(集成DUC和RF DAC),分别支持最大32/128个QAM通道。

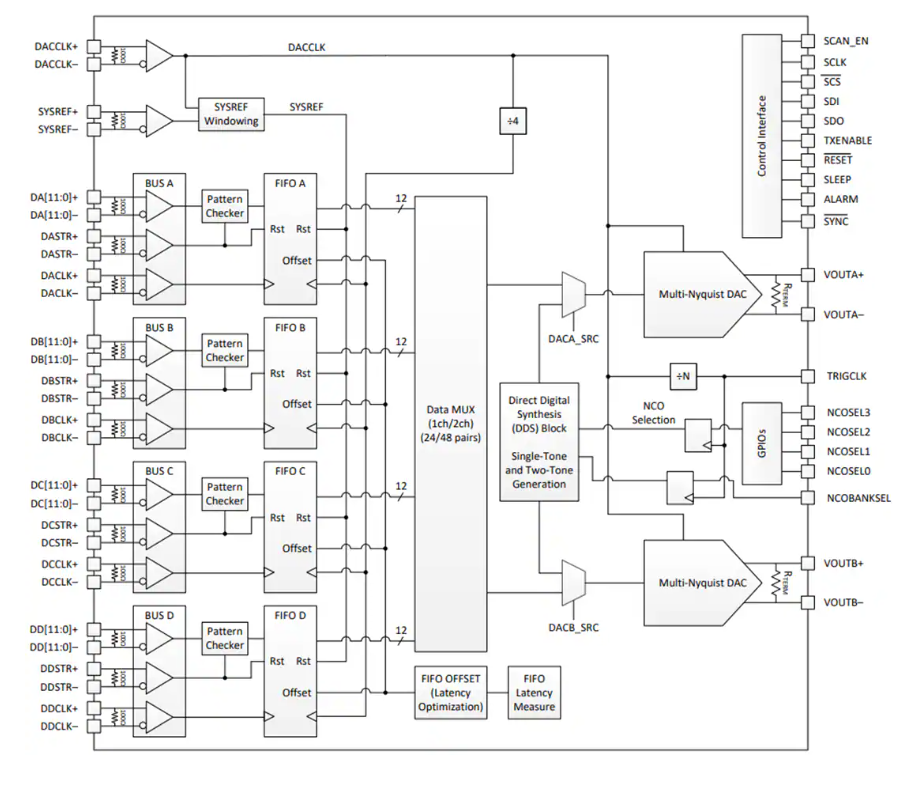

使用多个DAC的应用中的时钟同步

现代通信系统经常组合多个传输路径。这就对同步各个RF DAC的时钟提出了特殊要求。使用具有多路复用输入(MUXDAC)的DAC时,还必须考虑这些特殊要求。

同步多个DAC需要考虑以下问题:

必须检测上升时钟边沿的相对相位角。

各个DAC之间的相对相位角必须改变,直到DAC以正确的相位关系相互同步。

MAX19692 RF DAC具有1路多路复用输入。在这里,四个输入信号组合成一个输出信号。因此,输入数据速率是DAC更新数据速率的4/2。因此,3.575Gsps的更新数据速率导致最大输入数据速率为<>Msps。DAC接收数据,可选择可编程,具有数据时钟的上升沿或上升沿和下降沿。借助数字分频器,DAC从施加的输入时钟产生时钟信号。当DAC导通时,当数字时钟分频器启动时,N分频器可以处于任何状态。当这些DAC中的几个组合在单个发射路径上时,每个DAC都可以以不同的分频器状态启动N分频器。由于各个DAC接受具有不同数据边沿的输入数据,因此每个DAC的输出数据与其他DAC的输出数据偏移一个或多个时钟周期。重置时钟分频器只是解决此问题的部分方法;还需要检测操作过程中出现的任何错误分频器状态。这是通过测量和校正各种相关系来实现的。

在最简单的情况下,各个数据时钟输出之间的相位误差可以使用XOR门来实现。最复杂的解决方案是采用鉴频鉴相器,例如使用锁相环(PLL)时已知的鉴频检波器。

在这种情况下,每个DAC使用单独的PLL。使用PLL比较数据输出的相位角和参考频率。来自各种DAC的PLL具有公共参考频率。这个过程可以实现锁相或相位同步星座。然而,这种配置有两个缺点:额外的模块导致更高的成本,而PLL产生的相位噪声会限制系统性能。

MAX2870/MAX2871频率合成器保持优异的相位噪声性能,工作频率范围为23.5MHz至6000MHz。这是通过覆盖3000MHz至6000MHz频率范围的集成压控振荡器(VCO)和内部分频器(分频因子为1至128)实现的,该分频器将输出分频到所需频率。为了实现如此广泛的范围,该模块中集成了多个VCO,开发人员可以自动或手动选择它们。该器件可工作在整数N分频模式和小数N分频模式 由于这些特性,MAX2870/MAX2871可用作RF DAC的合成器。

结论

RF DAC使得使用单个DAC产生50MHz至1GHz的宽带传输信号成为可能。由于这一成就,具有直接调制方案的新型发射器设计成为可能。过去,这种方法仅用于生成有线电视系统中正交幅度调制(QAM)多载波信号的传输,或雷达设备和军事通信系统采用的微波系统的中频信号。新一代DAC也可用于其他通信系统。当信号以数字方式生成时,由模拟干扰引起的元件公差、温度漂移、转换损耗和失真只起很小的作用。此外,对于数字生成的QAM信号,还可以基本消除本振(LO馈通)的正交误差和串扰。必须特别注意考虑数字系统可能产生的杂散发射和噪声产物。其他优势包括更小的元件尺寸和更低的功耗,从而实现更高的集成密度。

审核编辑:郭婷

电子发烧友App

电子发烧友App

评论