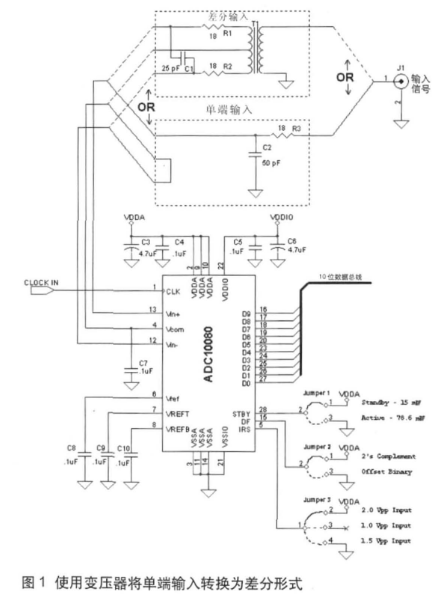

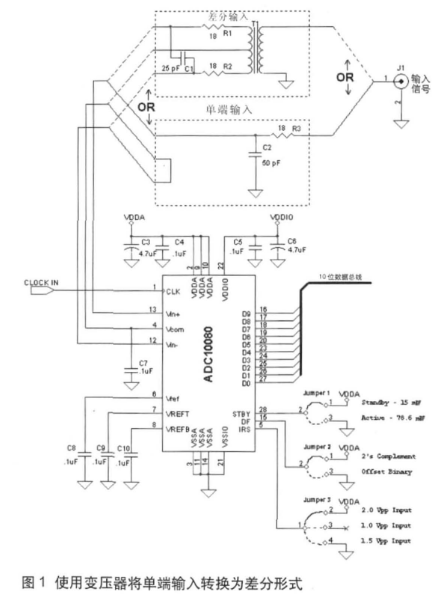

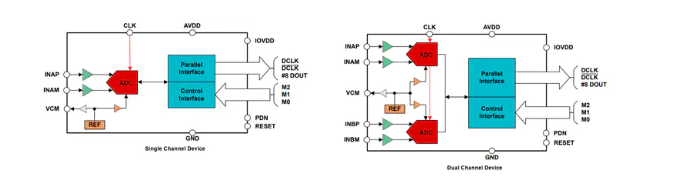

大多数现代高性能ADC使用差分输入抑制共模噪声和干扰。 由于采用了平衡的信号处理方式,这种方法能将动态范围提高2倍,进而改善系统总体性能。 虽然差分 输入型 ADC也能接受单端输入信号,但只有在输入差分信号时才能获得最佳ADC性能。

2023-02-23 11:58:39 5135

5135

如何实现高速时钟信号的差分布线

在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只有一个输出端的时钟信号线,如何实现差分布线?

2009-04-15 00:26:37 3623

3623 我在知乎看到了多bit信号跨时钟的问题,于是整理了一下自己对于跨时钟域信号的处理方法。

2022-10-09 10:44:57 8118

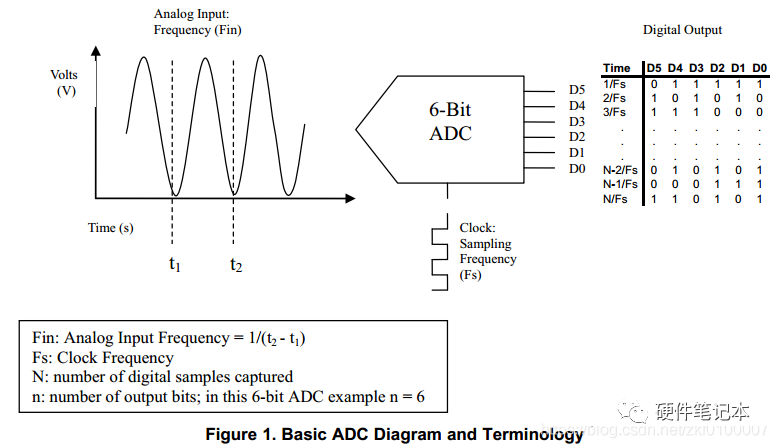

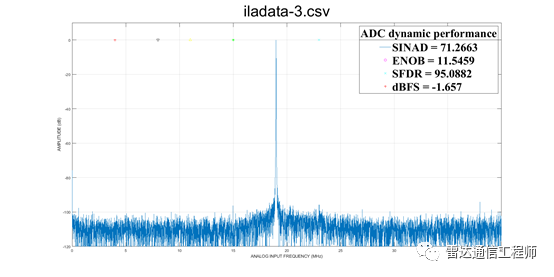

8118 本文的目的是介绍高速ADC相关的理论和知识,详细介绍了采样理论、数据手册指标、ADC选型准则和评估方法、时钟抖动和其它一些通用的系统级考虑。另外,一些用户希望通过交织、平均或抖动(dithering)技术进一步提升ADC的性能。

2023-03-16 09:15:15 6525

6525 今天我们将讨论时钟如何影响精密 ADC,涉及时钟抖动、时钟互调和时钟的最佳 PCB 布局实践。

2023-04-11 09:13:22 2034

2034 本文的目的是介绍高速ADC相关的理论和知识,详细介绍了采样理论、数据手册指标、ADC选型准则和评估方法、时钟抖动和其它一些通用的系统级考虑。 另外,一些用户希望通过交织、平均或抖动(dithering)技术进一步提升ADC的性能。

2023-04-15 14:00:51 3222

3222

本期,为大家带来的是《用于窄带匹配高速射频 ADC 的全新方法》,介绍了一种用于窄带匹配高速射频 ADC 的全新方法,以解决高中间频率系统中 ADC 前端窄带匹配的设计难题,可在 ADC 额定带宽内应用,能提升 ADC 性能、减少模拟停机时间。

2026-01-04 15:56:47 1674

1674

ADC0809clk端是芯片的时钟信号输入端,一般为500khz,外围电路怎么接呢,如何才能获得这个频率的信号呢

2013-04-01 20:18:48

描述TIDA-01016 是一款适合高动态范围高速 ADC 的时钟解决方案。射频输入信号由高速 ADC 直接采用射频取样法捕获。ADC32RF80 是一款双通道 14 位 3GSPS 射频取样

2018-09-30 09:26:09

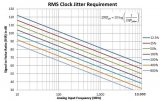

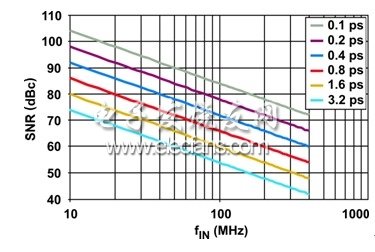

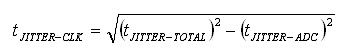

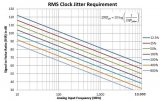

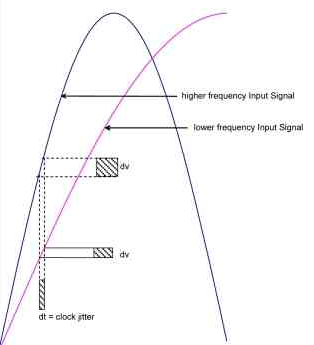

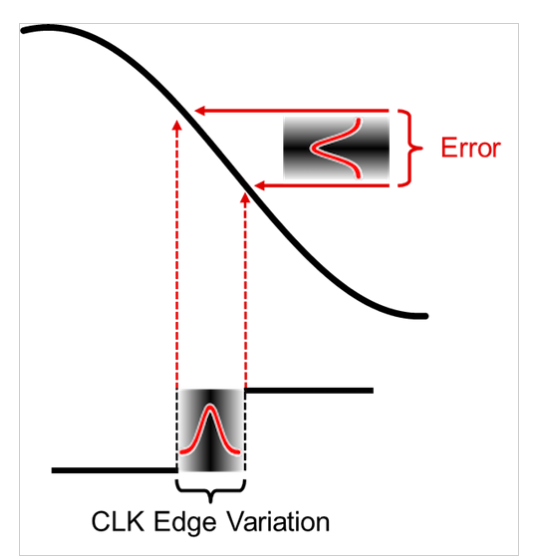

对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。那么时钟抖动会对高速ADC的性能有什么影响呢?

2021-04-08 06:00:04

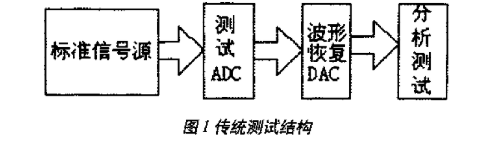

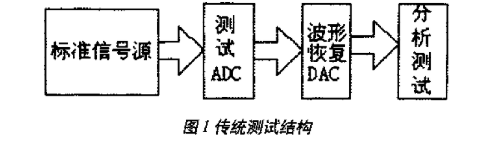

随着数字信号处理技术和数字电路工作速度的提高,以及对于系统灵敏度等要求的不断提高,对于高速、高精度的 ADC、DAC 的指标都提出了很高的要求。比如在移动通信、图像采集等应用领域中,一方面要求

2018-04-03 10:39:35

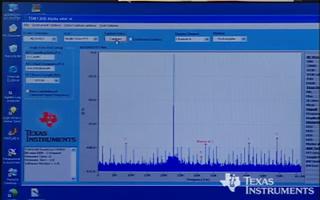

还可能表现为宽带噪声。这两种噪声都取决于所使用的振荡器和系统时钟电路。即使把理想的模拟输入信号提供给理想的ADC,时钟杂质也会在输出频谱上有所表现,如图2所示。由该图可以推论出是电源引脚。用一个模拟电源

2019-12-11 18:12:18

还可能表现为宽带噪声。这两种噪声都取决于所使用的振荡器和系统时钟电路。即使把理想的模拟输入信号提供给理想的ADC,时钟杂质也会在输出频谱上有所表现,如图2所示。由该图可以推论出是电源引脚。用一个模拟电源

2019-12-25 18:03:49

影响高速信号链设计性能的机制是什么?高速ADC设计中的PCB布局布线技巧有哪些?

2021-04-21 06:29:52

。近年来,NS、Atmel等公司都开发出了高速ADC,比如ADC08D1000、AT84AS003TP等,它们都是经采样后分多路降速进行传输。目前,多路并行数据传输存储成为高速信号采集系统的主流趋势。

2019-07-05 08:11:34

本文分析了高速电路设计中的信号完整性问题,提出了改善信号完整性的一些措施,并结合一个VGA视频分配器系统的设计过程,具体分析了改善信号完整性的方法。

2021-06-03 06:22:05

本文分析了高速电路设计中的信号完整性问题,提出了改善信号完整性的一些措施,并结合一个VGA视频分配器系统的设计过程,具体分析了改善信号完整性的方法。

2021-06-04 06:16:07

第三级寄存器,由于第二级寄存器对于亚稳态的处理已经起到了很大的改善作用,第三级寄存器在很大程度上可以说只是对于第二级寄存器的延拍,所以意义是不大的。02方法二:异步双口RAM处理多bit数据的跨时钟域,一般

2021-03-04 09:22:51

描述ADC12D1600RFRB 参考设计提供了展示高速数字转换器应用(其中整合了时钟、电源管理和信号处理)的平台。此参考设计利用 1.6 GSPS ADC12D1600RF 器件、板载 FPGA

2018-12-17 16:16:17

,高速先生则默默的看向本文的标题:如何用电源去耦电容改善高速信号质量?

没错,高速先生做过类似的案例。

如前所述,我们的Layout攻城狮经验丰富,在他的努力下,找到了另外一个对比模型,信号管脚周围只

2025-05-19 14:28:35

STM32f103的时钟有四个来源高速外部时钟信号(HSE)、低速外部时钟信号(LSE)、高速内部时钟信号(HSI)和低速内部时钟信号(LSI),图中分别用蓝色的①~④标注。①HSE高速外部时钟:由

2021-08-18 06:01:00

描述ADC12D1600RFRB参考设计提供了展示高速数字转换器应用(其中整合了时钟、电源管理和信号处理)的平台。此参考设计利用 1.6 GSPS ADC12D1600RF 器件、板载 FPGA

2022-09-20 07:01:22

,所以意义是不大的。 方法二:异步双口RAM 处理多bit数据的跨时钟域,一般采用异步双口RAM。假设我们现在有一个信号采集平台,ADC芯片提供源同步时钟60MHz,ADC芯片输出的数据在

2021-01-08 16:55:23

你好,我们有个需求计划使用两个高速ADC,ADS5546,一个用于采集电压,一个用于采集电流,最终测量出实时的V-I曲线,所以想确认下,两个ADC同时采集数据时:

1、两个高速ADC的CLK时钟

2024-11-18 06:47:20

DN1013- 了解时钟抖动对高速ADC的影响

2019-07-17 06:41:39

,送个例子,以时钟发生器AD9516的两路输出为例加以说明吧~一路100MHz输出连接到一个ADC,另一路2 5 M H z 输出(1/4×fSAMPLE)为一个FPGA提供时钟信号。两路输出时钟的上升沿

2018-10-26 11:05:01

的谐波注入法。表1,IEC 61000-3-2 谐波限值闭环调谐通常是一种降低谐波失真、改善 THD 的有效方法。不过,我看到过有 PFC 设计通过了 THD 测试,但无论工程师如何努力调谐控制环路,也无

2018-09-12 09:47:28

Common-Mode Rejection

有以下几个问题:

1、ADC需要一个时钟信号,这个时钟信号可以自己外接一个晶振电路吗?不使用Digital Host的时钟信号。

2、我准备先用FPGA开发板初步做一个

2024-11-26 07:11:39

速转换,降低速率后的数据可提供给内部DSP处理单元进行处理。Stratix2系列FPGA的另外一个优点是其内部具有专门的高速数字锁相环电路,能够产生可供ADC电路使用的时钟信号。图3所示为

2019-04-30 07:00:11

介绍了一种基于现场可编程门阵列(FPGA)和第二代双倍数据率同步动态随机存取记忆体(DDR2)的高速模数转换(ADC)采样数据缓冲器设计方法,论述了在Xilinx V5 FPGA中如何实现高速同步

2010-04-26 16:12:39

我继续使用PS结构时钟为我的PL生成时钟信号。如何配置PLL环路带宽?是否还有其他方法可以通过配置改善输出信号的抖动?关于抖动,在PS的“自定义IP”GUI中配置并不多,...由于“时钟向导IP”有一

2020-08-19 06:09:57

目前的实时信号处理机要求ADC尽量靠近视频、中频甚至射频,以获取尽可能多的目标信息。因而,ADC的性能好坏直接影响整个系统指标的高低和性能好坏,从而使得ADC的性能测试变得十分重要。那要怎么测试高速ADC的性能?

2021-04-14 06:02:51

第二级寄存器的延拍,所以意义是不大的。02方法二:异步双口 RAM处理多 bit 数据的跨时钟域,一般采用异步双口 RAM。假设我们现在有一个信号采集平台,ADC 芯片提供源同步时钟 60MHz,ADC

2020-10-20 09:27:37

测量高速信号快速的、比较干净的测量方法是什么

2021-05-07 07:13:16

DC1075A,演示电路1075是用于高速ADC的时钟分频器。每个组件包括一个时钟分频器,后面是一个用于产生尖锐时钟边沿的重定时级

2019-02-21 09:45:45

小弟最近项目中要对200KHz的超声波信号进行采样,采样时长越100us,无奈MCU自带的ADC采样率最高才200ksps,所以希望用MCU外带一块高速ADC来实现。因为后续处理要求精度比较高,所以

2018-09-27 11:45:20

的ADC同时采样同一个模拟信号,希望采样后重构此模拟信号。有两个问题请教。1.每个ADC的时钟如何处理比较合适?看论文,主要介绍的是同一个频率时钟500MHz,每个相位差90°。如果这样,采样后数据如何同步,对齐,还原出原来的信号?2.如果每个ADC的时钟同频率,相位差不是90°,是随机的。

2018-07-24 10:45:54

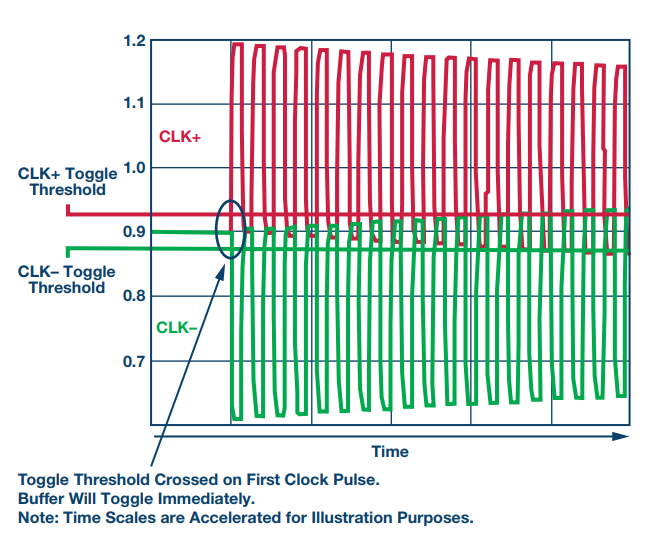

包含千兆采样率ADC的系统设计会遇到许多复杂情况。面临的主要挑战包括时钟驱动、模拟输入级和高速数字接口。本文探讨了如何才能克服这些挑战,并给出了在千兆赫兹的速度下进行系统优化的方法。在讨论中,时钟

2019-05-30 05:00:04

摘 要:本文提出了一种低压工作的高速10bit Pipelined ADC。采用自举时钟采样和Cascode频率补偿等方法,该ADC可以在低电压下工作,并达到较高的带宽。该ADC在HJTC 0.18-μm CMOS 数模混合工

2008-11-14 15:37:29 0

0 以1Gsps高速捕捉信号的ADC

2009-04-16 23:35:23 12

12 本文介绍了一种基于信号完整性计算机分析的高速数字信号 PCB板的设计方法。在这种设计方法中,首先将对所有的高速数字信号建立起PCB板级的信号传输模型,然后通过对信号完

2009-04-25 16:49:13 37

37 在高中频ADC应用中,如何改善增益平坦度同时又不影响动态性能:摘要:本文指导用户选择适当的变压器,用于高速模/数转换器(ADC)前端的信号调理。本文还阐述了如何合理选择无

2009-09-25 08:22:23 23

23 高速信号、时钟及数据捕捉:数据转换系统背后的运作原理— 作者:Ian King 美国国家半导体公司应用技术工程师随着仿真/数字转换器的数据转换取样率提高至每秒千兆个取

2009-09-25 10:42:19 0

0 本文主要讨论采样时钟抖动对ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

2009-11-27 11:24:07 15

15 本文提出了一种低压工作的高速10bit Pipelined ADC。采用自举时钟采样和Cascode频率补偿等方法,该ADC可以在低电压下工作,并达到较高的带宽。该ADC在HJTC 0.18-μmCMOS 数模混合工艺下

2009-12-14 09:43:07 18

18 摘要:ANSI EIA/TIA-644标准定义的低电压差分信号(LVDS)非常适合包括时钟分配、点对点以及多点之间的信号传输。本文描述了使用LVDS将高速通讯信号分配到多个目的端的方法。

2009-04-24 16:05:19 2002

2002

摘要:ANSI EIA/TIA-644标准定义的低电压差分信号(LVDS)非常适合包括时钟分配、点对点以及多点之间的信号传输。本文描述了使用LVDS将高速通讯信号分配到多个目的端的方法。

2009-05-01 11:14:27 1918

1918

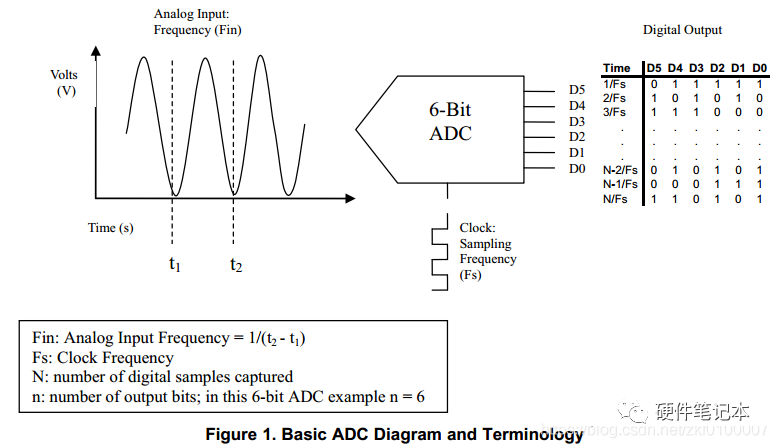

高速ADC,什么是高速ADC

背景知识:

随着计算机技术、通信技术和微电子技术的高速发展,大大促进了ADC技术的发展,ADC作为模拟量与数据量接

2010-03-24 13:28:01 10318

10318 时钟IC改善通信基础设施时序信号链的性能-- AD9553

AD9553时钟发生器提供引脚编程模式和可定制的 SPI 编程模式,有利于 GPON、OC-48光纤网络和无线

2010-05-24 10:36:10 981

981 本文简要介绍了SSC扩频时钟的基本概念以及如何使用力科示波器进行信号的扩频时钟的测试。

2011-05-17 11:23:34 6000

6000

跨时钟域信号的同步方法应根据源时钟与目标时钟的相位关系、该信号的时间宽度和多个跨时钟域信号之间的时序关系来选择。如果两时钟有确定的相位关系,可由目标时钟直接采集跨

2012-05-09 15:21:18 63

63 新型ADC正在朝着低功耗、高速、高分辨率的方向发展,新型流水线结构正是实现高速低功耗ADC的有效方法。而MAX1200则是采用这一新技术的高速、高精度、低功耗ADC的代表。

2012-07-09 15:04:51 4992

4992

TIDA-01015 是一款适合高速直接射频采样 GSPS ADC 的时钟解决方案参考设计。该参考设计展示了采样时钟在为第二奈奎斯特区域输入信号频率实现高 SNR 方面的重要性。ADC

2016-01-20 15:00:41 0

0 了解高速ADC时钟抖动的影响将高速信号数字化到高分辨率要求仔细选择一个时钟,不会妥协模数转换器的采样性能(ADC)。 在这篇文章中,我们希望给读者一个更好的了解时钟抖动及其影响高速模数转换器的性能

2017-05-15 15:20:59 13

13 任何通过时钟电路进入ADC的噪声都能直接到达输出端。ADC中此电路的噪声机制可认为是一个混频器。当看到噪声时,以这种方式考虑输入就真正能洞察一切了。通过时钟输入进入ADC的噪声频率将混入模拟输入信号,并出现在转换器输出端的FFT中。

2017-09-14 17:17:12 8

8 本文主要讨论采样时钟抖动对 ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。 ADC 是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定了

2017-11-27 14:59:20 18

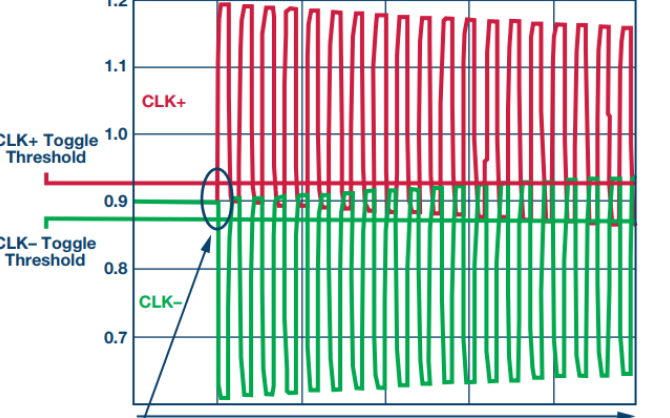

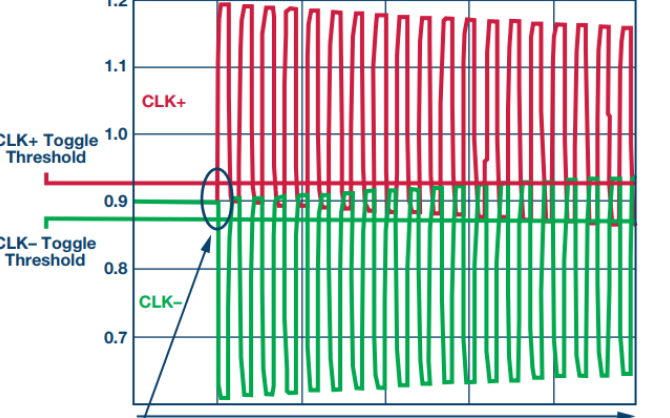

18 ADC的采样时钟输入端(CLK+和CLK−)。 通常,应使用变压器或电容将该信号交流耦合到CLK+引脚和CLK−引脚内。这两个引脚有内部偏置,无需其它偏置。 高速、高分辨率ADC对时钟输入信号的质量非常敏感。

2017-12-19 04:10:01 5918

5918

本文将为您介绍如何通过改善ADC的孔径抖动来进一步提高ADC的信噪比。文章将重点介绍如何对时钟信号的转换速率进行优化。

2018-05-14 08:59:27 14

14 低相位噪声时钟解决方案的ADS5483和其他高速ADC设备使用CDCE72010时钟合成器芯片。通过适当的配置,CDCE72010可以与高速ADC一起使用,以实现理想的性能;该器件也适用于直接实现印刷电路板(PCB)设计。

2018-05-16 14:33:53 14

14 本应用注释讨论了如何通过设计正确的时钟电路和良好的模拟输入网络,来优化高速流水线ADC的性能,以及如何将ADC的高速不失真的数据输送到FPGA或ASIC上。

2018-05-18 10:34:32 10

10 本应用注释讨论了如何通过设计正确的时钟电路和良好的模拟输入网络,来优化高速流水线ADC的性能,以及如何将ADC的高速不失真的数据输送到FPGA或ASIC上。

2018-05-18 10:41:22 0

0 新的高速ADC配备了一个大的模拟输入带宽(约三至六倍的最大采样频率),因此它们可以用于欠采样应用。ADC设计的最新进展显著地扩展了可用的输入范围,使得系统设计者可以消除至少一个中频级,这降低了成本

2018-05-24 08:44:05 18

18 TI最近推出了一套适合于高速、高IF采样模数转换器(ADC)的设备,如ADS583,它能够采样多达135个MSPS。为了实现这些高性能设备的全部潜力,系统必须提供极低的相位噪声时钟源。CDCE72010时钟合成器芯片提供了现实的时钟解决方案,以满足对高速ADC的严格要求。

2018-05-28 09:09:47 11

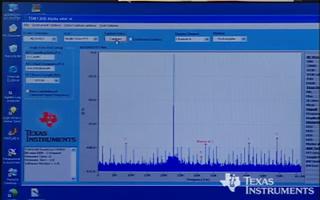

11 在本视频中, Lin Wu 将演示如何使用时钟驱动高速 ADC

2018-06-13 01:54:00 6735

6735

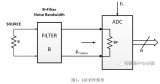

根据定义,高速模数转换器(ADC)是对模拟信号进行采样的器件,因此必定有采样时钟输入。

2019-04-15 17:12:04 3309

3309

1/14HZ = 71.4ms,一个周期采样6000个点,则每两个点之间的采样间隔为:71.4ms/6000 = 71.4 / 6 us;

选择ADC的采样周期为71.5,则ADC时钟频率为:71.4 /(6 * 71.5)≈ 6MHZ。

2019-10-14 16:22:06 21431

21431

高速ADC的进步,直接促使3G基站(如WCDMA ,TD-SCDMA,UMTS)接收(RX)和发送(TX)通路的性能改善。随着新基站设计要求低功率工作和小尺寸,对信号链路元件的热性能提出额外的要求。要求ADC低功率,高性能小尺寸。节省板空间的热耗。

2019-11-05 16:18:51 8794

8794

器件预期性能的最大化。一个颇具挑战性的输入条件是:对ADC输入模拟信号进行测量、驱动和接口连接。本文将探讨一些对于高速 ADC进行有效接口连接的技术,从而使ADC实现性能最佳化。

2020-04-12 11:18:46 4364

4364

高速ADC是信号处理机的不可欠缺的组成部分,其性能的好坏对信号处理系统的整体性能也至关重要。通常ADC的技术参数是由生产厂商提供,可作为设计的重要依据,但是在电路板上形成的ADC模块的性能如何,还与

2020-08-01 11:35:54 4468

4468

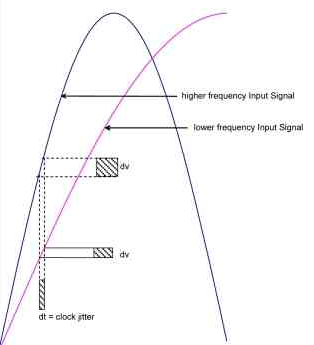

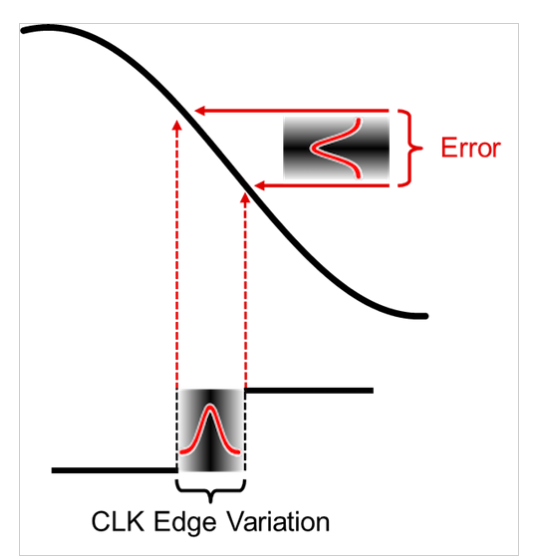

对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。借助本文,我们将使读者更好地理解时钟抖动问题及其对高速ADC性能的影响。

2020-08-20 14:25:16 1408

1408

二元输出中的宽带噪声,称作量化噪声,它限制了一个ADC的动态范围。本文描述了两种时下最流行的方法来改善实际ADC应用中的量化噪声性能:过采样和高频抖动。

2020-08-24 10:04:06 6415

6415

高速ADC使用外部输入时钟对模拟输入信号进行采样,如图1所示。图中显示了输入采样时钟抖动示意图。 图1、ADC采样 输入模拟信号的频率越高,由于时钟抖动导致的采样信号幅度变化越大,这点在图2中显示的非常明显。输入信号频率为F2=100MHz时,采样幅度变化如图红色虚

2021-04-07 16:43:45 10607

10607

DN1013-了解时钟抖动对高速ADC的影响

2021-05-11 18:22:19 0

0 总结了在高速PCB板设计中信号完整性产生的原因、抑制和改善的方法。介绍了使用IBS模型的仿真步骤以及使用 CADENCE公司的 Allegro SPB软件,支持IBIS模型对反射和串扰的仿真,验证了其改善后的效果,可以直观地看到PCB设计是否满足设计要求,进而指导和验证高速PCB的设计。

2021-05-27 13:59:31 22

22 高速ADC测试和评估方法(开关电源技术与设计 第二版.pdf)-应用范围本应用笔记将介绍ADI公司高速转换器部门用来评估高速ADC的特征测试和生产测试方法。本应用笔记仅供参考,不能替代产品数据手册

2021-09-16 17:22:31 27

27 高速ADC、DAC测试原理及测试方法(通信电源技术2020年16期)-随着数字信号处理技术和数字电路工作速度的提高,以及对于系统灵敏度等要求的不断提高,对于高速、高精度的ADC、DAC的指标都提出

2021-09-16 17:29:30 53

53 blog高速ADC、DAC测试原理及测试方法(肇庆理士电源技术有限公司招聘)-随着数字信号处理技术和数字电路工作速度的提高,以及对于系统灵敏度等要求的不断提高,对于高速、高精度的ADC、DAC的指标

2021-09-17 09:17:28 32

32 AT84AD001型ADC在2GHz高速信号采集系统中的应用(无线电源技术商业计划书)-该文档为AT84AD001型ADC在2GHz高速信号采集系统中的应用讲解文档,是一份不错的参考资料,感兴趣的可以下载看看,,,,,,,,,,,

2021-09-24 16:39:25 5

5 本文结合实际测试中遇到的时钟信号回沟问题介绍了高速信号的概念,进一步阐述了高速信号与高频信号的区别,分析了25MHz时钟信号沿上的回沟等细节的测试准确度问题,并给出了高速信号测试时合理选择示波器的一些建议。

2022-09-14 09:20:17 5855

5855 本文件的目的是介绍与高速模数转换器(ADC)。本文件详细介绍了抽样理论,数据表规格、ADC选择标准和评估方法、时钟抖动等常见问题系统级问题。此外,一些最终用户希望扩展通过实现交织、平均或抖动技术实现ADC。的好处和关注点本文讨论了交织、平均和抖动ADC

2022-09-20 14:23:49 4

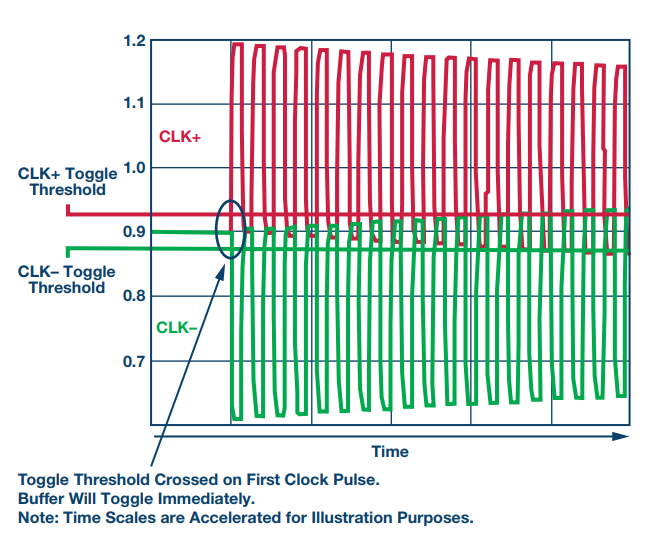

4 高速模数转换器(ADC)是定义上的器件 对模拟信号进行采样,因此必须具有采样时钟 输入。一些使用ADC的系统设计人员观察到速度较慢 比最初应用采样时钟时的预期启动时间长。 令人惊讶的是,这种延迟的原因往往是错误的启动 外部施加的ADC采样时钟的极性。

2023-01-05 11:07:59 2033

2033

在 DAQ 系统中,时钟作为时间参考,以便所有组件可以同步运行。对于模数转换器 (ADC),准确且稳定的时钟可确保主机向 ADC 发送命令,并且 ADC 以正确的顺序从主机接收命令且不会损坏。更重要的是,系统时钟信号使用户能够在需要时对输入进行采样并发送数据,从而使整个系统按预期运行。

2023-03-16 11:14:57 1958

1958

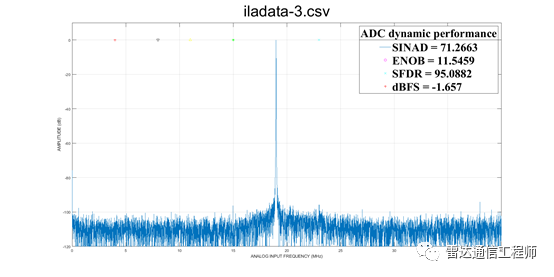

测试方法:高品质信号源输出单频信号经过带通滤波器后给到ADC,ADC为一颗14bit的多通道ADC,采集16k点的ADC数据做FFT分析各频谱分量。

2023-07-04 11:33:54 2472

2472

今天给大家分享下高速ADC噪声系数计算方法

2023-07-10 16:33:48 2531

2531

时钟信号怎么产生的 时钟信号是一种重要的信号,它在电子设备中广泛应用。时钟信号的产生与传输是现代电子设备中不可或缺的基础技术之一。时钟信号的精确性和准确性是现代电子设备能够实现高速计算等复杂操作

2023-09-15 16:28:22 3630

3630 电子发烧友网站提供《高速ADC的特征测试和生产测试方法评估笔记.pdf》资料免费下载

2023-11-27 10:28:42 9

9 本应用笔记将介绍ADI公司高速转换器部门用来评估高速ADC的特征测试和生产测试方法。本应用笔记仅供参考,不能替代产品数据手册。 动态测试硬件设置 SNR、SINAD、最差杂散和IMD均通过类似于图1的硬件设置进行测试。

2023-11-28 16:32:27 4

4 周期性的方波,每个周期都分为高电平(或1)和低电平(或0)两个状态。在每个周期的上升沿或下降沿,电路中的操作被触发执行。时钟信号的频率决定了电路的操作速率,也称为时钟频率。 产生时钟信号的方法取决于特定应用的要求

2024-01-25 15:40:52 15223

15223 高速PCB信号和电源完整性问题的建模方法研究

2024-09-21 14:13:25 1

1 通常把具备以下特征的信号视为高速信号: 频率大于50MHz的信号,特别是时钟信号频率达到50MHz以上的信号 上升沿时间短的快沿信号,当上升沿时间小于50ps时,信号变化速度极快,也可以被认定为高速信号 从走线长度角度,如果走线的长

2024-11-08 11:50:04 1616

1616 在使用高速模数转换器 (ADC) 进行设计时,需要考虑很多因素,其中 ADC 采样时钟的影响对于满足特定设计要求至关重要。关于 ADC 采样时钟,有几个指标需要了解,因为它们将直接影响 ADC

2024-11-13 09:49:18 2545

2545

在现代电子系统中,模数转换器(ADC)是将模拟信号转换为数字信号的关键组件。随着技术的发展,对ADC的需求也在不断变化。一方面,高速ADC能够快速处理信号,适用于需要快速响应的应用;另一方面,低功耗

2024-11-19 16:10:46 1846

1846 PCB设计电源去耦电容改善高速信号质量?!What?Why? How?

2025-05-19 14:27:18 619

619

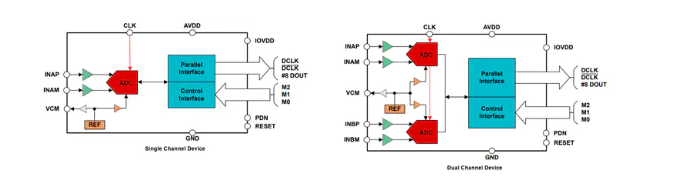

Texas Instruments ADC3908Dx/ADC3908Sx 8位高速模数转换器(ADC)是一系列超低功耗8位125MSPS高速双通道和单通道ADC。仅一个时钟周期的短延迟对高速控制环路有益。该ADC在125MSPS时的功耗仅为90mW,其功耗等级具有较低的采样率。

2025-07-17 11:50:39 682

682

电子发烧友App

电子发烧友App

评论