前言:本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容:

时钟抖动的构成

时钟抖动对ADC SNR的影响

如何计算时钟抖动

如何优化时钟抖动

1.采样理论

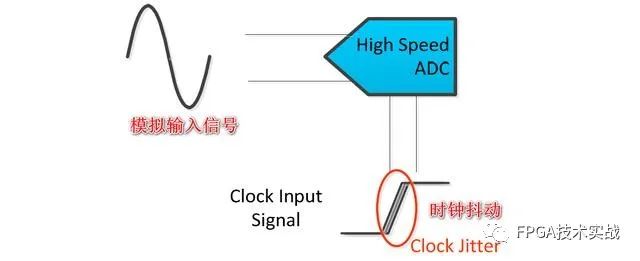

高速ADC使用外部输入时钟对模拟输入信号进行采样,如图1所示。图中显示了输入采样时钟抖动示意图。

图1、ADC采样

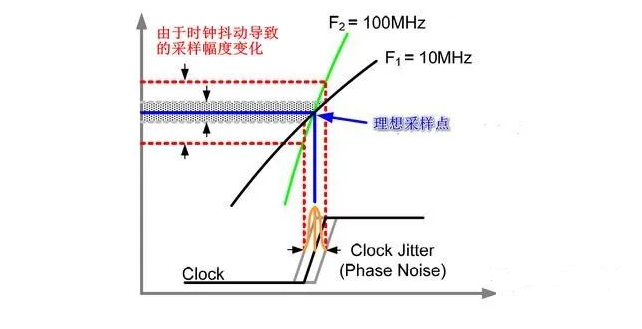

输入模拟信号的频率越高,由于时钟抖动导致的采样信号幅度变化越大,这点在图2中显示的非常明显。输入信号频率为F2=100MHz时,采样幅度变化如图红色虚线所示,明显大于输入信号F1=10MHz时采样幅度的变化。

图2、时钟抖动对不同频率输入模拟信号的影响

2.采样时钟抖动

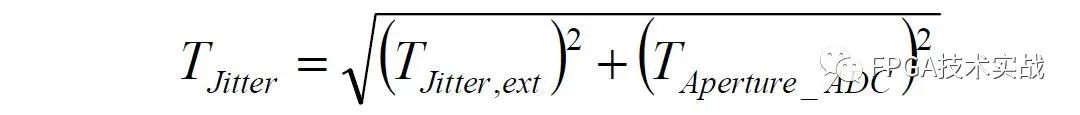

采样时钟抖动主要由两部分组成:

外部输入时钟抖动

ADC孔径抖动

图3、时钟抖计算公式

时钟沿速率越快,带来的时钟抖动越小,同时也会增加PCB设计难度。

图4、时钟抖动构成

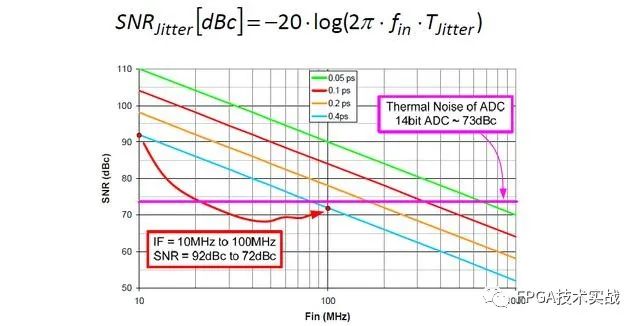

3.时钟抖动对SNR的影响

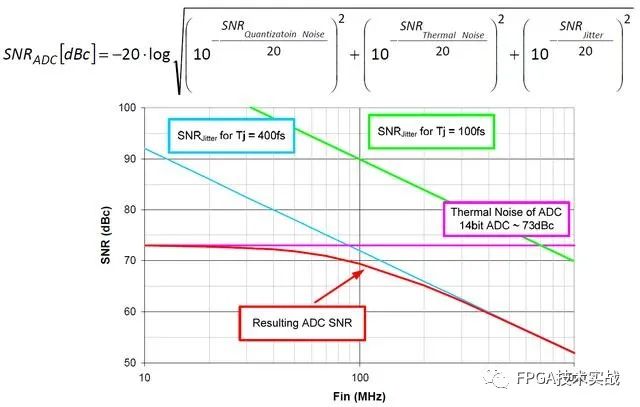

由于时钟抖动对ADC信噪比SNR的影响由图5所示公式计算。在图5中,可以看到时钟抖动对高频模拟输入信号影响更大。

图5、时钟抖动对SNR的影响

ADC噪声下限SNR一般由三部分构成:

ADC量化噪声

ADC热噪声

抖动衰减

图6、ADC噪声下限计算

4.计算抖动的幅度

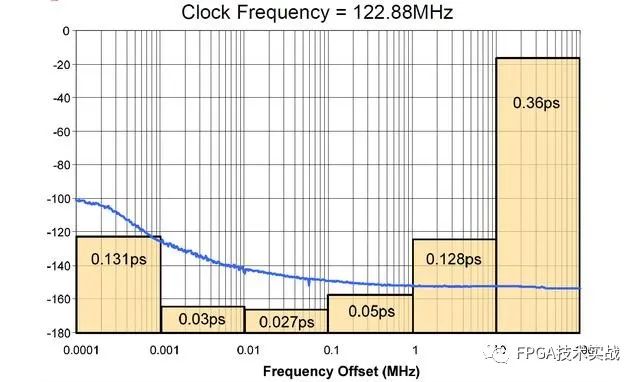

时钟抖动通过对时钟信号的相位噪声进行积分运算得到。典型的计算应用要求如图7所示。

图7、典型的时钟抖动计算要求

积分上限一般由以下因素限制:

时钟滤波器带宽

ADC时钟输入带宽

ADC采样速率

图8、时钟频率偏移对应的抖动值

5.SRN在频率的影响

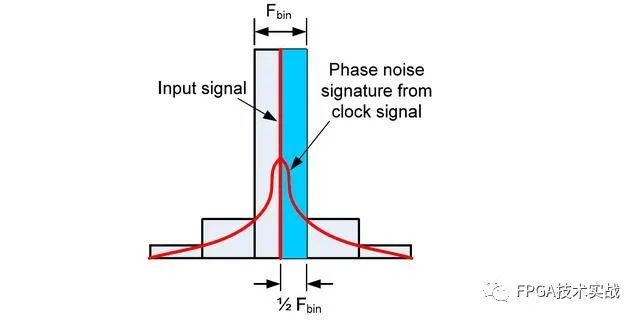

在采样过程中,时钟信号相位噪声被加到输入信号中。输入信号频率越高,相位噪声幅度越大,越大的相位噪声会导致越大的ADC噪声下限恶化,降低ADC有效分辨率。

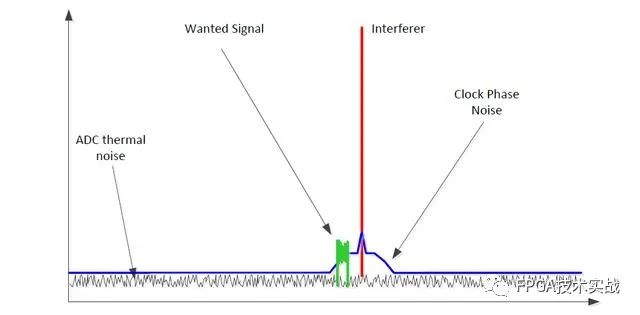

图9、相位噪声在频率的频谱图

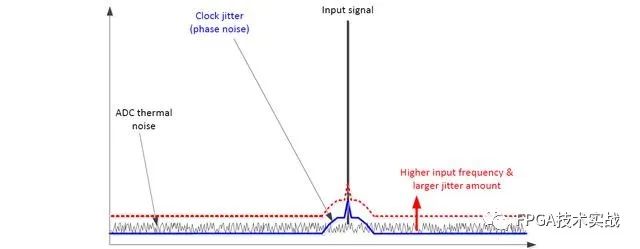

6.为什么时钟抖动/相位噪声如此关键

典型的接收机在“阻塞条件”下的性能包括两个方面:

一是,接收机需要在噪声背景下检测出想要的小信号

二是,在带内有大的干扰无法滤除,此干扰会影响小信号检测

图10、时钟抖动增强带内干扰影响

7.如何优化时钟抖动性能

为了使给定ADC的信噪比性能最大化,系统设计者可以采取几个步骤:

使用低抖动/相位噪声时钟源

使用低插入损耗的带通滤波器限制宽带噪声衰减

确保时钟振幅足够且不会降低ADC孔径抖动

编辑:jq

-

adc

+关注

关注

100文章

7946浏览量

556878 -

相位噪声

+关注

关注

2文章

198浏览量

23805 -

SNR

+关注

关注

3文章

198浏览量

25743

原文标题:正确理解采样时钟抖动(Jitter)对ADC信噪比SNR的影响

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AD9260:高速过采样CMOS ADC的卓越之选

MAX11284:双路24位低功耗高SNR 4ksps Delta-Sigma ADC的全方位解析

提高信噪比的操作

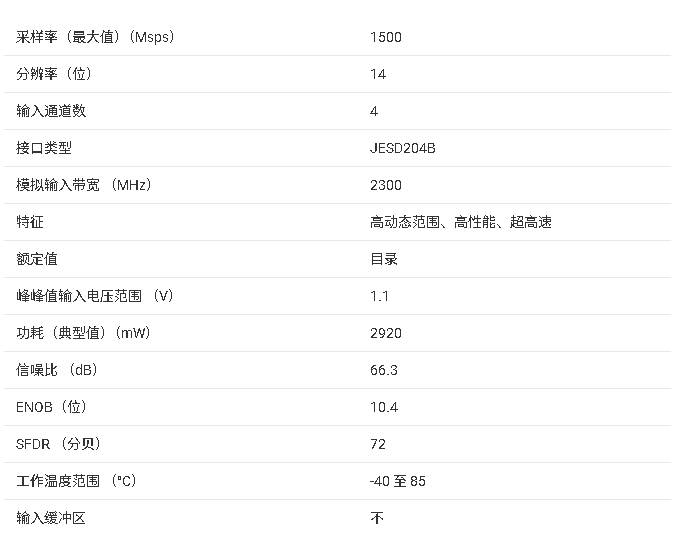

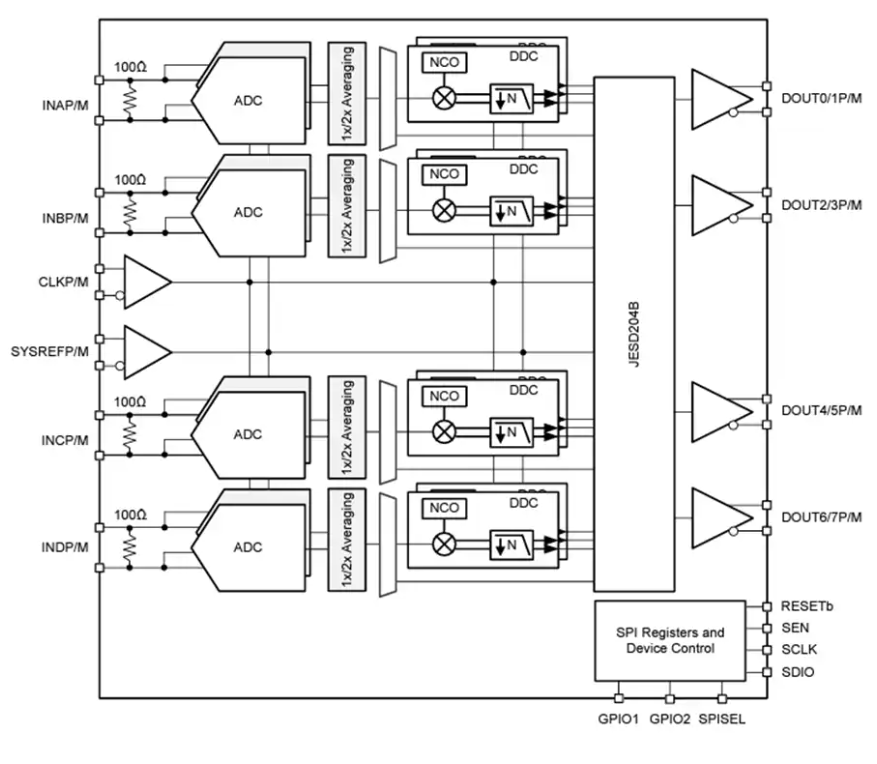

ADC34RF52 四通道 14 位 1.5GSPS 射频采样模数转换器(ADC)技术文档总结

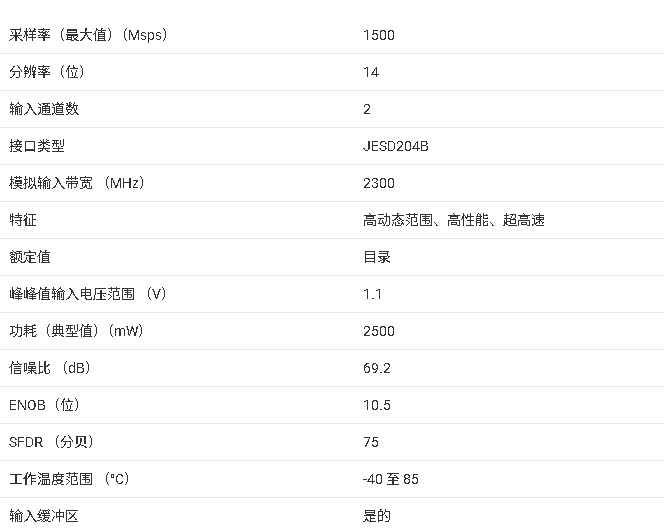

ADC32RF54双通道 14 位高速 RF 采样 ADC 技术总结

ADC32RF52 射频采样模数转换器技术总结

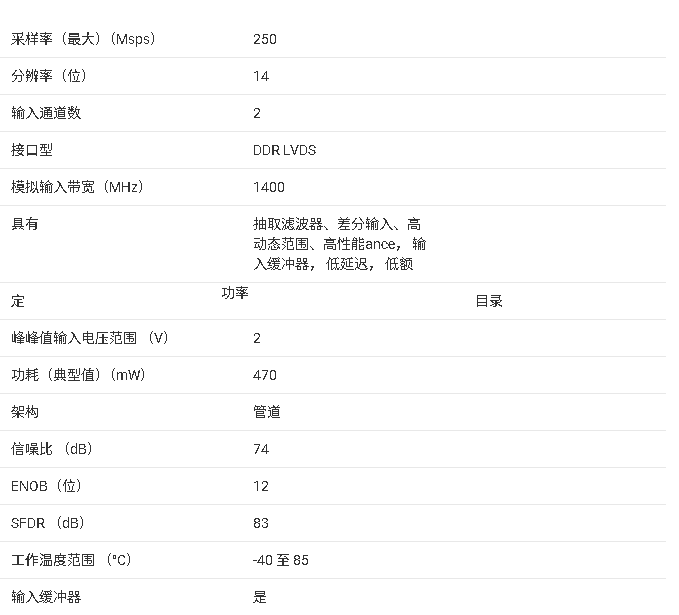

ADC3648/ADC3649 ADC 产品文档总结

ADC3568/ADC3569 ADC 产品文档总结

ADC3548/ADC3549 ADC 产品文档总结

德州仪器ADC34RF52:14位1.5GSPS射频采样ADC的技术解析

高性能射频采样ADC:ADC32RF5x系列技术解析

德州仪器ADC34RF55:14位3GSPS RF采样ADC技术解析

如何去正确理解采样时钟抖动(Jitter)对ADC信噪比SNR的影响

如何去正确理解采样时钟抖动(Jitter)对ADC信噪比SNR的影响

评论