高速先生成员--姜杰

大家都知道,信号的最佳回流路径是GND:对于走线而言,我们希望能参考GND平面;对于信号管脚,我们希望GND管脚伴随;对于BGA区域的高速信号扇出过孔,我们希望能被相邻的GND过孔包围。

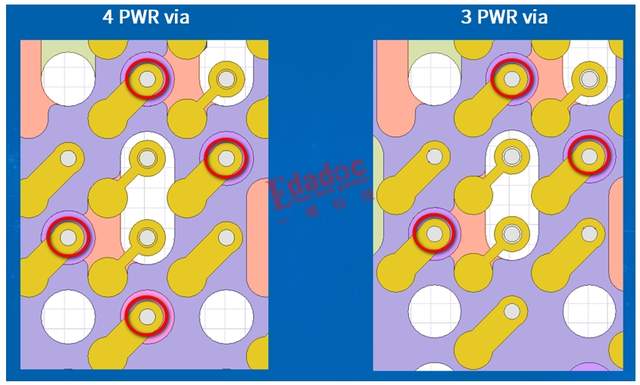

因此,经验丰富的攻城狮一定会避免让高速差分信号置于如下的境地:BGA区域差分信号管脚的四周分布多个电源管脚(图中白色对应差分信号,绿色是GND网络,黄色是电源PWR网络),不多不少,一边一个。

理想很丰满,现实却很骨感,上图的这种情况偏偏是存在的,更要命的是,电源管脚还不能换成GND网络。

当硬件攻城狮对换PIN方案表示无能为力的时候,Layout攻城狮把求助的眼光投向了高速先生,高速先生则默默的看向本文的标题:如何用电源去耦电容改善高速信号质量?

没错,高速先生做过类似的案例。

如前所述,我们的Layout攻城狮经验丰富,在他的努力下,找到了另外一个对比模型,信号管脚周围只分布了3个电源管脚(下图中的红色圆圈)的情况。

为了高速先生仿真对比,Layout攻城狮也是非常的贴心了。

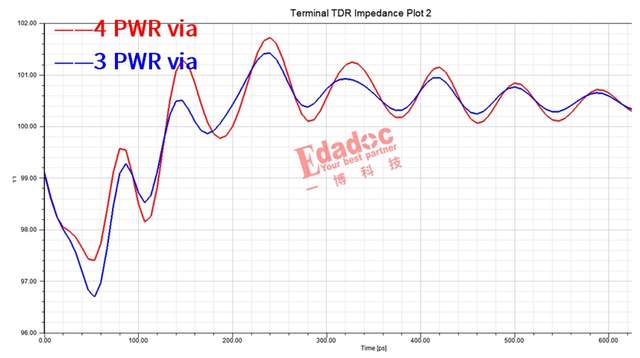

先仿真没有电容的情况。这个时候,对于走线特征阻抗100欧姆的差分信号,过孔阻抗是这样的:

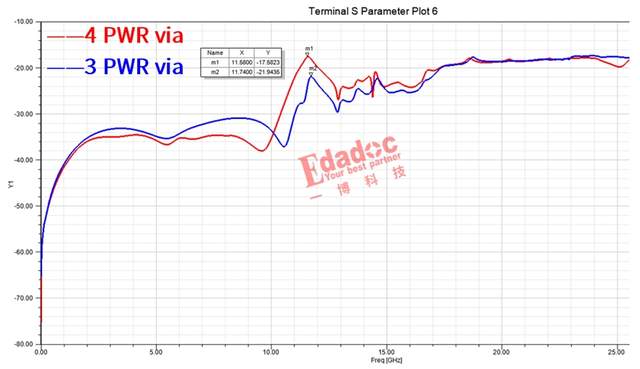

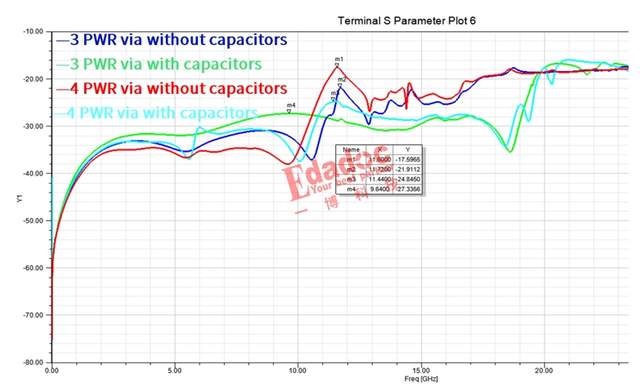

阻抗曲线甚至出现了振荡。换个角度,对比衡量阻抗连续性的另外一个参数,回波损耗。对于本案例中的100GBASE-KR4信号,在基频12.9GHz以内的频段,4个电源孔情况下的最大回损-17.5dB,3个电源孔情况下的最大回损-21.9dB。

通过对比可以发现,回流地孔的增加确实改善了差分过孔的阻抗,回损也反映了同样的趋势。问题在于,无论是3个电源孔还是4个电源孔,结果都不太理想。

一直关注高速先生的朋友,一定还记得前不久的一篇文章《瞧不起谁啊!“缝合电容”我怎么可能不知道》,此时会不会突发灵感:同样是电容,电源去耦电容该不会对改善高速信号质量有帮助吧?

试试看。

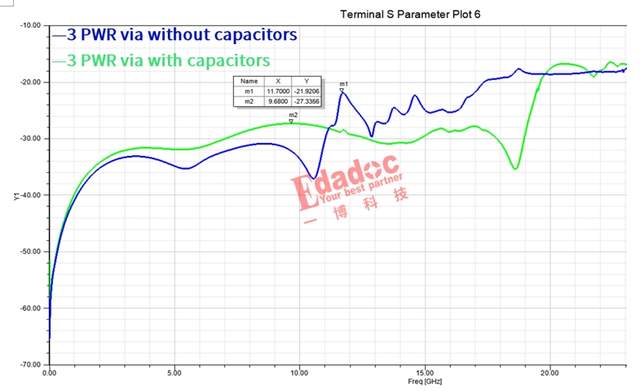

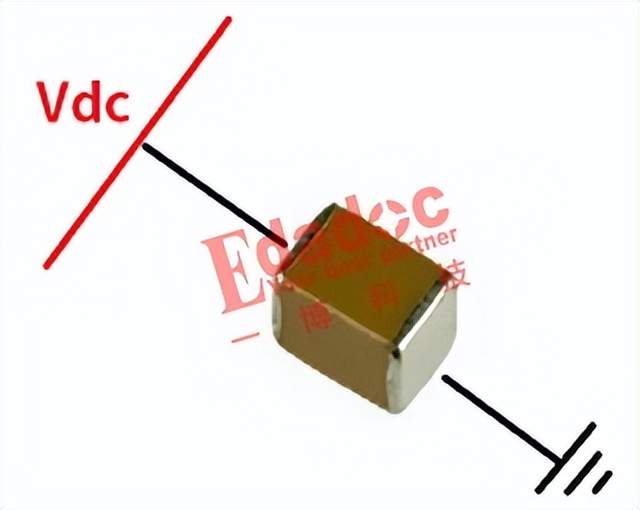

每个电源管脚加上本就属于它的去耦电容,像下图这样(当然了,BGA和电容位于PCB不同的布局面,本视图是为了大家更清楚的看到二者的相对位置)。

增加电容前后,3个电源过孔情况的回损对比如下,在关注频段内,增加电容后的最大回损有较大改善。

同样的, 4个相邻电源过孔的差分过孔回损也改善了不少。整体对比情况如下图。

电源去耦电容本来是为了减小电源噪声,没想到还能顺带改善信号质量,这到底是为什么呢?

问题来了

本案例中的电源去耦电容改善信号质量的原理是什么?

审核编辑 黄宇

-

仿真

+关注

关注

55文章

4535浏览量

138665 -

PCB设计

+关注

关注

396文章

4939浏览量

95780 -

去耦电容

+关注

关注

12文章

325浏览量

23615 -

GND

+关注

关注

2文章

550浏览量

41719

发布评论请先 登录

电源电容的作用

小尺寸车规贴片电容 车载 ADAS 模块电源去耦

PCB设计如何用电源去耦电容改善高速信号质量

PCB设计如何用电源去耦电容改善高速信号质量

评论