时钟信号怎么产生的

时钟信号是一种重要的信号,它在电子设备中广泛应用。时钟信号的产生与传输是现代电子设备中不可或缺的基础技术之一。时钟信号的精确性和准确性是现代电子设备能够实现高速计算等复杂操作的基础,因此,在电子学领域中,如何产生和控制时钟信号是一项至关重要的技术。

时钟信号是指一个周期性的方波信号,其周期性能和稳定性非常重要。为了使时钟信号精确可靠地产生,需要考虑多种因素的影响,包括设备的稳定性、抗干扰性、噪声等因素。下面将详细阐述时钟信号的产生过程。

时间基准

产生时钟信号的第一个关键因素是时间基准。时间基准是指用来产生时钟信号的稳定、可靠的参考时间源。时间基准可分为两类:外部时间基准和内部时间基准。

外部时间基准通常指由计算机外部提供的精确时间源。例如,广播台的标准无线电信号、GPS卫星传输的时间信号、太阳能钟等。这些时间基准都具有极高的稳定性和准确性,可以为时钟信号的产生提供高精度的参考。

内部时间基准指由计算机自身产生的时间源,如晶振、RC振荡器等。内部时间基准的精度往往要低于外部时间基准,但其优点在于可以减少电路的复杂性和成本。

晶振

晶振是一种常见的产生时钟信号的方法,它通过晶体振荡产生一定频率的电信号。晶振的工作原理是利用晶体的物理特性,当晶体受到外界电场刺激时会发生压电效应,从而产生短周期振荡。在晶振电路中,晶体通过一个电容与晶振电路相连,产生一个稳定可靠的振荡信号。晶振的频率精度和稳定性受到晶体品质、电路质量、温度等因素的影响。

RC振荡器

RC振荡器是另一种常见的时钟信号产生方法,它通过一个电容和电阻的组合来产生振荡信号。在RC振荡电路中,电容和电阻之间存在一定程度的耦合,从而产生振荡。RC振荡器的频率精度和稳定性取决于RC振荡电路中的电容和电阻的精度和温度等因素。

PLL锁相环

PLL锁相环是一种增强时钟信号精度和稳定性的技术。PLL锁相环利用反馈回路将时钟信号与内部振荡器的输出信号进行比较,并对比较结果进行反馈调整,从而使时钟信号的频率、相位和稳定性得到一定的提高。PLL锁相环的精度取决于反馈电路的质量和控制算法的准确性。

总之,时钟信号产生是现代电子学中非常重要的技术。不同的时钟信号产生技术在精度和稳定性等方面存在不同的优缺点。对于高精度、高性能的时钟信号要求,需要选择适合的产生技术,并配合合适的组合方式和控制算法,从而实现精确和稳定的时钟信号产生。

-

锁相环

+关注

关注

36文章

633浏览量

90801 -

时钟信号

+关注

关注

4文章

495浏览量

29692 -

PLL电路

+关注

关注

0文章

94浏览量

7022 -

rc振荡器

+关注

关注

3文章

49浏览量

9940

发布评论请先 登录

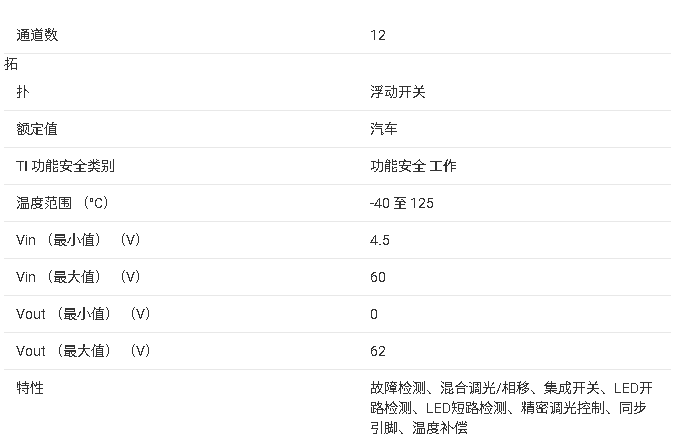

TPS92662A-Q1 高亮度LED矩阵管理器技术文档总结

精准时钟,驱动未来 ----澜起科技发布多款高性能时钟芯片

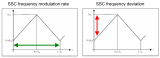

EMC 时钟信号的噪声源头是什么?

时钟信号怎么产生的

时钟信号怎么产生的

评论