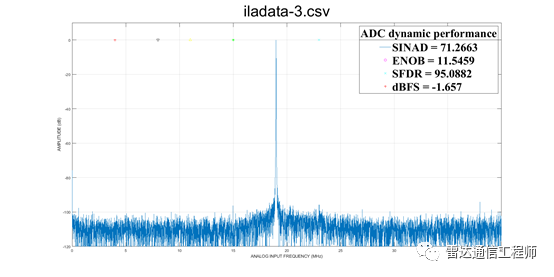

测试方法:高品质信号源输出单频信号经过带通滤波器后给到ADC,ADC为一颗14bit的多通道ADC,采集16k点的ADC数据做FFT分析各频谱分量。

Fs=80MHz采样61MHz单频

带通滤波器为两级级联,SINAD=71.26dB,有效位ENOB=11.55bit

Fs=80MHz采样141MHz单频

带通滤波器为单级,SINAD=68.05dB,有效位ENOB=11.0bit,与官方手册指标相差0.5bit有效位

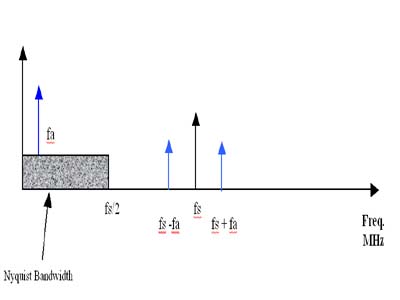

信号频率升高到141MHz时,信纳比(SINAD,)降低了3dB,并且出现了明显的杂散频点,最大杂散的频率为23MHz,通过分析可以发现该杂散为141MHz的三次谐波混叠而来,可通过改变测试频点来验证,频率提高1MHz到142MHz后该杂散转移到了26MHz,增加了3MHz,因此增加一级滤波器后应该会有所改善。142MHz时如下图所示:

信噪比SNR、信纳比SINAD的区别

信纳比(SINAD或S/(N + D))指的是信号幅度均方根与所有其它频谱成分(包括谐波但不含直流)的和方根(rss)的平均值之比。SINAD很好地反映了ADC的整体动态性能,因为它包括所有构成噪声和失真的成分。

信噪比(SNR,有时也称为无谐波的SNR)与SINAD一样,也是根据FFT数据计算,不同的是计算剔除了信号谐波,仅留下噪声项。实际应用中,只需剔除主要的前5次谐波。SNR性能在高输入频率下会下降,但由于不包括谐波项,其下降速度一般不像SINAD那样快。

-

FFT

+关注

关注

15文章

452浏览量

62620 -

信噪比

+关注

关注

3文章

267浏览量

29462 -

带通滤波器

+关注

关注

18文章

261浏览量

44496 -

SINAD

+关注

关注

0文章

5浏览量

10363 -

ADC采样

+关注

关注

0文章

134浏览量

13531

发布评论请先 登录

合理选择高速ADC实现欠采样

请问欠采样把中频处的信号搬移到基带进行处理是怎么实现的?

怎么测试高速ADC的性能?

使用国家半导体ADC演示高速ADC应用欠采样的作用与好处是什么?

欠采样超宽带LFM信号参数估计

欠采样中频收发器体系结构研究

使用国家半导体ADC演示高速ADC应用欠采样的作用与好处

实用模拟电路设计技术Section4高速采样ADC

单通道 / 双通道、14 位 250Msps ADC 系列提供高 SFDR 欠采样性能

高速ADC欠采样性能实测方法

高速ADC欠采样性能实测方法

评论