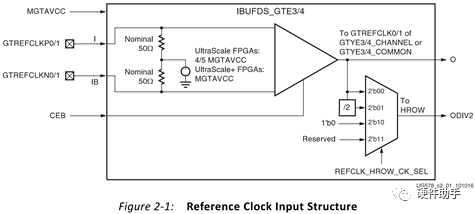

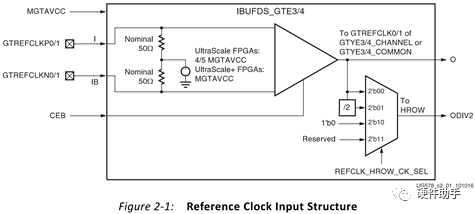

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。 参考时钟的模式 参考时钟可以配置为输入模式也可以是输出模式,但是在运行期间不能切换。作为

2020-11-14 11:39:15 17609

17609

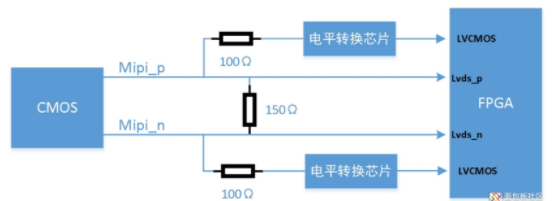

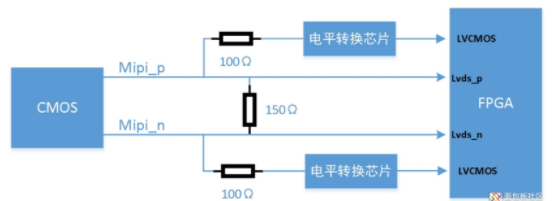

作者:Hello,Panda 这次分享一个在Xilinx FPGA实现MIPI DPHY接口的案例(包括CIS协议层)。截止目前为止,Xilinx仅在Ultrascale+及其以上版本的FPGA

2021-01-28 14:11:41 18343

18343

7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求。选择合适的时钟资源可以改善布线、性能和一般FPGA资源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 3922

3922 7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 2068

2068 Xilinx FPGA的组成部分 本文是以Xilinx Kintex UltraScale+ 系列为参考所写,其他系列有所不同,可以参考相应的user guide文档。 Xilinx家的FPGA有这

2022-12-27 15:54:52 3346

3346 锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 8964

8964

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 16812

16812

。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 1443

1443

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 4432

4432

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 5117

5117

FPGA 时钟分配网络设计技术

2012-08-20 17:15:27

今天给大侠带来 Xilinx ISE14.7 LVDS应用,话不多说,上货。

最近项目需要用到差分信号传输,于是看了一下FPGA上差分信号的使用。Xilinx FPGA中,主要通过原语实现差分信号

2024-06-13 16:28:52

是管脚的分配也必须在设计代码出来之前完成。所以,管脚的分配更多的将是依赖人,而非工具,这个时候就更需要考虑各方面的因素。 综合起来主要考虑以下的几个方面: 1 、 FPGA 所承载逻辑的信号流向。 IC

2012-08-11 10:27:54

=FLASE绕过PAR的检查,这样就只是将本该接入专用时钟管脚(或者叫做全局时钟管脚)的信号,接到了普通IO口上,但并没有做好如何用普通IO口来引入全局时钟,Xilinx官方论坛上更是有老外直接指出这只

2019-07-09 08:00:00

,FPGA上的全局时钟管脚用完了就出现不够用的情况。FPGA全局时钟约束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

摘要:FPGA异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的几种同步策略。关键词

2009-04-21 16:52:37

方面的要求。所以在管脚分配前对 FPGA工作的环境要相当的熟悉,要对其中的信号来自哪里去向何方非常的清楚,这就按照连线最短的原则将对应的信号分配到与外部器件连线最近的 BANK 中。2、 掌握

2024-01-10 22:40:14

的时钟都是差分时钟,这个时候如果所用的不是差分时钟就需要注意 P端与 N端一般不能同时分配给不同的时钟信号。如下图所示XILINX系列的FPGA中成对的时钟如果是同时采用那么就不能同时到达相同的区域,因为

2017-03-25 18:46:25

EDA技术具有什么特征?FPGA是什么原理?FPGA设计应用及优化策略基于VHDL的FPGA系统行为级设计

2021-04-15 06:33:58

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-05-28 09:23:25

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-07-08 08:00:00

`Xilinx FPGA入门连载12:PWM蜂鸣器驱动之引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 工程移植复制

2015-10-14 12:23:31

Xilinx FPGA配置clocking时钟动态相位输出

2019-08-05 11:35:39

个MUX。利用这种2+1的组合可以产生DDR操作,Xilinx称之为ODDR2。每个存储单元都有6个接口信号:时钟+时钟时能,数据输入+输出,置位复位+翻转输入除了这些信号,存储单元还有一些属性设置

2012-08-02 22:48:10

利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟 FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系

2012-03-05 14:42:09

您好Xilinx社区,我喜欢在时钟ADC和FPGA Spartan 6的通用时钟之间以90°的方式提供相位信号。之前,我的信号使用not功能进行180°定相。我的时钟信号只编码一位。请问你能帮帮我

2019-03-06 12:13:51

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说

2020-04-25 07:00:00

大家好,我刚开始学习FPGA并试图弄清楚哪些FPGA引脚可以分配我的数据信号。我正在使用FPGA Spartan 6封装TQG114器件LX9。查看产品规格,有102个可用的用户I / O.这是

2019-04-23 06:55:23

的时钟管脚,这样获得的时间的延迟将是最 小的,驱动也最强。复位信号因为要求同步性好驱动的能力强,所以一般的情况下也会从全局的时钟管脚送入。 在分配时钟时,根据时钟的多少分配的策略差别很大,也需要重点关注

2015-01-06 17:38:22

本帖最后由 mingzhezhang 于 2012-5-23 20:05 编辑

大型设计中FPGA的多时钟设计策略 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重

2012-05-23 19:59:34

最重要的一步是确定要用多少个不同的时钟,以及如何进行布线,本文将对这些设计策略深入阐述。 FPGA设计的第一步是决定需要什么样的时钟速率,设计中最快的时钟将确定FPGA必须能处理的时钟速率。最快时钟速率

2015-05-22 17:19:26

同步数字系统中的时钟信号(如远程通信中使用的)为系统中的数据传送定义了时间基准。一个时钟分配网络由多个时钟信号组成,由一个点将所有信号分配给需要时钟信号的所有组件。因为时钟信号执行关键的系统功能,很显然应给予更多的关注,不仅在时钟的特性(即偏移和抖动)方面,还有那些组成时钟分配网络的组件。

2019-10-16 07:11:33

并不理想。本文将讨论如何使用一个多点信号来分配PCIe时钟,而且仍满足PCIe第二代规范严格的抖动要求。

2019-09-26 07:56:41

在cache的相关操作中,cache控制器需要根据需求做出许多不同的选择。例如:分配策略是否需要将数据从主存中分配到cache中;替换策略组相联cache中,所有的way都已经有填充数据了,miss

2022-06-15 16:24:48

需要进行调整,在采用这一方法晨这些问题通常也已经局部化了,只需要在PCB或FPGA设计中进行很小的设计修改。

步骤1: 评估设计参数

那么,从哪里开始呢? 首先应当尽早制定I/O分配策略。 但没有优化

2024-07-22 00:40:11

已经检查过,我有正确的引脚从pcie插槽中点击100M refclk。我的问题 - 1)用于FPGA的xilinx gtx phy是否支持SSC时钟?2)如果我在主机端启用或取消了SSC时钟,那么我

2019-04-01 13:22:15

我做的一个基于DSP的系统中,DSP做主处理器,控制着整个系统,包括信号处理,整体调度等;选择了一块Xilinx的FPGA做FIFO UART和系统的逻辑控制和译码。DSP的时钟输入为15MHz

2023-06-19 06:43:17

问题是:如果相同的VCCO电压,不同的IO级标准信号可以在xilinx spartan6-45t FPGA的同一个BANK中一起分配?例如LVDS 3.3 V,TMDS 3.3 V

2019-10-23 10:03:17

简化Xilinx和Altera FPGA调试过程:通过FPGAViewTM 解决方案,如混合信号示波器(MSO)和逻辑分析仪,您可以在Xilinx 和Altera FPGA 内部迅速移动探点,而无需重新编译设计方案。能够把内部FPGA

2009-11-20 17:46:26 27

27 本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 摘要:介绍了为PET(正电子发射断层扫描仪)的前端电子学模块提供时间基准而设计的一种新型高频时钟扇出电路。该电路利用FPGA芯片来实现对高频时钟的分频

2009-06-20 12:41:04 1531

1531

大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 827

827

本文设计的基于Xilinx FPGA的千兆位以太网及E1信号的光纤传输系统采用Xilinx XC5VLX30T芯片,通过以太网测试仪和数据误码仪对本系

2010-07-06 09:09:10 3060

3060

本文将探讨FPGA时钟分配控制方面的挑战,协助开发团队改变他们的设计方法,并针对正在考虑如何通过缩小其时钟分配网络的规模来拥有更多的FPGA I/O,或提高时钟网络性能的设计者们

2011-03-30 17:16:32 1241

1241

FPGA 异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA 异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的

2011-12-20 17:08:35 63

63 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数

2012-05-21 11:26:10 1591

1591

如果您希望进一步了解本公司 FPGA 如何在丰富多样的应用中获得用武之地,建议查阅下列手册。 XAPP1065:Spartan-6 FPGA 扩频时钟生成 http :/ /www.xilinx.com/support/documentat ion/application_notes/xap

2012-08-14 17:24:13 95

95 DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 Xilinx FPGA设计进阶(提高篇)

有需要的下来看看

2015-12-29 15:45:48 12

12 Xilinx FPGA系列入门教程(一)——如何搭建Xilinx FPGA开发环境

2016-01-18 15:30:32 52

52 现在的FPGA向引脚分配信号的任务曾经很简单,现在也变得相当繁复。

2016-07-27 20:24:00 7371

7371 当Xilinx 7Series FPGA中,存在3种主要的时钟网络:BUFG,BUFR,BUFIO以及他们所衍生出的各种变种。那么他们有什么主要特点和区别呢? BUFIO是IO时钟网络,顾名思义,它

2017-02-08 05:31:40 3409

3409

谈到数字逻辑,谈到FPGA设计,每位工程师都离不开时钟。这里我们简单介绍一下xilinx 7 系列中的时钟资源。时钟设计的好坏,直接影响到布局布线时间、timing的收敛情况,FPGA的时钟

2017-02-08 05:33:31 1192

1192

1. Xilinx 时钟资源 xilinx 时钟资源分为两种:全局时钟和第二全局时钟。 1. 全局时钟资源 Xilinx 全局时钟采用全铜工艺实现,并设计了专用时钟缓冲与驱动结构,可以到达芯片内部

2017-02-09 08:43:41 2076

2076 上一篇写了基于Xilinx FPGA的通用信号发生器的案例,反响比较好,很多朋友和我探讨相关的技术,其中就涉及到信号的采集,为了使该文更有血有肉,我在写一篇基于Xilinx FPGA的通用信号采集器,望能形成呼应,以解答大家的疑问。

2017-02-11 03:11:37 2134

2134

设计过FPGA的原理图,看FPGA的手册,说管脚的分配问题,如时钟管脚要用GC类管脚,而且单端时钟输入时要用P类型的管脚,不能用N类型管脚等等。

2017-02-11 03:48:34 12613

12613

现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2017-05-18 10:51:54 31049

31049

FPGAs have changed dramatically since Xilinx first introduced them just 15 years ago. In the ast

2017-09-20 18:41:55 14

14 Xilinx FPGA的Maxim参考设计

2017-10-31 09:59:24 23

23 在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配

2017-11-22 07:09:36 12586

12586

Xilinx FPGA 可提供卓越的数字信号处理 (DSP) 性能,能够满足音频处理、接口、压缩、嵌入和转换等方面的需求。FPGA 架构所具有的内在并行性意味着音频的许多通道都可以使用极其高效的资源

2018-06-22 14:57:02 1319

1319 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟域

2018-09-01 08:29:21 6010

6010

FPGA本身是有专门的时钟cell的,以xilinx FPGA为例,就是primitive库中的BUFG。

2018-12-22 15:33:59 2174

2174 本文主要介绍Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 6756

6756 xilinx FPGA的资源一般指IOB,CLB,BRAM,DCM,DSP五种资源。其中IOB就是input/output block,完成不同电气特性下对输入输出信号的的驱动和匹配要求。

2020-12-29 16:59:33 12

12 全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

2020-12-29 16:59:35 8

8 利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线,本文将对这些设计策略深入阐述。

2021-01-13 17:00:00 11

11 本文档的主要内容详细介绍的是如何使用Xilinx的FPGA对高速PCB信号实现优化设计。

2021-01-13 17:00:59 26

26 利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线,本文将对这些设计策略深入阐述。

2021-01-15 15:57:00 14

14 引言:FPGA作为数字电路三大基石之一,其选型的好坏决定了产品的成本、项目研发效率、产品上市时间、产品生命周期等诸多方面。FPGA选型策略可以分为FPGA厂商选择、FPGA器件家族选择、器件型号选择

2021-03-22 09:25:18 7956

7956 引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。为了最好地利用时钟路由资源,必须了解如何从PCB到FPGA获取用户时钟,确定哪些时钟路由资源

2021-03-22 10:16:18 6115

6115

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 6070

6070 晶振是数字电路设计中非常重要的器件,时钟的相位噪声、频率稳定性等特性对产品性能影响很大。本文基于可编程晶振SI570,就Xilinx FPGA收发器输入参考时钟的硬件设计及FPGA软件设计给出设计案例,供大家参考。

2021-04-07 12:00:44 6246

6246

超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 AD5933 pmod Xilinx FPGA参考设计

2021-04-21 18:41:19 3

3 AD7780 pmod Xilinx FPGA参考设计

2021-04-22 13:35:23 15

15 AD5628 pmod Xilinx FPGA参考设计

2021-05-19 14:34:17 4

4 AD7193 pmod Xilinx FPGA参考设计

2021-05-19 15:18:13 2

2 AD7156 pmod Xilinx FPGA参考设计

2021-05-20 12:32:16 10

10 AD7991 pmod Xilinx FPGA参考设计

2021-05-20 12:37:26 12

12 AD5781 pmod Xilinx FPGA参考设计

2021-05-24 10:29:20 20

20 减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2021-09-23 16:39:54 3632

3632 说到异步时钟域的信号处理,想必是一个FPGA设计中很关键的技术,也是令很多工程师对FPGA望 而却步的原因。但是异步信号的处理真的有那么神秘吗?那么就让特权同学和你一起慢慢解开这些所谓的难点

2021-11-01 16:24:39 11

11 Xilinx FPGA开发实用教程资料包免费下载。

2022-04-18 09:43:46 29

29 HROW:水平时钟线,从水平方向贯穿每个时钟区域的中心区域,将时钟区域分成上下完全一致的两部分。全局时钟线进入每个时钟区域的逻辑资源时,必须经过水平时钟线。

2022-06-13 10:07:26 2543

2543 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 4699

4699 本章的主要内容: 分析时钟驱动器、时钟信号的特殊布线 改进时钟信号分配的特殊电路

2022-09-20 14:55:40 0

0 如何优化 PCIe 应用中的时钟分配

2022-11-07 08:07:15 0

0 现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2023-05-04 17:38:53 1487

1487 Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

0 基于FPGA的高频时钟的分频和分频设计

2023-08-16 11:42:47 1

1 减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2023-08-23 16:10:01 1372

1372 上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数

2023-09-07 18:31:35 3352

3352

,时钟是很重要的一个因素,而时钟配置芯片则是为了提供时钟信号而存在。 时钟是FPGA中非常重要的因素,因为FPGA必须在时钟边沿上完成一次操作。时钟信号决定了FPGA内部计算和通讯的速度,因此时钟信号的稳定性和精度至关重要。 FPGA实现时钟同步通常有两种方式:一种是通过外部时钟输入

2023-10-25 15:14:20 2400

2400 如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 3484

3484

FPGA输入的时钟信号必须是方波么?正弦波会有影响么? FPGA是一种可编程逻辑器件,通常用于实现数字电路。输入时钟信号是FPGA中非常重要的时序信号,对整个系统的稳定性和性能都有很大影响。在

2024-01-31 11:31:42 5410

5410 Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 5686

5686

电子发烧友App

电子发烧友App

评论