游戏开发者手中到普通消费者家中还需多久?商用化必须克服哪些瓶颈?以下是目前虚拟现实商用化路上的三大“拦路虎”。

2015-01-09 16:46:40 2024

2024 智能交通不但能提升运输效率,还能有效降低运输成本。业内人士认为,智能交通行业现在是一个快速增长的增量市场,未来发展空间广阔。但是智能交通在欣欣向荣之时,国内智能交通设备厂商就能高枕无忧吗?据悉,我国智能交通产业还面临四大拦路虎。

2015-07-23 09:56:45 2717

2717 1.亚稳态与设计可靠性设计数字电路时大家都知道同步是非常重要的,特别当要输入一个信号到一个同步电路中,但是该

2017-12-18 09:53:13 9651

9651

自研GPU遇拦路虎?Imagination再度与苹果签订新协议

2020-01-02 18:05:39 5987

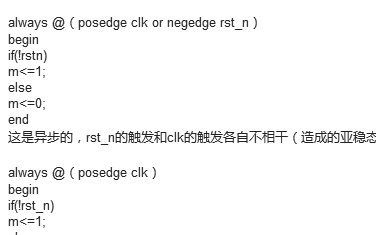

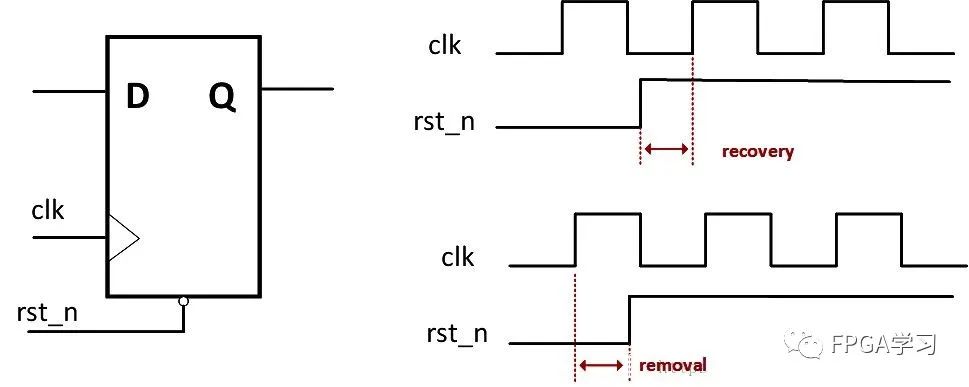

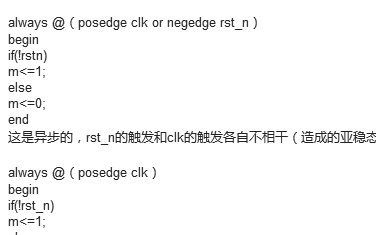

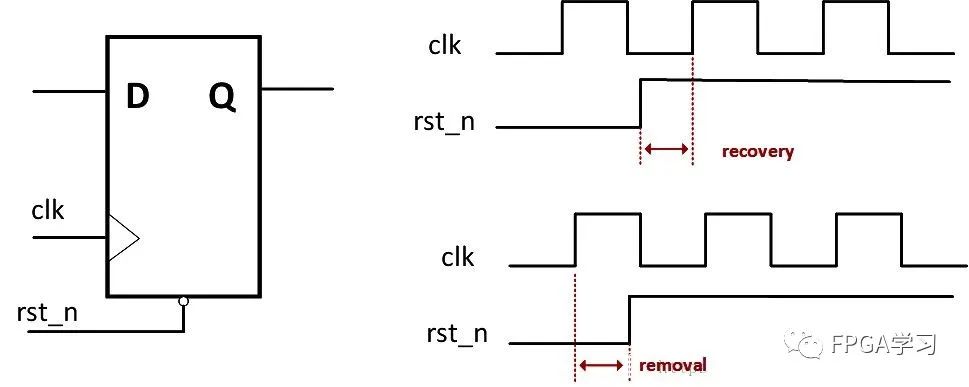

5987 在复位电路中,由于复位信号是异步的,因此,有些设计采用同步复位电路进行复位,并且绝大多数资料对于同步复位电路都认为不会发生亚稳态,其实不然,同步电路也会发生亚稳态,只是几率小于异步复位电路。

2020-06-26 16:37:00 1776

1776

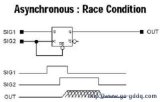

只要系统中有异步元件,亚稳态就是无法避免的,亚稳态主要发生在异步信号检测、跨时钟域信号传输以及复位电路等常用设计中。

2020-09-30 17:08:43 4345

4345

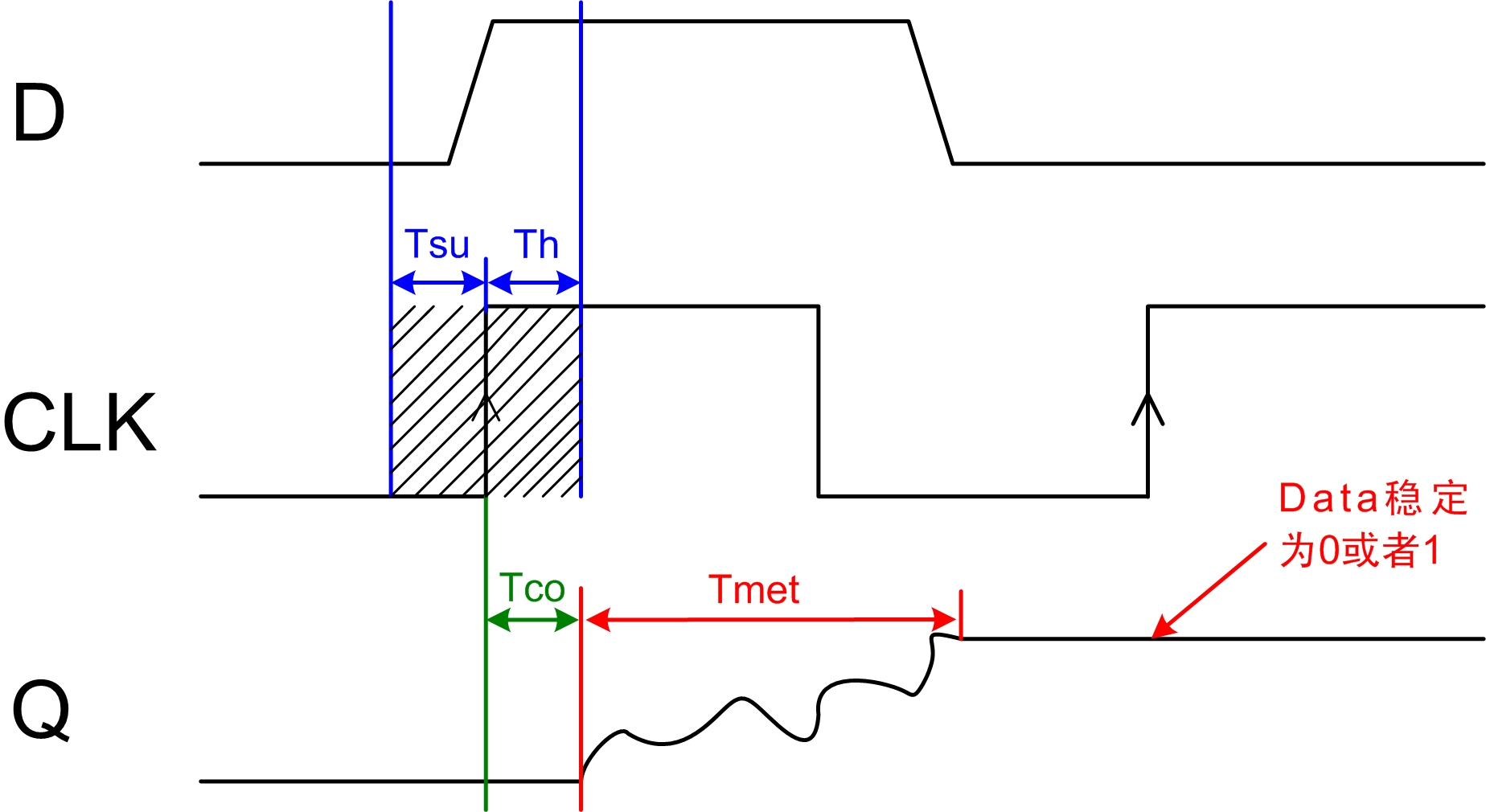

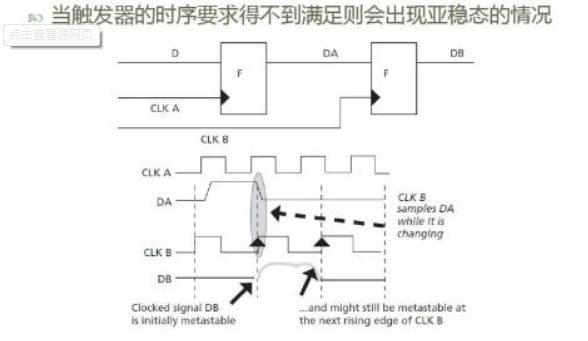

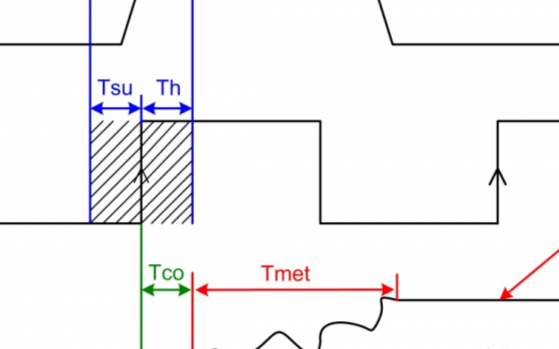

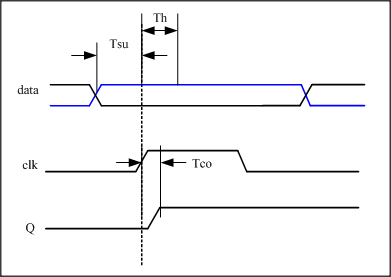

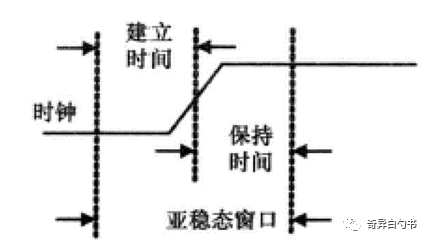

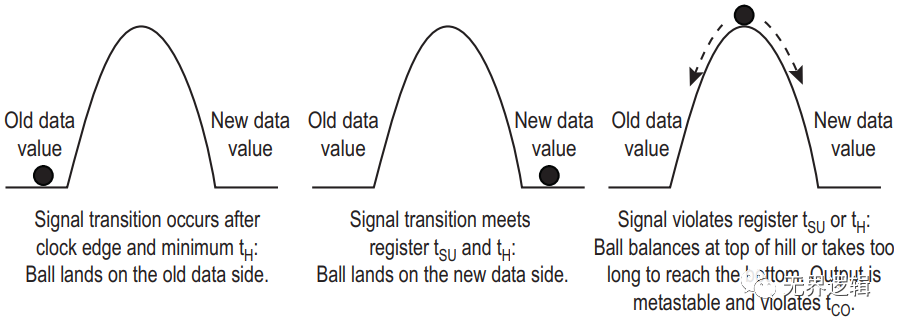

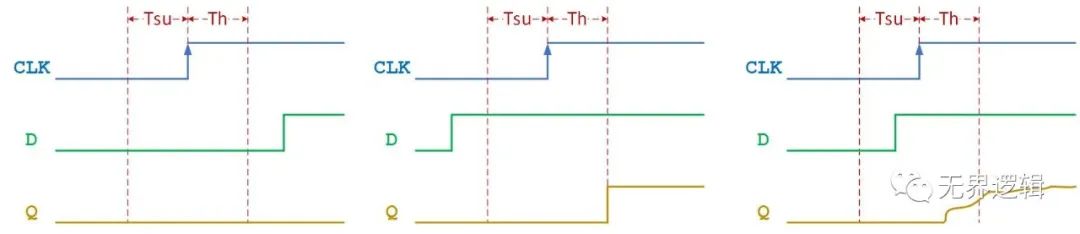

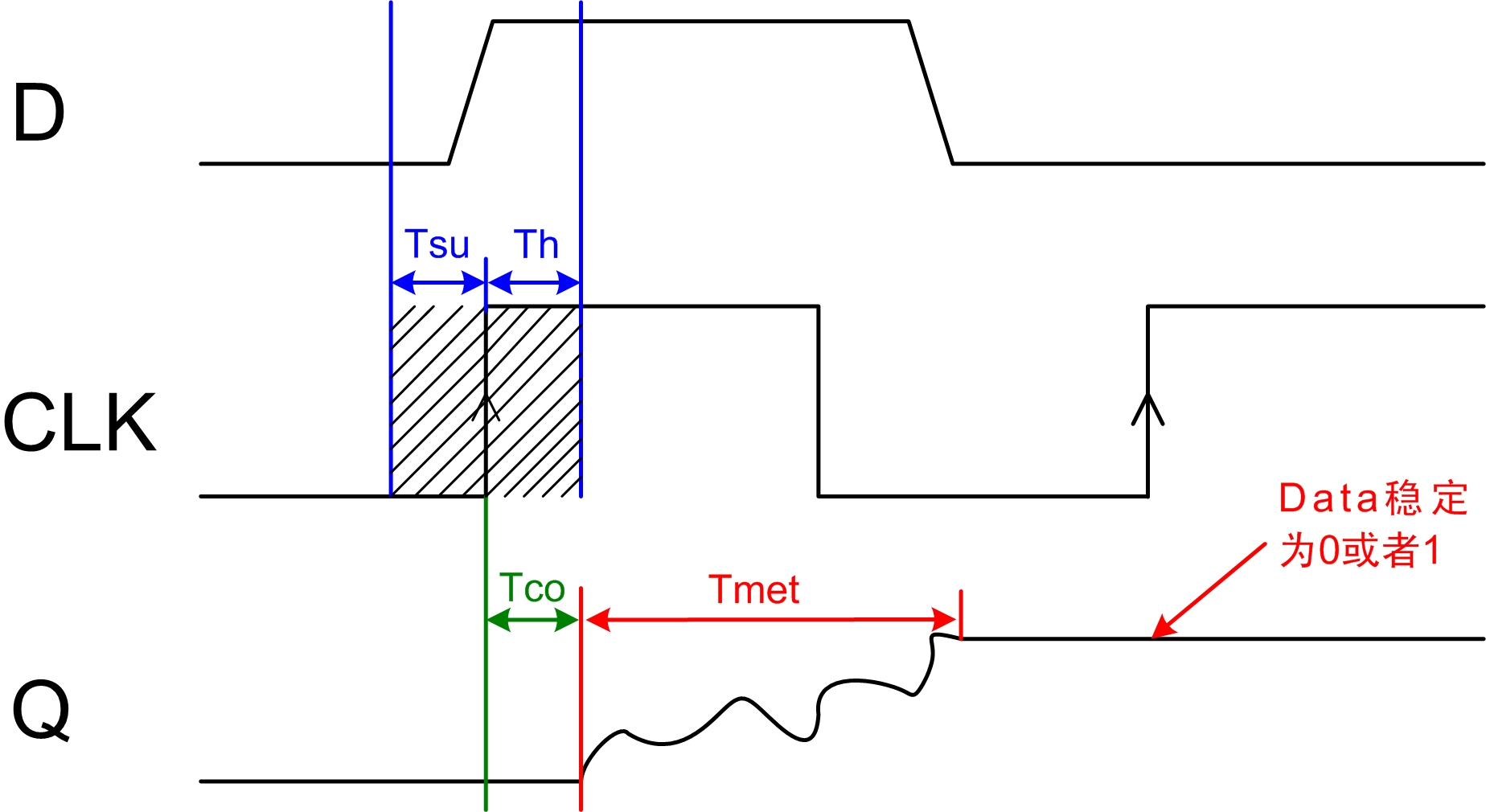

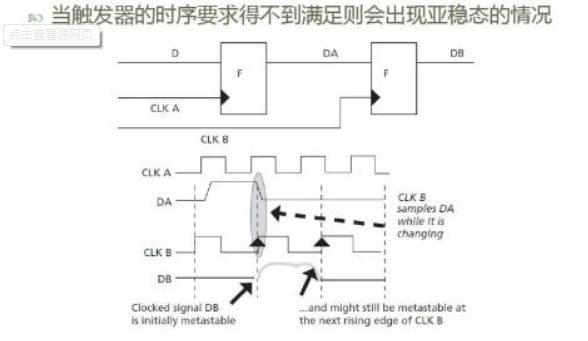

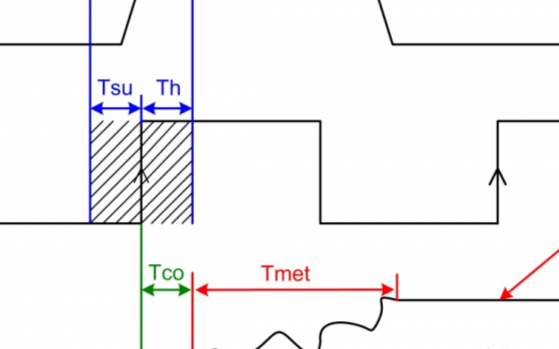

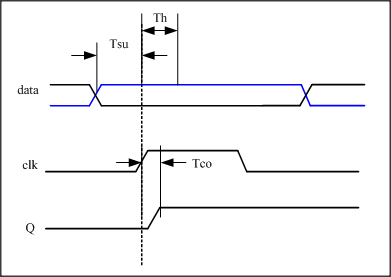

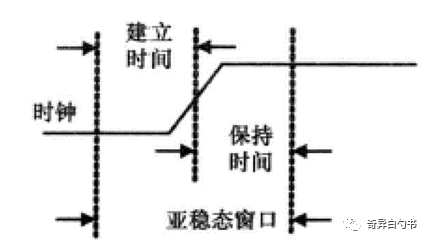

发生亚稳态的原因是信号在传输的过程中不能满足触发器的建立时间和保持时间。

2023-06-20 15:29:58 2210

2210

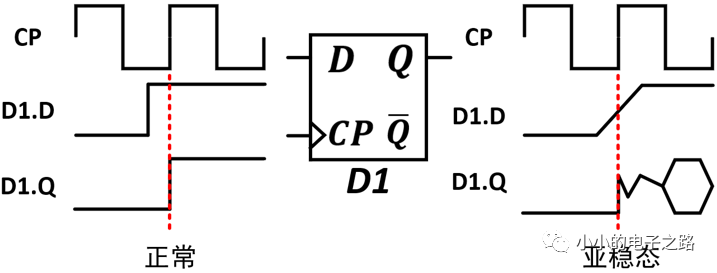

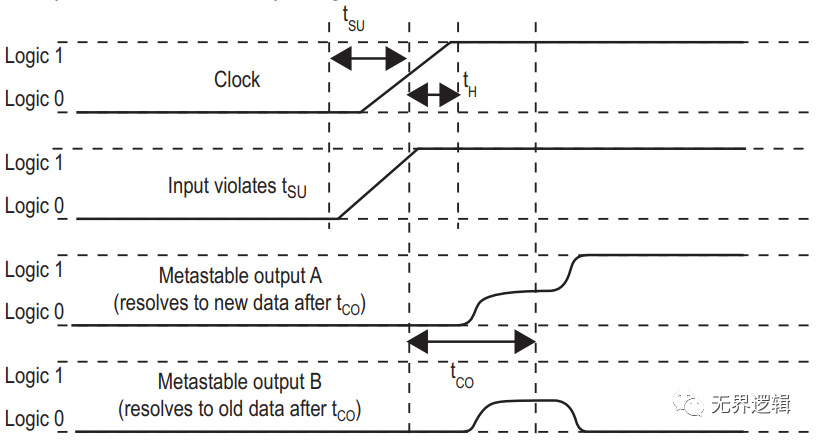

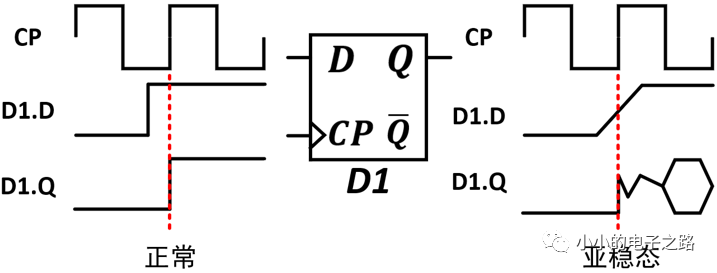

亚稳态是指触发器的输入信号无法在规定时间内达到一个确定的状态,导致输出振荡,最终会在某个不确定的时间产生不确定的输出,可能是0,也可能是1,导致输出结果不可靠。

2023-11-22 18:26:09 2725

2725

在嵌入式学习过程中,基于ARM核的嵌入式芯片必不可少。那么,在学习ARM嵌入式知识或开发中,嵌入式工程师会遇到哪些不可预知的问题?哪些问题会在嵌入式的学习中成为您的拦路虎?为了尽量为电子发烧友网读者扫清这些令人困惑的障碍,故电子发烧友网整理推出《ARM嵌入式学习经典40问》,以飨读者。

2020-08-10 10:30:00

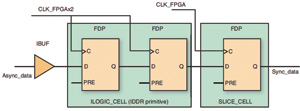

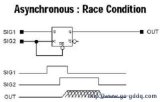

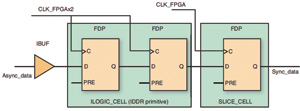

FPGA 设计需要重视的一个注意事项。理论分析01 信号传输中的亚稳态在同步系统中,输入信号总是系统时钟同步,能够达到寄存器的时序要求,所以亚稳态不会发生。亚稳态问题通常发生在一些跨时钟域信号传输以及异步

2020-10-22 11:42:16

导致复位失败。怎么降低亚稳态发生的概率成了FPGA设计需要重视的一个注意事项。2. 理论分析2.1信号传输中的亚稳态在同步系统中,输入信号总是系统时钟同步,能够达到寄存器的时序要求,所以亚稳态不会

2012-04-25 15:29:59

部件将其作出不同的判断,有的判断到“1”有的判断到“0”,有的也进入了亚稳态,数字部件就会逻辑混乱。在复位电路中产生亚稳态可能会导致复位失败。怎么降低亚稳态发生的概率成了FPGA设计需要重视的一个

2012-01-11 11:49:18

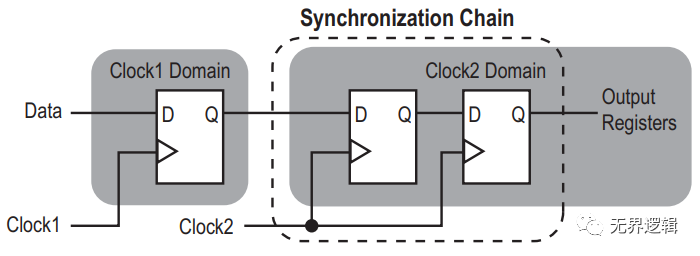

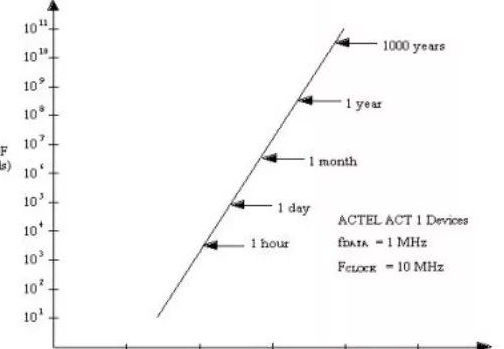

摘要:FPGA异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的几种同步策略。关键词

2009-04-21 16:52:37

说起亚稳态,首先我们先来了解一下什么叫做亚稳态。亚稳态现象:信号在无关信号或者异步时钟域之间传输时导致数字器件失效的一种现象。

2019-09-11 11:52:32

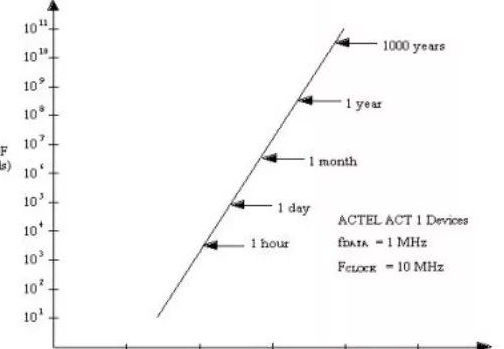

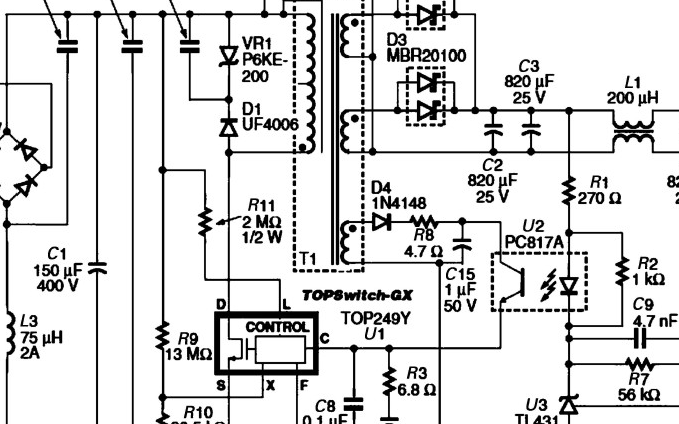

返回到低电平, 这和输入的数据无关。且在亚稳态的过程中,触发器的输出可能在震荡,也可能徘徊在一个固定的中间电平上。我们来看一个真实案例。见图3. 在这个案例中,我们测试一个FPGA逻辑单元中的亚稳态现象。在测试中,我们让sel信号固定在0,那么逻辑关系为 F1

2012-12-04 13:51:18

FPGA项目开发之同步信号和亚稳态

让我们从触发器开始,所有触发器都有一个围绕活动时钟沿的建立(setup time)和保持窗口(hold time),在此期间数据不得更改。如果该窗口中的数据

2023-11-03 10:36:15

麻雀虽小,五脏俱全。CPLD规模虽小,其原理和设计方法和FPGA确是一样的。轻视在CPLD上的投入,就有可能存在设计隐患,导致客户使用产品时出现故障,从而给公司带来不可挽回的信誉损失。近一段时间,我

2012-12-04 13:55:50

亚稳态是数字电路设计中最为基础和核心的理论。同步系统设计中的多项技术,如synthesis,CTS,STA等都是为了避免同步系统产生亚稳态。异步系统中,更容易产生亚稳态,因此需要对异步系统进行特殊的设计处理。学习SoC芯片设计,欢迎加入启芯QQ群:275855756

2013-11-01 17:45:15

中找到任何最小数量的寄存器的建议。我需要有关同步器链长度的任何建议或任何文档,以便针对Virtex-5器件提供更好的亚稳态保护。我还需要Virtex-6的类似信息。很抱歉,如果这不是此主题的正确论坛。提前致谢,阿姆鲁

2020-06-12 09:27:03

的亚稳态事件,结合实例讲解,语言通俗易懂,由浅入深,特别举了多个实例以及解决方案,非常具有针对性,让人受益匪浅,非常适合对亚稳态方面掌握不好的中国工程师和中国的学生朋友,是关于亚稳态方面不可多得的好资料,强烈推荐哦!!![hide] [/hide]`

2012-03-05 14:11:41

通过独立按键控制LED灯状态变化这样一个实验,来验证独立按键消抖是否成功,另外,由于独立按键作为一个外部异步输入信号,因此借此机会刚好给大家详细介绍了亚稳态的原理和应对策略。希望大家在观看学习时,重点

2015-09-29 14:27:58

的稳定性。减少亚稳态的产生。

通过上述对亚稳态的分析以及各种模式的处理,相信各位大侠应该有所收获,今日说\"法\"到此结束,下篇再见,欢迎各位大侠投稿,交流学习,共同进步,祝一切安好!

2023-04-27 17:31:36

数据表或应用说明中定义。一般来说,当我们设计 FPGA 满足时序约束时,我们不必过于担心它们,因为 Vivado 会尽量满足约束中定义的性能。然而,当我们有异步信号进入到 FPGA 或多个彼此异步

2022-10-18 14:29:13

问题的,不过还是有一些方法可降低系统出现亚稳态问题的几率。先来深入研究一下引起亚稳态的原因,再谈谈用哪些方法加以应对。什么是亚稳态 在FPGA等同步逻辑数字器件中,所有器件的寄存器单元都需要预定义信号时序

2010-12-29 15:17:55

却是拦路虎,还有那些英文水平差的人,电子技术水平较低的人,很是打击学习的积极性。哪位大佬能把gpio.h加上中文注释,在函数中怎么用的,配套的电路图等,让初学者少走些弯路。

2023-10-26 09:47:06

性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。在FPGA中,同步信号、异步信号和亚稳态的理解PGA(Field-Programmable Gate Array),即现场

2023-02-28 16:38:14

。怎么降低亚稳态发生的概率成了 FPGA 设计需要重视的一个注意事项。理论分析01 信号传输中的亚稳态在同步系统中,输入信号总是系统时钟同步,能够达到寄存器的时序要求,所以亚稳态不会发生。亚稳态问题通常发生

2020-10-19 10:03:17

/Metastable-Delay-in-Virtex-FPGAs/ba-p/7996有Virtex4和Virtex5的测量。我正在寻找Virtex6和7Series部件的类似亚稳态参数测量。是否存在应用说明?我猜猜V6& 7应该比

2020-07-18 16:58:50

关于win10驱动安装失败的解决现在win10的驱动安装是学习单片机的路上一大拦路虎,故本人找到了解决win10成功安装驱动的方法最有效的方法按win+r然后输入service.msc找到Device Install Service 然后将其启动,再安装驱动,成功安装...

2022-02-16 07:10:12

在使用负载开关时 时序决定一切

2021-03-02 07:38:18

检测开关是人工智能的最大拦路虎。因此我们我们可以进行双开关设计。

当一个开关损坏就报错。要双开关到位才工作。这样就避免因为开关误报的情况。

2023-05-22 14:18:50

在开发DM8148+nvp6124驱动中遇到拦路虎,希望找个这方面的大神帮忙解决,如能帮解决问题,我们会付一笔辛苦费给您,有兴趣的可以加我QQ***,谢谢。

2017-12-19 20:43:45

求基于FPGA的交通灯控制的一切资料,有实物图更好,求大神

2015-11-01 16:59:34

亚稳态现象发生的概率(只能降低,不能消除),这在FPGA设计(尤其是大工程中)是非常重要的。亚稳态的产生:所有的器件都定义了一个信号时序要求,只有满足了这个要求,才能够正常的在输入端获取数据,在输出端

2018-08-01 09:50:52

该如何解决频率混叠和频谱泄露这两头谐波测量的“拦路虎”呢?

2021-04-29 06:59:42

模拟领域——一切皆有可能

我时常会被不懂技术的朋友或家人问到这样的问题:“这些被叫做芯片(IC)的到底是什么东西?”以及“它们是如何工作的?”。我尽所能地给

2008-09-22 08:48:51 869

869 笔记本选购要注意:主板决定一切!

很多读者在购买笔记本电脑时,更多关注于CPU、内存、显存、硬盘的大小,甚至连电池、配件等都一一烂熟

2010-01-23 14:10:41 6619

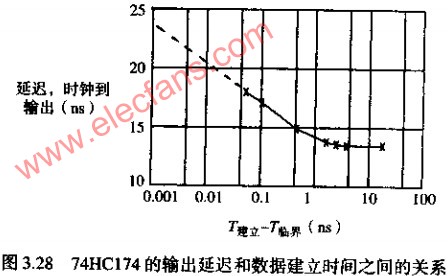

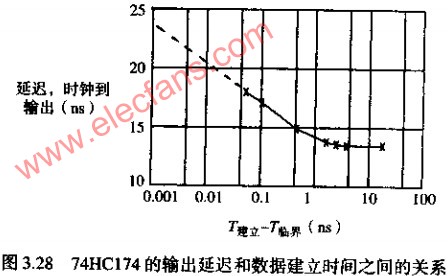

6619 图3.27所示的是一个观察D触发器亚稳态的电路图。使用这个电路至少需要一个双通道示波器。

2010-06-08 14:31:27 1490

1490

什么是亚稳态

在FPGA等同步逻辑数字器件中,所有器件的寄存器单元都需要预定义信号时序以使器件正确

2010-11-29 09:18:34 3518

3518

在本文的第一章对跨时钟域下的同步问题和亚稳态问题做了概述。 在第二章中对时钟同步需要考虑的基本问题做了介绍。 在第三章中仔细分析了现在常用的几种同步方法。包括使用G

2011-09-06 15:24:12 42

42 本文分析了异步电路中亚稳态产生的原因和危害, 比较了几种常用的降低亚稳态发生概率的设计方法, 针对这些方法不能彻底消除亚稳态的不足, 设计了一种消除亚稳态的外部逻辑控制器

2011-10-01 01:56:02 55

55 FPGA 异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA 异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的

2011-12-20 17:08:35 63

63 异步FIFO结构及FPGA设计,解决亚稳态的问题

2015-11-10 15:21:37 4

4 基于FPGA的亚稳态参数测量方法_田毅

2017-01-07 21:28:58 0

0 一切从游戏开始_python

2017-03-19 11:23:20 7

7 在进行FPGA设计时,往往只关心“0”和“1”两种状态。然而在工程实践中,除了“0”、“1”外还有其他状态,亚稳态就是其中之一。亚稳态是指触发器或锁存器无法在某个规定时间段内达到一个可确认的状态[1]。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。

2019-10-06 09:42:00 1760

1760

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平.

2017-12-02 10:40:12 45616

45616

通常情况下(已知复位信号与时钟的关系),最大的缺点在于异步复位导致设计变成了异步时序电路,如果复位信号出现毛刺,将会导致触发器的误动作,影响设计的稳定性。同时,如果复位信号与时钟关系不确定,将会导致 亚稳态 情况的出现。

2018-03-15 16:12:00 4610

4610

无论是数码3C锂电池时代,还是规模化生产的动力电池爆发年,模切工艺中的毛刺粉尘问题一直都被模切设备企业和电池企业公认为电芯生产中的一只拦路虎。

2018-05-18 16:43:16 6153

6153 大家好,又到了每日学习的时间了,今天我们来聊一聊FPGA学习中,亚稳态现象。 说起亚稳态,首先我们先来了解一下什么叫做亚稳态。亚稳态现象:信号在无关信号或者异步时钟域之间传输时导致数字器件失效的一

2018-06-22 14:49:49 3927

3927

在FPGA系统中,如果数据传输中不满足触发器的Tsu和Th不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器输出端Q在有

2018-06-27 10:11:00 11080

11080

本文采用问答形式向你详细地介绍了方方面面,不夸口的说,你所需要知道的关于 ZigBee的一切,在这里基本可以了解到!

2018-08-22 17:14:31 5978

5978 亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。

2018-09-22 08:25:00 10011

10011

在异步设计中,完全避免亚稳态是不可能的。因此,设计的基本思路应该是:首先尽可能减少出现亚稳态的可能性,其次是尽可能减少出现亚稳态并给系统带来危害的可能性。

2019-11-18 07:07:00 1972

1972 NSA组网确实可以经济实惠地建设5G,但并不意味着选择5G NSA组网就没有“拦路虎”。

2019-07-10 15:22:50 2407

2407 小区内如果仅有一家运营商的宽带,那么该小区必定存在垄断经营问题;如果小区内不同运营商的通信信号强弱不一,那么该小区大概率存在收取高额入场费的问题。未来5G基站需要大规模进入居民小区,物业公司这道门槛如果不尽早铲除,必将成为争抢5G全球领先赛道上的拦路虎。

2020-06-29 08:47:18 4744

4744 ,主板接口却还是老样子,成了新电源标准的拦路虎。这是怎么回事呢?小编今天就来聊聊这事儿吧。 至于主板迟迟不变的原因,其实很简单,因为跟主板伸手要电的配件太多了,电压也各不相同。如果供电电压换了,主板上的相关供电电路都得重新

2020-08-20 16:03:36 3178

3178 中国正在加快推进5G网络建设的进程,然而近期三大运营商均表示将在特定时段关闭5G基站,原因是5G基站耗电量太大,导致运营成本激增,不得不采取如此举措来控制成本,这说明能耗问题正成为5G普及的拦路虎。

2020-09-01 10:54:36 748

748 物联网的影响是将过去分散的、无法自我表达的一切事物注入灵魂,放到一个互联的网络进行交流、分析并产生更大的价值,其最终的落脚点是让人们享受更加舒适便捷的生活。隐私会死亡,世界更开放,财富将共享,个人更

2020-11-07 11:28:14 867

867 硅可以通过硅的高压金属相-Sn 结构的Si-II在卸压过程中发生相变而获得,其转变机理和相变路径受温度、压强、加载速率、剪切应力、样品尺寸等多种因素影响。然而,这些热力学物理因素是如何耦合在一起影响到亚稳态硅的合成的

2020-10-17 10:25:26 4038

4038 本文是一篇详细介绍ISSCC2020会议上一篇有关亚稳态解决方案的文章,该技术也使得FPGA在较高频率下的时序收敛成为了可能。亚稳态问题是芯片设计和FPGA设计中常见的问题,随着FPGA的发展,时序

2020-10-22 18:00:22 5277

5277

亚稳态概述 01亚稳态发生原因 在 FPGA 系统中,如果数据传输中不满足触发器的 Tsu 和 Th 不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time

2020-10-25 09:50:53 3120

3120

又遇“拦路虎。 随着AI、大数据、物联网和安防技术的融会贯通,要实现身份认证与识别,不单单只有人脸识别这一个突破口,指纹识别、虹膜识别、步态识别、静脉识别等技术也在不断突破创新中。那么,若人脸识别被按下“暂停键

2020-12-25 14:01:44 2735

2735 芯片紧缺,正在影响一切硬件,大到汽车,小到产线上的每一个充电器、蓝牙耳机。

2020-12-29 14:22:30 5193

5193 在同步系统中,如果触发器的setup time / hold time不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端毛刺、振荡、固定的某一电压值,而不是等于数据输入端D的值。

2021-03-09 10:49:23 2037

2037

电子发烧友网为你提供在使用负载开关时 时序决定一切资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-07 08:51:23 9

9 电子发烧友网为你提供什么是亚稳态资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-16 08:43:07 24

24 今天写一下时序问题常见的跨时钟域的亚稳态问题。 先说明一下亚稳态问题: D触发器有个明显的特征就是建立时间(setup time)和保持时间(hold time) 如果输入信号在建立时间和保持时间

2021-06-18 15:28:22 3606

3606 输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。 FPGA纯工程师社群 亚稳态产生原因 在同步系统中,触发器的建立/保持时间不满足,就可能产生亚稳态。当信号

2021-07-23 11:03:11 5493

5493

作者:Julian Hagedorn

欢迎阅读TI 最新《定时决定一切》系列博客文章的第一篇!在本系列中,您会发现我们

2021-11-10 09:42:52 1626

1626

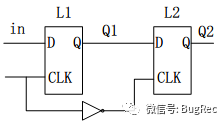

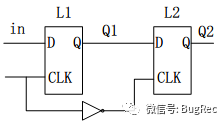

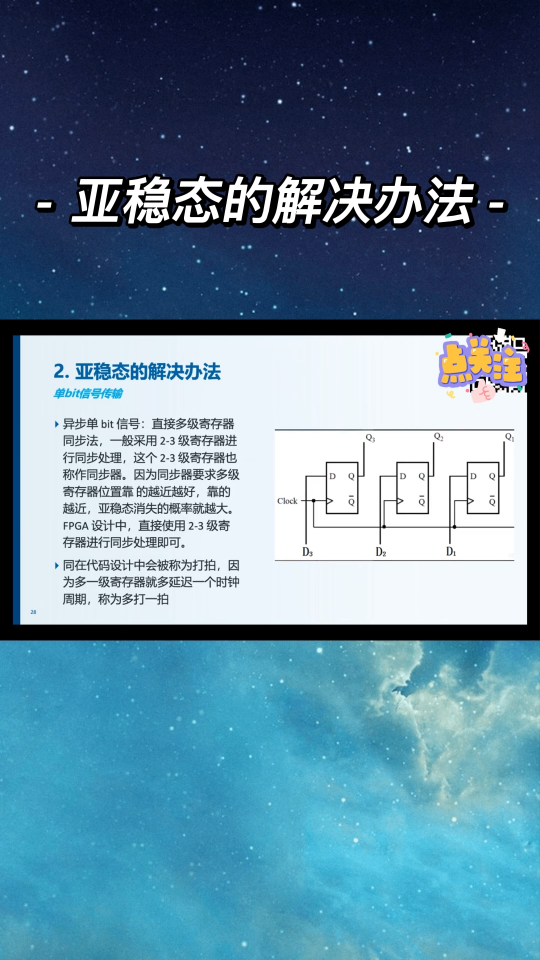

可能很多FPGA初学者在刚开始学习FPGA设计的时候(当然也包括我自己),经常听到类似于”这个信号需要打一拍、打两拍(寄存),以防止亚稳态问题的产生“这种话,但是对这个打拍和亚稳态问题还是一知半解,接下来结合一些资料谈下自己的理解。

2022-02-26 18:43:04 9404

9404

亚稳态问题是数字电路中很重要的问题,因为现实世界是一个异步的世界,所以亚稳态是无法避免的,并且亚稳态应该也是面试常考的考点。

2022-09-07 14:28:37 818

818 亚稳态问题是数字电路中很重要的问题,因为现实世界是一个异步的世界,所以亚稳态是无法避免的,并且亚稳态应该也是面试常考的考点。

2022-09-07 14:28:00 11347

11347 亚稳态是我们在设计经常遇到的问题。这个错误我在很多设计中都看到过。有人可能觉得不以为然,其实你现在没有遇到问题只能说明。

2022-10-10 09:30:10 1217

1217 即使 “打两拍”能阻止“亚稳态的传递”,但亚稳态导致后续FF sample到的值依然不一定是符合预期的值,那 “错误的值” 难道不依然会向后传递,从而造成错误的后果吗?

2022-10-19 14:14:38 2179

2179 FemtoFET MOSFETs:沙粒般渺小,一切尽在间距

2022-11-02 08:16:22 0

0 在使用负载开关时,时序决定一切!

2022-11-03 08:04:38 0

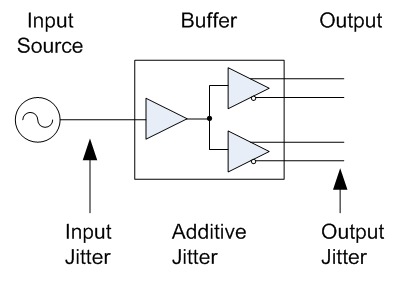

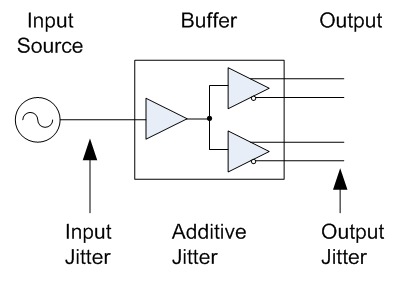

0 定时决定一切:抖动技术规范

2022-11-04 09:52:13 0

0 定时决定一切:如何使用部分 PLL 创建调制波形

2022-11-04 09:52:13 0

0 定时决定一切:如何测量附加抖动

2022-11-04 09:52:13 0

0 一个不稳定的状态,无法确定是1还是0,我们称之为亚稳态。这个亚稳态的信号会在一段时间内处于震荡状态,直到稳定,而稳定后的状态值与被采样值无关,可能是0也可能是1。

2022-12-12 14:27:52 1713

1713 关于步进电机你需要知道的一切

2023-03-07 16:58:21 3028

3028

一切从用户需求出发,一切为了用户的智慧家庭生活体验。

2023-04-25 13:35:45 1066

1066 本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D触发器与亚稳态的那些事。

2023-05-12 16:37:31 2934

2934

亚稳态在电路设计中是常见的属性现象,是指系统处于一种不稳定的状态,虽然不是平衡状态,但可在短时间内保持相对稳定的状态。对工程师来说,亚稳态的存在可以带来独特的性质和应用,如非晶态材料、晶体缺陷等

2023-05-18 11:03:22 6015

6015 前面在时序分析中提到过亚稳态的概念,每天学习一点FPGA知识点(9)之时序分析并且在电路设计中如果不满足Tsu(建立时间)和Th(保持时间),很容易就出现亚稳态;在跨时钟域传输的一系列措施也是为了降低亚稳态发生的概率。

2023-05-25 15:55:43 2832

2832

点击上方 蓝字 关注我们 1.1 亚稳态发生原因 在 FPGA 系统中,如果数据传输中不满足 触发器 的Tsu和Th不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery

2023-06-03 07:05:01 2490

2490 本文主要介绍了亚稳态的分析与处理。

2023-06-21 14:38:43 5126

5126

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D触发器与亚稳态的那些事。

2023-07-25 10:45:39 2841

2841

亚稳态(Metastability)是由于输入信号违反了触发器的建立时间(Setup time)或保持时间(Hold time)而产生的。建立时间是指在时钟上升沿到来前的一段时间,数据信号就要

2023-09-19 09:27:49 1841

1841

说起亚稳态,首先我们先来了解一下什么叫做亚稳态。亚稳态现象:信号在无关信号或者异步时钟域之间传输时导致数字器件失效的一种现象。

2023-09-19 15:18:05 3140

3140

所谓一切皆文件就是指计算机操作系统将一切计算机的可用资源都映射成文件形式向使用者提供统一的操作方式。

2023-10-11 10:10:21 1229

1229 复位信号存在亚稳态,有危险吗? 复位信号在电子设备中起着重要的作用,它用于使设备回到初始状态,以确保设备的正常运行。然而,我们有时会发现复位信号存在亚稳态,这意味着信号在一定时间内未能完全复位,并

2024-01-16 16:25:56 1170

1170 两级触发器同步,就能消除亚稳态吗? 两级触发器同步可以帮助消除亚稳态。本文将详细解释两级触发器同步原理、亚稳态的定义和产生原因、以及两级触发器同步如何消除亚稳态的机制。 1. 两级触发器同步

2024-01-16 16:29:38 2541

2541 在数字电路的设计与实现中,亚稳态是一个不可忽视的现象。它可能由多种因素引发,对电路的稳定性和可靠性产生严重影响。本文将深入探讨数字电路中亚稳态的概念、产生原因、影响以及应对策略,以期为读者提供全面而深入的理解。

2024-05-21 15:29:41 2945

2945

电子发烧友App

电子发烧友App

评论