亚稳态在电路设计中是常见的属性现象,是指系统处于一种不稳定的状态,虽然不是平衡状态,但可在短时间内保持相对稳定的状态。对工程师来说,亚稳态的存在可以带来独特的性质和应用,如非晶态材料、晶体缺陷等。

在材料制备和应用方面,亚稳态也常常是一个挑战。如何克服亚稳态,使材料转化为更稳定的状态,是一个重要的问题。以下是一些克服亚稳态的方法:

1、热处理

热处理是一种克服亚稳态的有效方法。通过加热材料至一定温度,可以使材料的能量增加,从而突破亚稳态的能垒,转变为稳定态。热处理也可以用于改变材料的结构和性质,例如退火可以使晶体缺陷减少,晶粒长大,提高材料的强度和韧性。

2、添加合金元素

添加合金元素也是一种克服亚稳态的方法。合金元素可以改变材料的晶体结构和化学成分,从而降低能垒,使亚稳态转变为稳定态。例如,将锂添加到钢中可以形成亚稳态的奥氏体,从而提高钢的强度和塑性。

3、热机械处理

热机械处理是一种将热处理和机械加工结合起来的方法,可以通过热压、轧制等方式将材料加工成形,使其突破亚稳态能垒,转变为稳定态。例如,通过轧制可以将亚稳态的合金材料转变为均匀的晶粒结构,提高材料的强度和韧性。

总之,亚稳态是一种普遍存在的现象。在材料制备和应用方面,克服亚稳态是一个重要的问题。采用热处理、添加合金元素和热机械处理等方法,可以提高材料的稳定性和性能。

-

电路设计

+关注

关注

6732文章

2576浏览量

217991 -

热处理

+关注

关注

0文章

118浏览量

18806 -

亚稳态

+关注

关注

0文章

47浏览量

13651

发布评论请先 登录

利用IDDR简化亚稳态方案

xilinx资料:利用IDDR简化亚稳态

FPGA中亚稳态——让你无处可逃

FPGA触发器的亚稳态认识

亚稳态问题解析

简谈FPGA学习中亚稳态现象

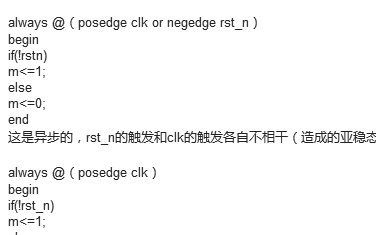

在FPGA复位电路中产生亚稳态的原因

FPGA--中复位电路产生亚稳态的原因

简谈FPGA学习中亚稳态现象

什么是亚稳态?如何克服亚稳态?

什么是亚稳态?如何克服亚稳态?

评论