亚稳态是我们在设计经常遇到的问题。这个错误我在很多设计中都看到过。有人可能觉得不以为然,其实你现在没有遇到问题只能说明:

1. 你的发货量还没到一定的量级。

2. 你很幸运。

当问题一旦发生的时候,亚稳态的问题是非常难以定量的分析的,甚至复现也是非常困难的。为了不让这样的“玄学”问题困扰我们,我们在设计调试的时候,首先要把这类问题规避,才有助于我们拨开迷雾,找到问题的原因。设计的检视也非常重要,不能说功能测试通过了,小批量发货没有问题产品就没有潜在的隐患。

亚稳态与设计可靠性

设计数字电路时大家都知道同步是非常重要的,特别当要输入一个信号到一个同步电路中,但是该信号由另一个时钟驱动时,这是要在接口处采取一些措施,使输入的异步信号同步化,否则电路将无法正常工作,因为输入端很可能出现亚稳态(Metastability),导致采样错误。这里我们对亚稳态的起因、危害、对可靠性的影响和消除仿真做一些介绍。

1.亚稳态发生的原因

在同步系统中,如果触发器的setup time / hold time不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端毛刺、振荡、固定的某一电压值,而不是等于数据输入端D的值。这段之间成为决断时间(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是究竟是0还是1,这是随机的,与输入没有必然的关系。

2.亚稳态的危害

由于输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值,因此亚稳态除了导致逻辑误判之外,输出0~1之间的中间电压值还会使下一级产生亚稳态(即导致亚稳态的传播)。

逻辑误判有可能通过电路的特殊设计减轻危害(如异步FIFO中Gray码计数器的作用),而亚稳态的传播则扩大了故障面,难以处理。

3.亚稳态的解决办法

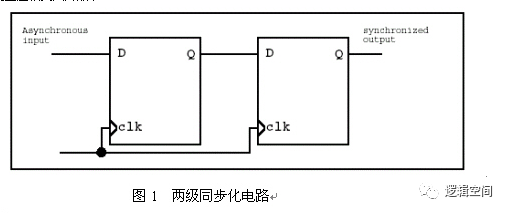

只要系统中有异步元件,亚稳态就是无法避免的,因此设计的电路首先要减少亚稳态导致错误的发生,其次要使系统对产生的错误不敏感。前者要靠同步来实现,而后者根据不同的设计应用有不同的处理办法。用同步来减少亚稳态发生机会的典型电路如图1所示。

在图1中,左边为异步输入端,经过两级触发器同步,在右边的输出将是同步的,而且该输出基本不存在亚稳态。其原理是即使第一个触发器的输出端存在亚稳态,经过一个CLK周期后,第二个触发器D端的电平仍未稳定的概率非常小,因此第二个触发器Q端基本不会产生亚稳态。注意,这里说的是“基本”,也就是无法“根除”,那么如果第二个触发器Q出现了亚稳态会有什么后果呢?后果的严重程度是由你的设计决定的,如果系统对产生的错误不敏感,那么系统可能正常工作,或者经过短暂的异常之后可以恢复正常工作,例如设计异步FIFO时使用格雷码计数器当读写地址的指针就是处于这方面的考虑。如果设计上没有考虑如何降低系统对亚稳态的敏感程度,那么一旦出现亚稳态,系统可能就崩溃了。

4.亚稳态与系统可靠性

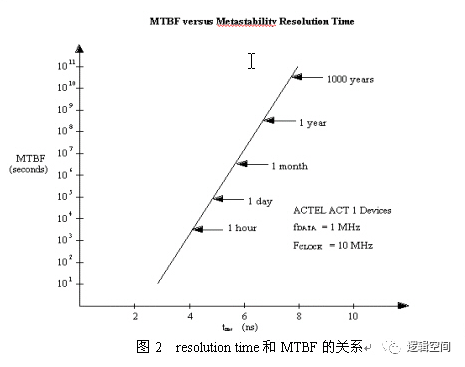

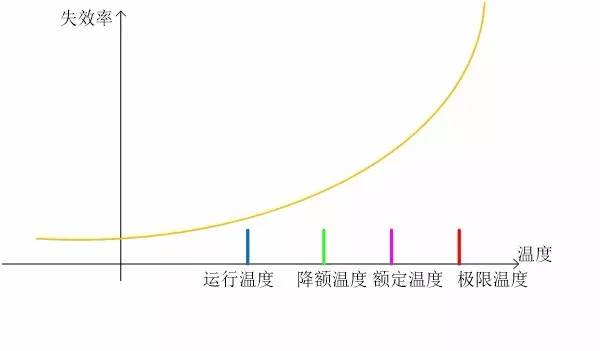

使用同步电路以后,亚稳态仍然有发生的可能,与此相连的是MTBF(Mean Time Between Failure),亚稳态的发生概率与时钟频率无关,但是MTBF与时钟有密切关系。有文章提供了一个例子,某一系统在20MHz时钟下工作时,MTBF约为50年,但是时钟频率提高到40MHz时,MTBF只有1分钟!可见降低时钟频率可以大大减小亚稳态导致系统错误的出现,其原因在于,提供较长的resolution time可减小亚稳态传递到下一级的机会,提高系统的MTBF,如图2所示。

5.总结

亚稳态与设计可靠性有非常密切的关系,当前对很多设计来说,实现需要的功能并不困难,难的是提高系统的稳定性、可靠性,较小亚稳态发生的概率,并降低系统对亚稳态错误的敏感程度可以提高系统的可靠性。

审核编辑:汤梓红

-

数字电路

+关注

关注

193文章

1648浏览量

83021 -

亚稳态

+关注

关注

0文章

47浏览量

13649 -

可靠性

+关注

关注

4文章

277浏览量

27503

原文标题:亚稳态的传播

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

利用IDDR简化亚稳态方案

FPGA同步复位和异步复位的可靠性特点及优缺点

xilinx资料:利用IDDR简化亚稳态

FPGA触发器的亚稳态认识

亚稳态问题解析

在FPGA复位电路中产生亚稳态的原因

亚稳态与设计可靠性

亚稳态与设计可靠性的关系

亚稳态与设计可靠性的关系

评论