今天写一下时序问题常见的跨时钟域的亚稳态问题。

先说明一下亚稳态问题:

D触发器有个明显的特征就是建立时间(setup time)和保持时间(hold time)

如果输入信号在建立时间和保持时间发生变化,则可能产生亚稳态,如果在时钟上升沿也就是D触发器采样期间,输入点评判断为1则输出为1,如果是0则输出为0,另外一种情况就是在时钟上升沿时,D在发生变化,在中间思考跳转很久,但不知道Dinput跳到0还是1(此状态出现概率非常低,但会出现)到下一个时钟还没有思考好是0还是1,没有出现稳定状态,这就是亚稳态。[1]

总结:在FPGA系统中,如果数据传输中不满足触发器的Tsu和Th不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据输入端D的值。这段时间称为决断时间(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是稳定到0或者1,是随机的,与输入没有必然的关系。[2]

总结亚稳态问题产生场景:1)跨时钟域的信号传输,由于源信号时钟与目的信号时钟的相移未知,可能导致保持时间和建立时间条件不满足,从而产生亚稳态现象。2)异步信号,最常见的为异步复位信号,由于异步信号不与触发器同步时钟同步,所以可能导致保持时间和建立时间条件不满足,产生亚稳态现象。

(建立时间保持时间条件:数据在建立时间和保持时间保持稳定)

亚稳态导致的后果:

一般情况下亚稳态产生的后果为产生不可预知的数据,或者在前面所述亚稳态第三种情况可能导致系统崩溃。在数据表现方面来说会产生毛刺、突变等现象。影响系统后续的逻辑判断和程序整体运行走向。

一般FPGA的建立时间和保持时间加起来为1ns左右,所以可以根据概率论来计算亚稳态产生的概率,也就是同步时钟周期的倒数。

亚稳态的串扰,也就是D触发器处于震荡状态时会影响后续触发器的状态,一般来说如果震荡状态不超过同步时钟周期,也就不会串扰下一个触发器导致下一个触发器也产生振荡,一般工程上来讲串两至三个触发器基本就可以保证不串扰。(是可能不串扰,不是一定不串扰,串扰的可能性很小)

针对上述的亚稳态问题,常见的解决方法:

1)通过对异步信号边沿提取实现异步信号同步处理,在边沿提取过程中也要防止亚稳态串扰,进行多寄存器缓存减小亚稳态串扰的可能性。

2)通过FIFO实现异步信号同步处理。

3)对于异步时钟通过异步复位同步释放的方法实现亚稳态大可能的消除:

异步复位,同步释放就是对异步复位时钟进行两次或两次以上缓存,尽可能的减少亚稳态信号进入到系统内部。

在进行异步复位同步释放的时候一定能够要进行至少两次缓存,这样才能保证亚稳态串扰的可能性大大降低。

原文标题:【FPGA】几种时序问题的常见解决方法

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

时钟

+关注

关注

11文章

1999浏览量

135238 -

时序设计

+关注

关注

0文章

22浏览量

44143

原文标题:【FPGA】几种时序问题的常见解决方法

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

英诺达ECDC上线RDC跨复位域检查新功能

为何跨复位域问题是危险的“芯片杀手”

CD4047B:CMOS低功耗单稳态/无稳态多谐振荡器的设计与应用

什么是位域

CD4047B:低功耗单稳态/无稳态多谐振荡器的设计与应用

如何降低系统时钟频率?

航盛电子搭载QNX技术的墨子跨域融合平台正式量产

黑芝麻智能武当C1200家族作为跨域计算芯片的核心突破

vivado时序分析相关经验

移植E203到Genesys2开发板时遇到时序问题的常见原因

时钟设计优化实战

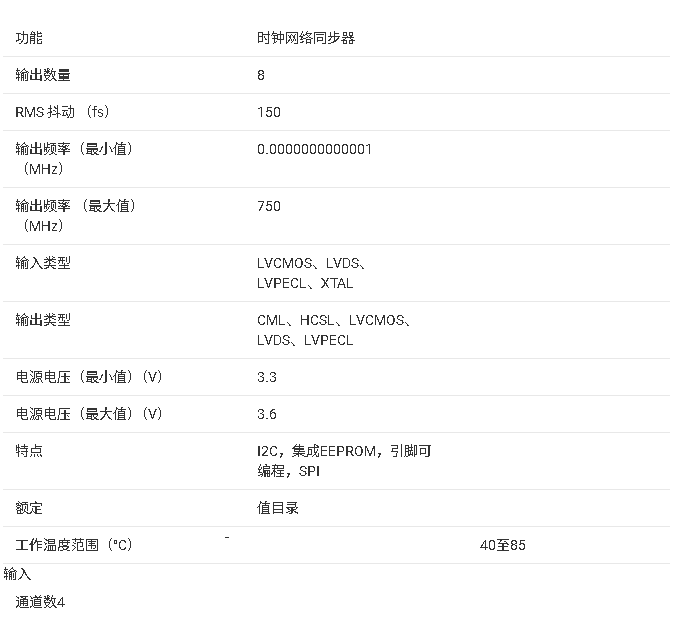

LMK05028 低抖动双通道网络同步器时钟芯片总结

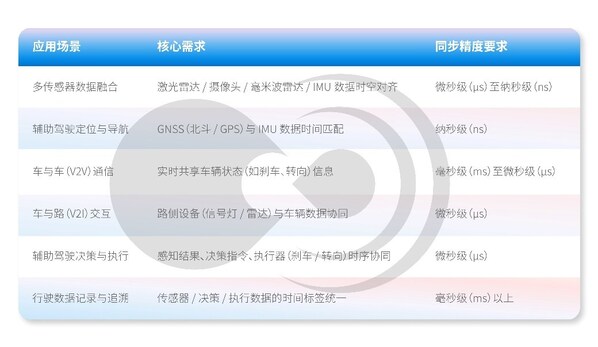

黑芝麻智能跨域时间同步技术:消除多域计算单元的时钟信任鸿沟

跨异步时钟域处理方法大全

时序问题常见的跨时钟域亚稳态问题

时序问题常见的跨时钟域亚稳态问题

评论