单片机主要作用是控制外围的器件,并实现一定的通信和数据处理。但在某些特定场合,不可避免地要用到数学运算,尽管单片机并不擅长实现算法和进行复杂的运算。下面主要是介绍如何用单片机实现数字滤波。

2018-02-28 09:41:12 9544

9544

我们为了实现动态图像的滤波算法,用串口发送图像数据到FPGA开发板,经FPGA进行图像处理算法后,动态显示到VGA显示屏上,前面我们把硬件平台已经搭建完成了,后面我们将利用这个硬件基础平台

2019-01-02 16:26:23 5687

5687 前面发过中值、均值、高斯滤波的文章,这些只考虑了位置,并没有考虑相似度。那么双边滤波来了,既考虑了位置,有考虑了相似度,对边缘的保持比前几个好很多,当然实现上也是复杂很多。本文将从原理入手,采用Matlab与FPGA设计实现双边滤波算法。

2025-07-10 11:28:12 4272

4272

根据交流采样的原理,设计出基于FPGA开方算法,解决了实时计算电压有效值和频率的问题。充分发挥FPGA硬件并行计算的特性,实现高速运算和可靠性的结合, 能够较好地解决精度与速度

2011-10-03 11:02:02 3365

3365 如何用FPGA实现串行算法?我想用FPGA做一个随机数发生器,然后想用李世刚那个超素数法,但是要生成1024bit的01序列,它们是用第一bit顺推第二bit 的产生。请问大神 ,有没有没有好的办法

2013-03-11 19:23:49

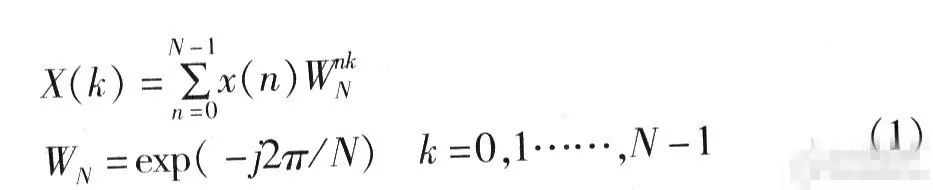

流水方式对复数数据实现了加窗、FFT、求模平方三种运算。整个设计采用流水与并行方式尽量避免瓶颈的出现,提高系统时钟频率,达到高速处理。实验表明此处理器既有专用ASIC电路的快速性,又有DSP器件的灵活性的特点,适合用于高速数字信号处理。

2012-08-12 11:49:01

采集数据中的量化噪声,在进行数据压缩前采用滤波的预处理技术。介绍LZW算法和滑动滤波算法的基本理论,详细阐述用单片FPGA实现两种算法的方法。最终测试结果表明,该设计方案能够有效滤除数据中的高频噪声

2010-04-24 09:05:21

的数据处理和预处理,实现实时计算和反馈。

二、数据传输与处理FPGA在自动驾驶中扮演着数据传输和处理的角色。它能够支持多种传感器(如激光雷达、摄像头、GPS等)的数据传输,并通过其高速的数据处理能力,实现

2024-07-29 17:09:16

本帖最后由 eehome 于 2013-1-5 10:03 编辑

fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点

2012-08-11 18:27:41

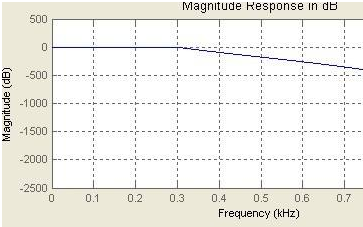

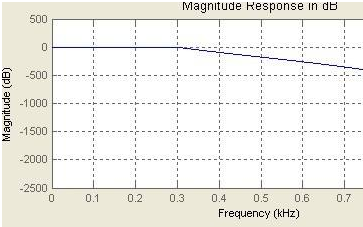

fpga实现滤波器fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点。本文研究了一种16阶FIR滤波器的FPGA设计方法

2012-08-12 11:50:16

4 个时钟后连续输出运算结果。各个单元协调一致的并行工作, 提高了系统时钟频率, 达到了高速处理。采用块浮点机制, 动态扩大数据范围, 在速度和精度之间得到折衷。模块化设计, 易于实现更多

2017-11-21 15:55:13

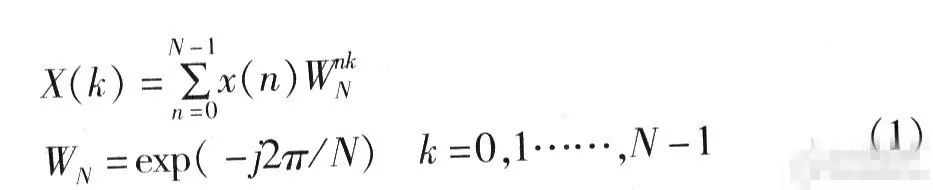

在信号处理中,FFT占有很重要的位置,其运算时间影响整个系统的性能。传统的实现方法速度很慢,难以满足信号处理的实时性要求。针对这个问题,本文研究了基于FPGA芯片的FFT算法,把FFT算法对实时性

2010-05-28 13:38:38

实现各种数字信号处理算法的工程方法。本书将理论与实践相结合,给出了相应算法的硬件结构,并配有时序图,以帮助读者深入理解设计思路。第1章 现场可编程逻辑门阵列(FPGA)技术现状1.1 FPGA已进入

2012-04-24 09:33:23

摘要针对FFT算法基于FPGA实现可配置的IP核。采用基于流水线结构和快速并行算法实现了蝶形运算和4k点FFT的输入点数、数据位宽、分解基自由配置。使用Verilog语言编写,利用ModelSim

2019-07-03 07:56:53

)、离散余弦变换(DCT)、小波变换、数字滤波器(有限脉冲响应(FIR)、无限脉冲响应(IIR)和自适应滤波器)以及数字上下变频器。这些算法中,每一种都有一些结构性的元件可以用并行方法实现。而FPGA

2021-12-15 06:30:00

TMS320C6713.处理能力高达2400MIPS,结合该芯片的8指令并行运行的特点,对程序进行优化,可大大提高运算速度,实现“二次解调”实时处理算法。3. 数据处理3.1 PGC解调原理PGC解调

2021-07-05 11:23:33

传输,因而只能做需求数据较少的测向工作,并不能做实时波束形成。为了克服这些困难,这里将测向数据和波束形成数据分开进行传输,采用LVDS技术解决多通道高速数据传输,选择内置高性能DSP内核的高密度FPGA并行实现波束形成中的大量复乘运算。

2020-11-25 06:49:42

的并行运算单元。4 结 论 本文阐述了无源雷达系统中基于FPGA的实时互相关运算器的一种实现方案。该运算器由1块500 000门的FPGA芯片完成2路信号的互相

2009-09-19 09:25:42

运行时, FPGA 并行运算平台首先完成对摄像头的初始化和寄存器配置,配置完成之后读取实时的图像数据存入 SDRAM 存储器中,在 FPGA 芯片内部并行实现图像处理算法,对从 SDRAM 中读出的数据

2024-05-24 07:45:44

基于FPGA的高速实时图像采集和自适应阈值算法提出了基于FPGA的图像处理自适应阈值算法,实现了激光光斑中心的高速实时检测。采用3×3窗口模块和自适应阈值模块,先对CCD输入数据进行处理,判断光斑

2012-08-11 15:38:18

` 本帖最后由 ninghechuan 于 2017-9-1 07:04 编辑

在这一篇开篇之前,我需要解决一个问题,上一篇我们实现了基于FPGA的均值滤波算法的实现,最后的显示效果图上发现有

2017-09-01 07:04:36

` 本帖最后由 ninghechuan 于 2017-8-30 08:20 编辑

我们为了实现动态图像的滤波算法,用串口发送图像数据到FPGA开发板,经FPGA进行图像处理算法后,动态显示到

2017-08-28 11:34:10

:基于FPGA的均值滤波算法实现第五篇:深刻认识ShiftRAM学习笔记番外篇:数字图像处理界标准图像 Lena 后面的故事第六篇:基于FPGA的中值滤波算法实现第七篇:基于FPGA的Sobel边缘检测的实现

2017-09-22 13:20:55

基于FPGA的超高速FFT硬件实现介绍了频域抽取基二快速傅里叶运算的基本原理;讨论了基于FPGA达4 096点的大点数超高速FFT硬件系统设计与实现方法,当多组大点数进行FFT运算时,利用FPGA

2009-06-14 00:19:55

传统数字滤波器硬件的实现主要采用专用集成电路(ASIC)和数字信号处理器(DSP)来实现。FPGA内部的功能块中采用了SRAM的查找表(lo-ok up table,LUT)结构,这种结构特别适用于并行处理结构,相对于传统方法来说,其并行度和扩展性都很好,它逐渐成为构造可编程高性能算法结构的新选择。

2019-10-22 07:14:04

跪求各位大神有没有基于verilog HDL的高速对数运算模块设计的CORD IC算法实现自然对数运算的代码

2016-03-10 12:39:28

,每相仍然相当于低阶的FIR滤波器,下节对其采用DA算法,可以看到运算速度将进一步提高,运算量也将大幅减少。3、多速率DA根升余弦滤波器的结构及其FPGA实现按查找表的方式,DA算法可以分为串行实现

2024-03-25 14:21:38

请问一下如何用FPGA实现FFT算法?

2021-04-08 06:06:26

对于自主机器人导航和其它机器视觉应用来说,实时深度感知是很关键的。目前通过立体图像来计算深度的算法计算量很大,例如差异测绘,要占用CPU大量的时间,或者需要用昂贵的器件进行实时操作。

2019-10-17 08:28:30

如何用中档FPGA实现多相滤波器?

2021-04-29 06:30:57

单片机主要作用是控制外围的器件,并实现一定的通信和数据处理。但在某些特定场合,不可避免地要用到数学运算,尽管单片机并不擅长实现算法和进行复杂的运算。下面主要是介绍如何用单片机实现数字滤波。在单片机

2021-01-13 07:29:27

单片机主要作用是控制外围的器件,并实现一定的通信和数据处理。但在某些特定场合,不可避免地要用到数学运算,尽管单片机并不擅长实现算法和进行复杂的运算。下面主要是介绍如何用单片机实现数字滤波...

2022-01-07 06:30:56

处理器(FPGA,DSP)是一个“瓶颈”;基于多相滤波的信道化接收机抽取在滤波之前,运算量小,且输出速率低,便于FPGA实现,这使得在一片FPGA中实现数字信道化成为可能。

2019-08-22 08:01:34

本文利用FPGA乘累加的快速算法,可以设计出高速的FIR数字滤波器,使FPGA在数字信号处理方面有了长足的发展。

2021-05-07 06:31:21

能够充分利用有限位长。这样处理比定点方法扩大了动态范围,并且提高了精度,比浮点运算在速度上有了提高。块浮点结构如图4所示。3 结 语着重讨论基于FPGA的64点高速FFT算法的实现方法。采用高基数结构和流水线

2019-06-17 09:01:35

嗨,我是Xilinx FPGA的新手。我该如何在FPGA中实现实时时钟或时间和日期计数器?Xilinx是否为Artix 7提供任何RTC核心或IP?非常感谢您的建议。

2020-05-22 12:41:35

在IPSec协议中认证使用SHA-1和MD5单向散列函数算法实现,通过使用FPGA高速实现SHA-1消息认证算法。

2021-04-13 06:02:01

本文研究的就是在FPGA设计平台上设计硬件电路,实现数字图像的空域滤波算法。

2021-04-30 06:29:41

现代通信信号处理发展到3G、4G时代后,每秒上百兆比特处理速度的要求对于自适应处理技术是一个极大的挑战。使用具有高度并行结构的FPGA实现自适应算法以及完成相应的调整和优化,相比于在DSP芯片上的算法实现可以达到更高的运行速度。

2019-08-23 08:03:10

的信息并行存在,因此可以并行对其施以相同的操作,使得图像处理的速度大大提高,这正好适合映射到FPGA架构中用硬件算法得以实现。本篇阐述了基于FPGA设计一个能够实时采集、实时处理并实时显示的数字图像处理系统的设计思想和流程,分析了摄像头接口的时序;阐述了图像...

2021-07-28 06:06:26

想用FPGA实现双边滤波算法,有懂得能说一下具体的实现步骤吗

2017-03-21 15:41:13

分布式的滤波器算法是什么?一种基于FPGA分布式算法的滤波器设计实现

2021-04-29 07:13:23

用FPGA硬件实现。 现在我没有FPGA硬件实现的经验,不知道如何用FPGA硬件实现小波算法。 恳请赐教!谢谢!

2012-11-20 21:35:16

单片机主要作用是控制外围的器件,并实现一定的通信和数据处理。但在某些特定场合,不可避免地要用到数学运算,尽管单片机并不擅长实现算法和进行复杂的运算。下面主要是介绍如何用单片机实现数字滤波。在单片机

2022-01-18 07:00:34

FIR数字滤波器分布式算法的原理及FPGA实现摘要:在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘积-积结构相比,具有并行处理的高效性特点。详细研

2009-10-27 14:05:48 57

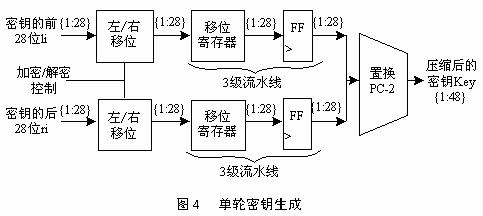

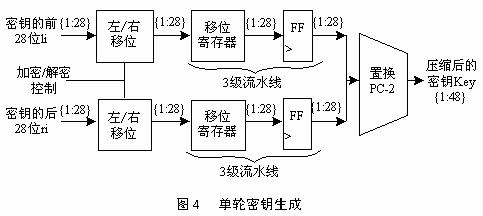

57 介绍AES 算法的原理以及基于FPGA 的高速实现。结合算法和FPGA 的特点,采用查表法优化处理了字节代换运算、列混合运算。同时,为了提高系统工作速度,在设计中应用了内外结合

2010-01-25 14:26:51 29

29 介绍AES算法的原理以及基于FPGA的高速实现。结合算法和FPGA的特点,采用查表法优化处理了字节代换运算、列混合运算。同时,为了提高系统工作速度,在设计中应用了内外结合的流水线

2010-07-17 18:09:43 46

46 摘要:介绍3-DES算法的概要;以Xilinx公司SPARTANII结构的XC2S100为例,阐述用FPGA高速实现3-DES算法的设计要点及关键部分的设计。引 言

2006-03-13 19:36:42 1016

1016

如何用用FPGA实现FIR滤波器

你接到要求用FPGA实现FIR滤波器的任务时,也许会想起在学校里所学的FIR基础知识,但是下一步该做什么呢?哪些参数是重

2009-03-30 12:25:45 4905

4905

摘要: 针对在FPGA中实现FIR滤波器的关键--乘法运算的高效实现进行了研究,给了了将乘法化为查表的DA算法,并采用这一算法设计了FIR滤波器。通过FPGA仿零点验证

2009-06-20 14:09:36 1050

1050

摘要:介绍3-DES算法的概要;以Xilinx公司SPARTANII结构的XC2S100为例,阐述用FPGA高速实现3-DES算法的设计要点及关键部分的设计。

关键词:3-DES

2009-06-20 14:22:00 1600

1600

本文介绍的基于PCI总线的FPGA计算平台的系统实现:通过在PC机上插入扩展PCI卡,对算法进行针对并行运算的设计,提升普通PC机对大计算量数字信号的处理速度。本设计采用5片FPGA芯片及

2011-08-21 18:05:31 2415

2415

提出了一种适用于FPGA的改进型线性插值算法,该算法基于并行流水线方式实现,充分发挥了FPGA的高速并行处理能力。

2011-11-22 14:29:49 1509

1509

基于FPGA的高速实时图像采集和自适应阈值算法

2016-05-10 13:45:28 21

21 实时图像增强算法改进及FPGA实现,下来看看

2016-09-17 07:28:24 15

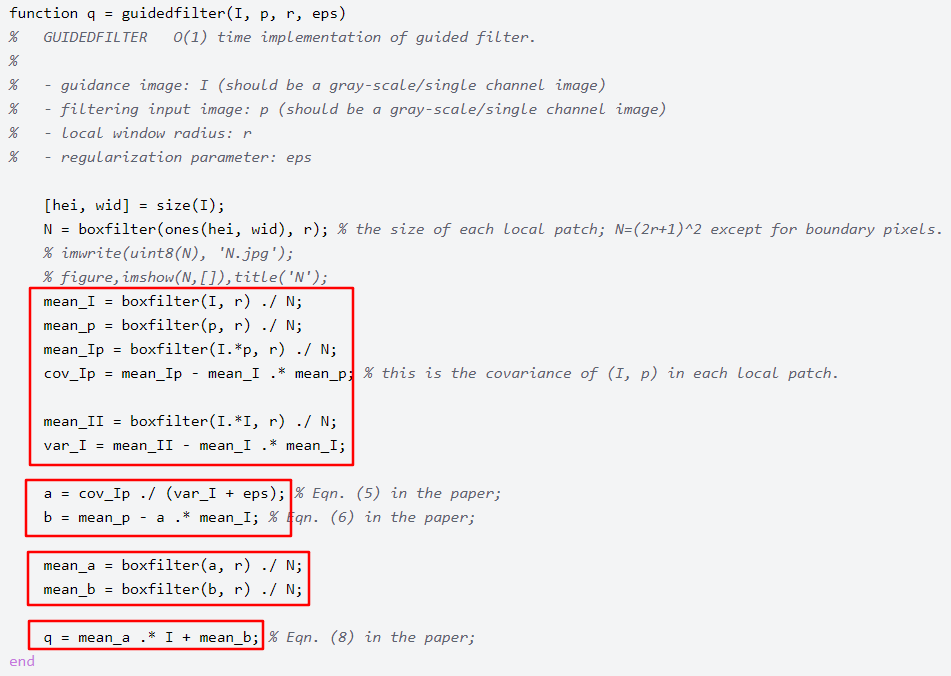

15 基于改进的引导滤波算法的多曝光图像融合

2017-01-08 14:47:53 3

3 基于FPGA的实时图像中值滤波算法及实现_蒋涛

2017-03-19 11:38:26 15

15 针对传统CORDIC算法流水线结构的迭代次数过多,运算速度不够快,消耗硬件资源较多的缺点,改进了一种基于旋转模式并行运算的CORDIC算法。该算法采用二进制两极编码和微旋转角编码进行低位符号预测和高

2017-11-16 10:46:22 14

14 引导滤波算法被大量用于图像处理领域中,在去雨雪、去雾、前景提取、图像去噪、图像增强、级联采样等方面有很好的处理效果。但是对于实时应用,软件实现难以满足需要。提出了在SDSoC环境下利用软硬件协同开发

2017-11-16 14:40:18 1979

1979 随着高性能信号处理系统对运算速度、通信速率等要求的不断提高,单独的处理器(如FPGA或DSP)无法满足高速实时信号处理的需求。TI公司的多核DSP处理性能强大,但是并行性不强,难以适应计算异常密集

2017-11-17 03:11:01 32633

32633

线性相位FIR滤波器的对称性减小了硬件规模;利用分割查找表的方法减小了存储空间;采用并行分布式算法结构和流水线技术提高了滤波器的速度,在FPGA上实现了该滤波器。

2017-11-24 15:17:27 3615

3615 FPGA仿真篇-使用脚本命令来加速仿真二 基于FPGA的HDMI高清显示借口驱动 基于FPGA灰度图像高斯滤波算法的实现 FPGA为什么比CPU和GPU快 基于Xilinx FPGA的视频图像采集

2018-02-20 20:49:00 7998

7998

,常规做法是利用插值和抽取的方法实现数字信号的变采样处理,这种方法实现复杂,硬件成本高。文中提出了一种高速并行成型滤波器的FPGA实现方法,这种基于群延时结构的查找表算法,所需的查找表只需存储单位冲击响应的采样值,

2018-02-23 10:14:22 0

0 结构复杂,采用DSP实现会增加系统负担,降低系统速度。在某些对速度要求较高的情况,必须采用专门的浮点运算处理器。 EDA/FPGA技术不断发展,其高速、应用灵活、低成本的优点使其广泛应用数字信号处理领域。在FPCA技术应用的初期,

2018-04-10 14:25:53 17

17 本文是基于FPGA实现Cordic算法的设计与验证,使用Verilog HDL设计,初步可实现正弦、余弦、反正切函数的实现。将复杂的运算转化成FPGA擅长的加减法和乘法,而乘法运算可以用移位运算代替

2018-07-03 10:18:00 3415

3415

数据采集系统的总体架构如图1所示,其中PCI核、DMA控制器与A/D控制器均在FPGA内部实现。为实现多路并行采样,可选用多片A/D器件并行处理的方式,在FPGA的高速状态机控制下,完成模拟信号经过

2018-08-28 10:16:07 14862

14862

开方运算作为数字信号处理(DSP)领域内的一种基本运算,其基于现场可编程门列(FPGA)的工程实现具有较高的难度。本文分析比较了实现开方运算的牛顿-莱福森算法,逐次逼近算法,非冗余开方算法3种算法

2020-08-06 17:58:15 6

6 在分析传统自适应滤波算法的基础上,针对自适应滤波器的硬件实现,采用一种适合FPGA实现的DLMS算法。使用VHDL语言完成设计,仿真实验验证了设计的正确性,经过编译和布局布线后对改进算法和传统算法进行了比较,结果表明改进算法在增加硬件消耗较少的情况下有效提高了系统工作频率。

2021-01-22 16:12:24 12

12 提出了一种基于多相滤波器的并行有限脉冲响应(finite impulse response,FIR)滤波器结构,可以有效提高滤波器运算的吞吐率,与传统的串行滤波器结构比,并行滤波器运算速度可以提高L

2021-01-28 17:22:00 15

15 提出了一种基于多相滤波器的并行有限脉冲响应(finite impulse response,FIR)滤波器结构,可以有效提高滤波器运算的吞吐率,与传统的串行滤波器结构比,并行滤波器运算速度可以提高L

2021-01-28 17:22:00 7

7 处理能力的现场可编程门阵列(FPGA)在成本、性能、体积等方面都显示出了优势。本文以此为背景,研究了基于FPGA的快速傅立叶变换、数字滤波、相关运算等数字信号处理算法的高效实现。

2021-02-01 16:11:00 17

17 FPGA,通过并行处理结构及流水线技术,可实时处理每秒50帧780×582×12bits的可见光图像。在处理视频的过程中,由前一帧图像的直方图信息,来增强后一帧图像。理论分析和实验结果均表明,该算法克服了直方图均衡及平台直方图均衡增强

2021-02-03 15:21:00 10

10 本文提出了一种用FPGA实现星载合成孔径雷达实时成像处理器的方法,用来实现星载SAR的CS算法(或RMA算法).该实时成像处理器由7片Xilinx公司的商业FI:‘GA实现,其中4片作为并行的处理

2021-02-05 15:22:46 14

14 提出一种新的高阶FIR滤波器的FPGA实现方法。该方法运用多相分解结构对高阶FIR滤波器进行降阶处理,采用改进的分布式算法来实现降阶后的FIR滤波器。设计了一系列阶数从8到1 024的FIR滤波

2021-03-23 15:44:54 31

31 及布局布线,并用ModelSim和Matlab对设计作了联合仿真。结果表明,通过利用FPGA器件中大量的乘法器、逻辑单元及存储器等硬件资源,采用全并行加流水结构,可在一个时钟节拍内完成32点FFT运算的功能,设计最高运算速度可达11 ns,可实现对高速A/D采样数据的实时处理.

2021-03-31 15:22:00 11

11 图像滤波是图像预处理过程中苇要的组成部分,而基于FPGA的滤波算法相对软件算法而言具有高度的并行性。能满足实时图像处理的要求.同时也具有灵活的硬件可编程性;简要说明了中值滤波的原理.介绍并比较了标准

2021-04-01 11:21:48 42

42 为了调整图像数据灰度,介绍了一种图像灰度级拉伸算法的FPGA实现方法,并针对FPGA的特点对算法的实现方法进行了研究,从而解决了其在导引系统应用中的实时性问题。仿真验证结果表明:基于FPGA的图像拉伸算法具有运算速度快,可靠性高,功耗低等特点,非常适合成像系统使用.

2021-04-01 14:14:49 10

10 为了调整图像数据灰度,介绍了一种图像灰度级拉伸算法的FPGA实现方法,并针对FPGA的特点对算法的实现方法进行了研究,从而解决了其在导引系统应用中的实时性问题。仿真验证结果表明:基于FPGA的图像拉伸算法具有运算速度快,可靠性高,功耗低等特点,非常适合成像系统使用.

2021-04-01 14:14:49 1

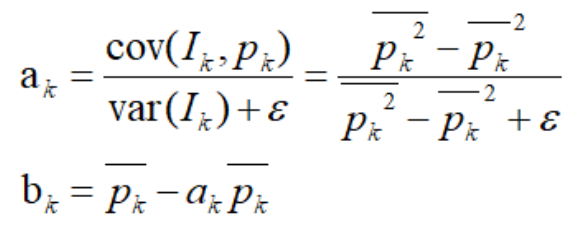

1 ,如何用FPGA并行高速运算,最小的代码实现实时的引导滤波算法。 首先,给出上篇中最后的matlab 引导滤波的代码,如下所示。 其中框框中为主要的计算过程,下一图为计算a/b的最后的公式(引导图=本身)。 双边滤波由于其只是在空间距

2021-08-10 14:27:15 5374

5374

单片机主要作用是控制外围的器件,并实现一定的通信和数据处理。但在某些特定场合,不可避免地要用到数学运算,尽管单片机并不擅长实现算法和进行复杂的运算。下面主要是介绍如何用单片机实现数字滤波。

2022-07-03 10:55:37 3221

3221 FPGA以擅长高速并行数据处理而闻名,从有线/无线通信到图像处理中各种DSP算法,再到现今火爆的AI应用,都离不开卷积、滤波、变换等基本的数学运算。

2022-10-31 14:48:15 4165

4165 和移位操作。这些结构需要占用器件较多的LE(逻辑元件)资源,设计周期长,工作频率低,实时性差。本文提出一种基于Stratix系列FPGA器件的新的实时高速脉动FIR滤波器的快速实现方法。利 用FGPA集成的DSP(数字信号处理器)乘加模块定制卷积运算单元,利用VHDL(甚高速集成电路硬件描述

2022-12-01 10:20:05 2154

2154 FPGA最大的优势体现在其低功耗和并行运算的特点上,数字图像蕴含数据量大,采用FPGA可以在保证低功率运算的情况下,有效提高图像算法的实时性。

2023-04-07 09:40:07 7159

7159 ,成本昂贵。随着FPGA发展,其资源丰富,易于组织流水和并行结构,将FFT实时性要求与FPGA器件设计的灵活性相结合,实现并行算法与硬件结构的优化配置,不仅可以提高处理速度,并且具有灵活性高。开发费用低

2023-05-11 15:31:41 3541

3541

由于FPGA可以对算法进行并行化,所以FPGA 非常适合在可编程逻辑中实现数学运算。

2023-05-15 11:29:15 4247

4247

本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的并行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了复现以及解读,并进行了仿真验证。

2023-05-24 10:57:36 1825

1825

各种不同的计算和处理任务,例如数字信号处理(DSP)、图像处理、机器学习、通信协议处理等。FPGA的特点使得它非常适合实现需要高度并行计算和低延迟的算法。

2023-08-16 14:31:23 3882

3882

长度N的平方成正比。当N较大时,因计算量太大,直接用DFT算法进行谱分析和信号的实时处理是不切实际的。快速傅立叶变换(Fast Fourier Transformation,简称FFT)使DFT运算效率

2023-10-09 14:30:02 2869

2869 引言 LMS(最小均方)算法因其收敛速度快及算法实现简单等特点在自适应滤波器、自适应天线阵技术等领域得到了十分广泛的应用。为了发挥算法的最佳性能,必须采用具有大动态范围及运算精度的浮点运算,而浮点

2023-12-21 16:40:01 1590

1590

电子发烧友App

电子发烧友App

评论