引言

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:快速实现基于FPGA的脉动FIR滤波器,VHDL,脉动阵列,PE处理单元,FIR滤波器

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1663文章

22493浏览量

638939

原文标题:快速实现基于FPGA的脉动FIR滤波器,VHDL,脉动阵列,PE处理单元,FIR滤波器

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

屏蔽电源滤波器的分类

屏蔽房用来屏蔽 辐射 干扰,而滤波器用来滤除 传导 干扰。没有滤波器,屏蔽房的整体隔离效果会下降60dB以上(相当于百万倍的效能损失),因此滤波器是屏蔽房发挥完整功能的核心部件。 来看下分类: 屏蔽

交流单相滤波器与三相滤波器的核心区别解析

选型和实现有效电能质量管理的基础。 一、结构设计与电路拓扑的根本差异 单相滤波器基于单相两线制系统设计,其电路结构相对简单。它通常由针对特定谐波频率设计的电感、电容等无源元件构成,形成一个独立的滤波支路。其核心任务

MAX262微处理器可编程通用有源滤波器:设计与应用指南

MAX260/MAX261/MAX262 微处理器可编程通用有源滤波器:设计与应用指南 在电子设计领域,滤波器是信号处理中不可或缺的组件。Maxim 公司的 MAX260/MAX261

基于卡尔曼滤波的无刷电机转矩脉动抑制研究

数据处理算法,卡尔曼滤波器同时具备良好的滤波特性。因此文章在分析永磁无刷直流电动机数学模型的基础上,提出了一种基于卡尔曼滤波的无刷直流电机转矩脉动

发表于 07-29 16:13

有源滤波器与无源滤波器的区别

滤波器是根据电路参数对电路频带宽度的影响而设计出来的工程应用电路,滤波器种类很多,有源滤波器和无源滤波器的区别我们最简单的分别办法是看看是否需要电源,在作用上最大的区别在于有源

GNSS 低噪声放大器前端模块,集成前滤波器和后滤波器 skyworksinc

电子发烧友网为你提供()GNSS 低噪声放大器前端模块,集成前滤波器和后滤波器相关产品参数、数据手册,更有GNSS 低噪声放大器前端模块,集成前滤波器和后滤波器的引脚图、接线图、封装手

发表于 06-06 18:34

Sky5® 低电流 GNSS LNA 前端模块,集成前置滤波器和后置滤波器 skyworksinc

电子发烧友网为你提供()Sky5® 低电流 GNSS LNA 前端模块,集成前置滤波器和后置滤波器相关产品参数、数据手册,更有Sky5® 低电流 GNSS LNA 前端模块,集成前置滤波器和后置

发表于 05-14 18:31

基于 FPGA 的任意波形发生器+低通滤波器系统设计

对图像进行平滑去噪处理。

本次设计将用两种方式实现低通滤波器。

方法一:利用Vivado自身具备的DDS和FIR的IP核实现;

方法二:通过

发表于 05-07 15:34

请问对SPDIF_Rx传来的48K,24Bit立体声信号作约160阶FIR电子二分频滤波器需怎样的MCU性能?

请问对SPDIF_Rx 传来的48K,24Bit立体声信号作约160阶FIR电子二分频滤波器需怎样的MCU性能?

发表于 04-29 07:00

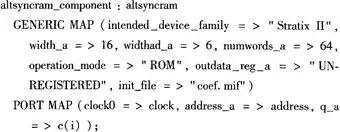

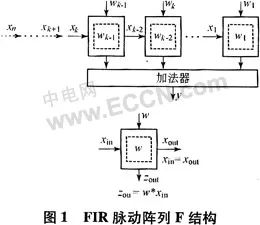

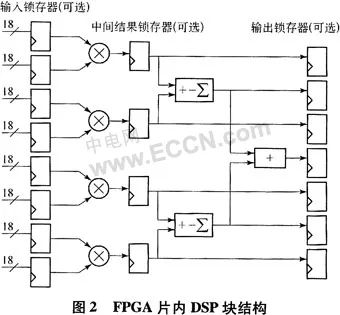

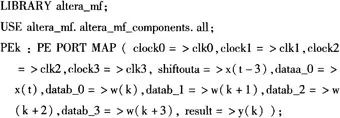

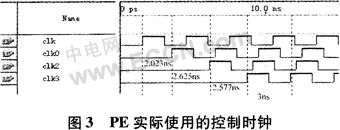

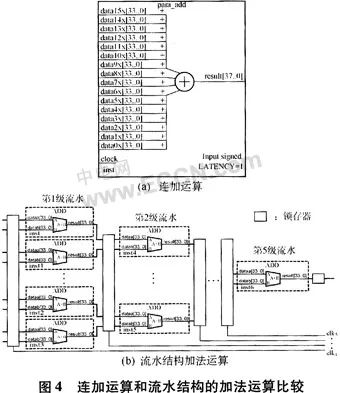

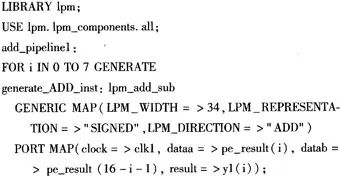

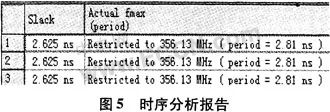

快速实现基于FPGA的脉动FIR滤波器,VHDL,脉动阵列,PE处理单元,FIR滤波器

快速实现基于FPGA的脉动FIR滤波器,VHDL,脉动阵列,PE处理单元,FIR滤波器

评论