在《数字电路之如雷贯耳的“逻辑电路”》、《数字电路之数字集成电路IC》之后,本文是数字电路入门3,将带来「时序电路」的讲解,及其核心部件触发器的工作原理。什么是时序电路?

2016-08-01 10:58:48 19579

19579

时序电路 首先来看两个问题: 1.为什么CPU要用时序电路,时序电路与普通逻辑电路有什么区别。 2.触发器、锁存器以及时钟脉冲对时序电路的作用是什么,它们是如何工作的。 带着这两个问题,我们从头了解

2020-11-20 14:27:09 5120

5120

触发器是由各种基础门电路单元组成,广泛应用于数字电路和计算机中。它具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。 触发器具有两个稳定状态

2023-01-11 17:17:07 13777

13777

触发器是一种特殊的电路元件或信号,它可以根据预先设定的条件或事件来产生相应的输出信号或动作。触发器是数字电路中的基本元件,用于控制信号的时序、逻辑运算和状态转换。

2024-01-15 16:33:15 7829

7829

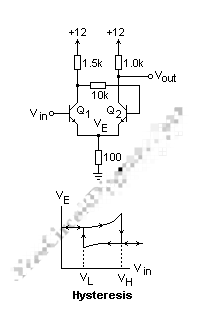

的,因此可以设计成储存电路用来保存信息。常用的存储电路有两类:一类采用电平触发,我们称为锁存器(Latch);另一类通过边沿信号触发,也就是触发器(Flip-flop)。中文译法经常有一种不明觉厉的感觉

2021-07-04 08:00:00

,显然内部结构不是单纯的组合逻辑。内部的功能有一定的记忆性功能,能够清楚的记得之前我们投入的硬币的数量。 时序逻辑电路 = 组合逻辑电路 + 时序逻辑器件(触发器)。 根据输出信号的特点将时序电路划分

2023-02-22 17:00:37

数字电路--触发器原理

2017-02-05 14:20:16

数字电路--触发器双稳态触发器

2017-02-05 14:16:51

数字电路--若干种触发器工作原理

2016-12-26 16:51:00

触发器)3.2.3同步式融发器(边缘触发器)3.3触发器的特性表与特性方程3.3.1R-S触发器3.3.2T触发器(Trigger)3.33D触发器(数字电路-21世纪电子工程师

2008-09-04 23:26:26

数字电路实验指导书一、集成门电路(3)二、TTL集电极开路门与三态输出门的应用 (9)三、加法器 (15)四、数据选择器 (19)五、触发器 (23)六、集成电路计数器、译码和显示 (30)七、移位寄存器 (35)八、集成定时器 (41)九、电子秒表 (47)十、模/数和数/模转换器 (52)

2009-03-16 23:06:45

触发器是构成时序逻辑电路的基本单元电路。

触发器具有记忆功能,能存储一位二进制数码。

2025-03-26 14:21:19

功能。时序电路的特点是:输出不仅取决于当时的输入值,而且还与电路过去的状态有关。它类似于含储能元件的电感或电容的电路,如触发器、锁存器、计数器、移位寄存器、储存器等电路都是时序电路的典型器件。

2021-09-23 10:05:43

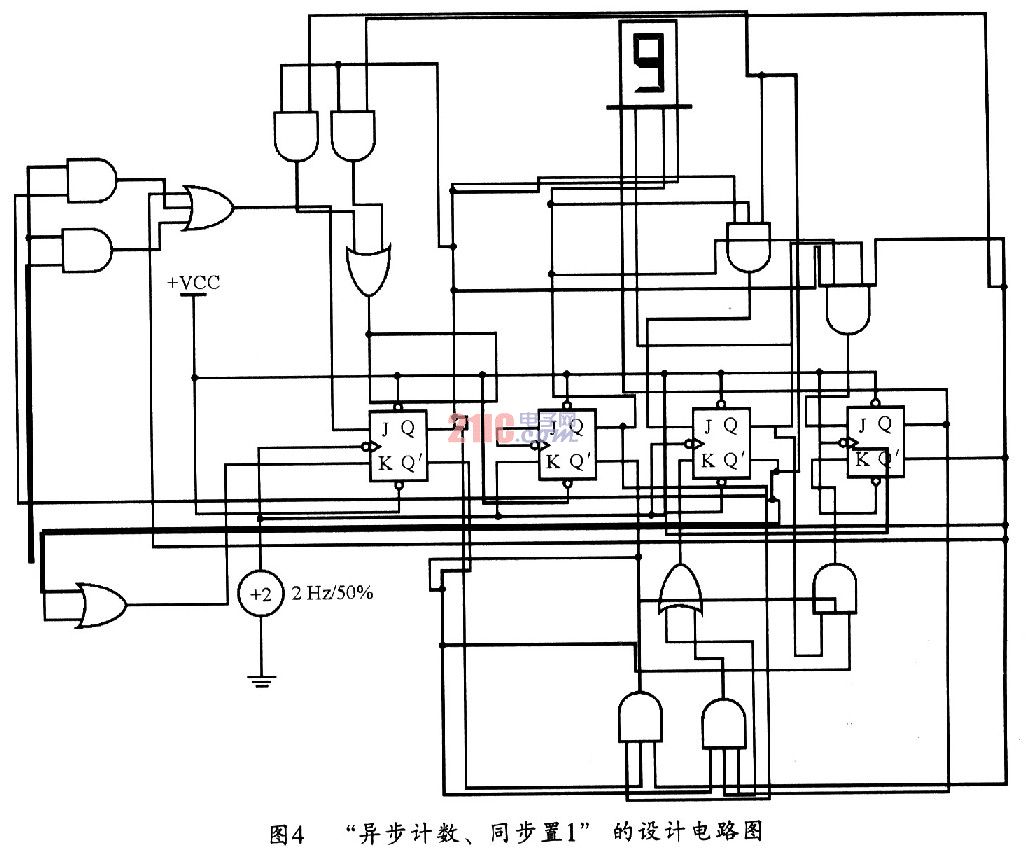

化简→画逻辑电路图。时序电路设计:列原始状态转移图和表→状态优化→状态分配→触发器选型→求解方程式→画逻辑电路图。在实际应用中,数字电路设计的基本思路是先选择标准的通用集成电路,然后,再利用这些芯片

2019-02-27 11:55:00

习时把这一章分为两节,它们分别是:§5、1 时序电路的概述§5、2 触发器 5、1 时序电路的概述 这一节我们来学习一些关于时序电路的概念,在学习时要注意同步时序电路和异步时序电路的区别一:时序电路

2018-08-23 10:36:20

时序电路测试及应用一、实验目的1.掌握常用时序电路分析,设计及测试方法。2.训练独立进行实验的技能.二、实验仪器及材料1.双踪示波器 2.

2009-08-20 18:55:27

逻辑功能,若电路存在问题,并提出改进方法。在分析同步时序电路时分为以下几个步骤:分清时序电路的组成.列出方程. 根据时序电路的组合部分,写出该时电路的输出函数表达式.并确定触发器输入信号的逻辑表达式

2018-08-23 10:28:59

基本元器件和基本电路的性能指标及分析、测试方法及相关的应用技术;3.掌握实验箱及常用仪器的使用;4.锻炼分析、判断、解决实际问题能力【教学内容】完成逻辑门电路、组合逻辑电路、触发器及触发器之间的转换

2009-10-11 09:11:41

《数字电路》课程口袋型FPGA实验板

2021-01-28 06:58:12

; 2.学习用集成数据选择器进行逻辑设计。实验基本内容:模集成数据选择器的逻辑功能及测试方法仪器:数字电路实验台一台,74系列常用芯片,直流电源。实验五:触发器实验

2009-10-11 09:15:33

在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器.由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。由于一个触发器能够存储一位二进制码,所以把n个触发器

2018-10-27 22:38:21

什么是时序电路?时序电路核心部件触发器的工作原理

2021-03-04 06:32:49

什么是时序电路?SRAM是触发器构成的吗?

2021-03-17 06:11:32

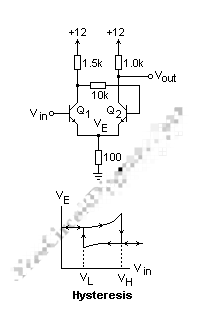

逻辑可构成时序逻辑电路,简称时序电路。现在讨论实现存储功能的两种逻辑单元电路,即锁存器和触发器。双稳态:电子电路中。其双稳态电路的特点是:在没有外来触发信号的作用下,电路始终处于原来的稳定状态。在外

2016-05-21 06:50:08

在Quartus-ii中实现数字电路的仿真一、前期二、门电路设计触发器实验三、直接调用触发器实验四、总结一、前期数字电路用数字信号完成对数字量进行算术运算和逻辑运算的电路称为数字电路,或数字系统。从

2021-07-26 07:12:52

同步时序逻辑电路的设计(仿真实验 2学时)一、 实验目的;1. 掌握时序电路的设计和测试方法。2. 验证二进制计数器的工作原理:学会用集成触发器

2009-10-11 09:09:51

触发器没有使用相同的时钟信号,需要分析哪些触发器时钟有效哪些无效分析步骤和同步时序电路一样,不过要加上时钟信号有关D触发器的例题抄自慕课上的一个题目,注意第二个触发器反相输出端同时连接到复位端JK

2021-09-06 08:20:26

针对数字电路测试诊断需求,以数字电路中较为复杂的时序电路测试为侧重点,将含有CPU、FPGA的数字电路作为测试对象,结合目前常用的时序电路仿真方法,设计了一套基于PXI总线的小型化电路板测试诊断系统

2010-05-13 09:08:39

状态,因此,与标准环形计数器相比,约翰逊计数器仅需要一半数量的触发器便可实现同样的MOD。 典型时序电路的缺陷 如图1所示,这种电路最大的缺点是不可配置,因此,不能改变时钟分频因子。一个N触发器

2018-09-30 16:00:50

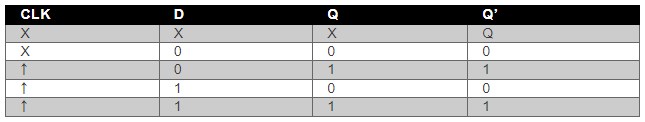

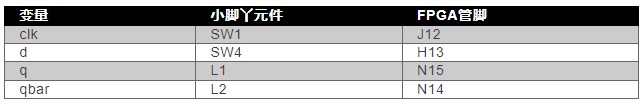

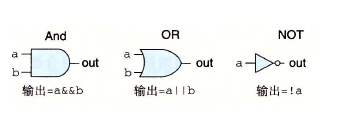

实验二 基本时序电路设计(1)实验目的:熟悉QuartusⅡ的VHDL文本设计过程,学习简单时序电路的设计、仿真和硬件测试。(2)实验内容:Ⅰ.用VHDL设计一个带异步复位的D触发器,并利用

2009-10-11 09:21:16

《计算机系统基础》30’一、处理器的时序电路1、CPU中的时序电路答:CPU中的时序电路:通过RS触发器控制CPU的时序。2、单周期处理器的设计答:CPU在处理指令时,一般需要经过以下几个步骤:1

2021-07-22 09:46:12

计数器及时序电路原理及实验 一、实验目的1、了解时序电路的经典设计方法(D触发器、JK触发器和一般逻辑门组成的时序逻辑电路)。 &

2009-10-10 11:47:02

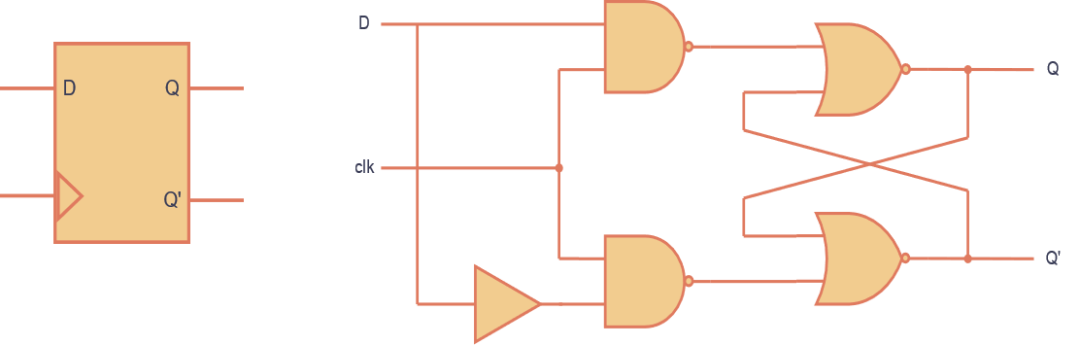

怎样去设计一个基于数字电路的D触发器?如何对基于数字电路的D触发器进行仿真?

2021-09-16 06:45:31

集成触发器、集成计数器及译码显示电路实验目的1. 验证基本RS、D、JK触发器的逻辑功能。2. 了解十进制加法计数器和减法计数器的工作过程。3. 了解计数、译码、显示电路的工作状态。实验原理在数字电路

2008-12-11 23:38:01

同步时序数字电路的分析二进制同步计数器 分析步骤: 1.确定电路是否是同步时序数字电路 2.确定触发器的驱动方程 3.做出状态转换表 4.做出分析结论 BC

2008-10-20 10:10:43 30

30 摘要:针对同步时序电路的初始化问题,提出了一种新的实现方法。当时序电路中有未确定状态的触发器时,就不能顺利完成该电路的测试生成,因此初始化是时序电路测试生成中

2010-05-13 09:36:52 6

6 一、基本要求1、理解R-S触发器、J-K触发器和D触发器的逻辑功能;2、掌握触发器构成的时序电路的分析,并了解其设计方法;3、理解计数器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

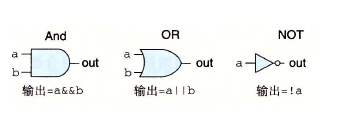

57 组合电路和时序电路是数字电路的两大类。门电路是组合电路的基本单元;触发器是时序电路的基本单元。

2010-08-29 11:29:04 67

67 T触发器,什么是T触发器

在数字电路中,凡在CP时钟脉冲控制下,根据输入信号T取值的不同,具有保持和翻转功能的电路,即当T=0时

2009-09-30 18:26:07 30888

30888

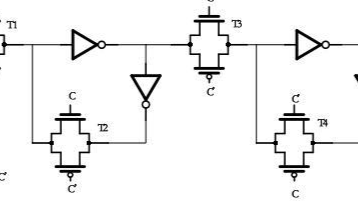

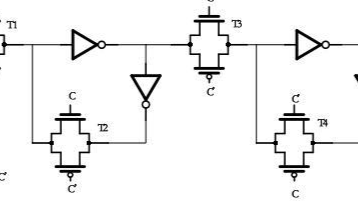

CMOS触发器的结构与工作原理

CMOS D触发器足主-从结构形式的一种边沿触发器,CMOS T型触发器、JK触发器、计数单元、移位单元和各种时序电路都由其组成,因此仪

2009-10-17 08:52:27 7947

7947

同步时序电路

4.2.1 同步时序电路的结构和代数法描述

2010-01-12 13:31:55 5768

5768

触发器是数字电路的基本逻辑单元之一,也是构成各种时序电路的最基本逻辑单元。

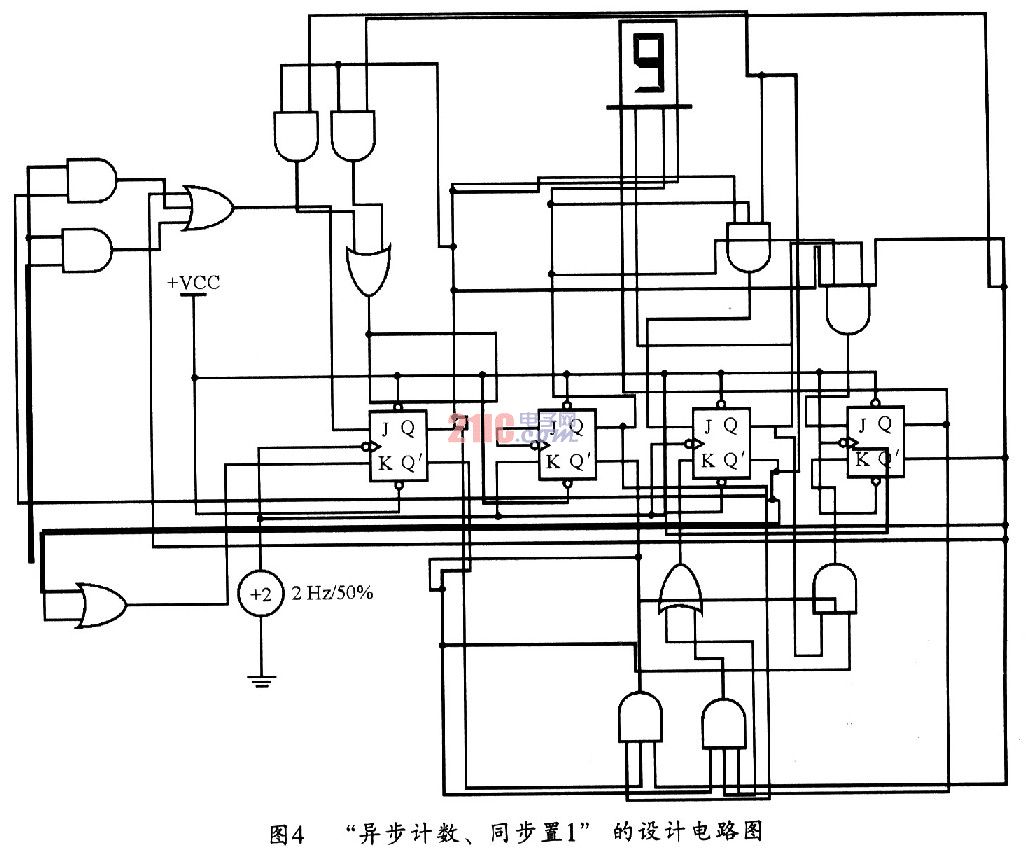

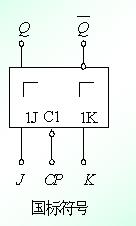

文中给出了基于JK触发器来设计十二归一计数器的设计和实现方法,并通过EWB软件进行了

2010-06-30 15:58:29 18640

18640

本教材是与《数字电子技术基础》配套的实验指导书,共有4章。主要内容包括:数字电路实验基础知识、数字电路实验、计算机辅助实验以及可编程逻辑器伯设计住址实验。教材末配有

2011-04-10 12:28:55 180

180 FPGA设计一个很重要的设计是时序设计,而时序设计的实质就是满足每一个触发器的建立(Setup)/保持(Hold)时间的要求。 建立时间(Setup Time):是指在触发器的时钟信号上升沿到来以前,数据

2011-10-28 10:21:26 92

92 数字电路--触发器原理

2016-12-29 19:03:12 0

0 数字电路--触发器双稳态触发器

2016-12-20 17:32:40 0

0 数字电路--若干种触发器工作原理

2017-01-07 21:08:03 0

0 1、了解时序电路的经典设计方法(D触发器、JK触发器和一般逻辑门组成的时序逻辑电路)。

2、了解同步计数器,异步计数器的使用方法。

3、了解同步计数器通过清零阻塞法和预显数法得到循环任意进制

2022-07-10 14:37:37 17

17 触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即“0”和“1”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

2017-08-19 09:21:00 17038

17038

触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态.

2017-11-02 08:53:42 61658

61658 触发器是一个具有记忆功能的二进制信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即“0”和“1”,,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

2017-11-02 10:20:40 115082

115082

触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即“0”和“1”。

2017-12-12 16:47:56 8214

8214

触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态

2017-12-12 17:20:40 86395

86395

“时钟是时序电路的控制者” 这句话太经典了,可以说是FPGA设计的圣言。FPGA的设计主要是以时序电路为主,因为组合逻辑电路再怎么复杂也变不出太多花样,理解起来也不没太多困难。但是时序电路就不同了

2018-07-21 10:55:37 5151

5151 组合电路和时序电路是计算机原理的基础课,组合电路描述的是单一的函数功能,函数输出只与当前的函数输入相关;时序电路则引入了时间维度,时序电路在通电的情况下,能够保持状态,电路的输出不仅与当前的输入有关,而且与前一时刻的电路状态相关,如我们个人PC中的内存和CPU中的寄存器,均为时序电路。

2018-09-25 09:50:00 25945

25945 ,得到原始状态图. 2.化简原始状态. 在制作原始状态图时,难免会出现多余状态(触发器的个数增多激励电路过于复杂等),因此要进行状态化简,化简时应根据具体情况来考虑. 3.分配化简后的状态. 把化简后的状态用二进制代码来表示称为状态编码.时序电路中,电路

2018-10-31 18:14:01 1681

1681 本文档的主要内容详细介绍的是数字电路教程之触发器课件的详细资料说明主要内容包括了:一 SR锁存器,二 电平触发的触发器,三 脉冲触发的触发器,四 边沿触发的触发器,五 触发器的逻辑功能及其描述方法

2018-12-28 08:00:00 17

17 D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

2019-12-02 07:06:00 8199

8199

异步时序电路是指电路中除以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件;电路中没有统一的时钟;电路状态的改变由外部输入的变化直接引起。

2019-11-29 07:07:00 1637

1637 异步时序电路是指电路中除以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件;电路中没有统一的时钟;电路状态的改变由外部输入的变化直接引起.

2019-11-27 07:04:00 2273

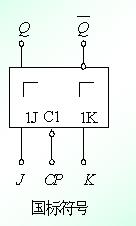

2273 数字时序电路中通常用到的触发器有三种:电平触发器、脉冲触发器和边沿触发器。

2019-07-05 14:38:54 17268

17268

时序电路是数字电路的基本电路,也是FPGA设计中不可缺少的设计模块之一。

2020-09-08 14:21:22 7784

7784

时间的重要性不言而喻,加上时间这个维度就如同X-Y的平面加上了一个Z轴,如同打开了一个新的世界。所以今天我们就要来聊聊时序电路。 在时序电路中,电路任何时刻的稳定状态输出不仅取决于当前的输入,还与前

2021-01-06 17:07:22 5770

5770 电子发烧友网为你提供什么是时序电路?触发器又是怎么回事资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-02 08:41:19 5

5 电子发烧友网为你提供“时序电路”及其核心部件触发器的工作原理资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:51:02 13

13 明德扬有完整的时序约束课程与理论,接下来我们会一章一章以图文结合的形式与大家分享时序约束的知识。要掌握FPGA时序约束,了解D触发器以及FPGA运行原理是必备的前提。今天第一章,我们就从D触发器开始讲起。

2022-07-11 11:33:10 6143

6143

组合逻辑和时序逻辑电路是数字系统设计的奠基石,其中组合电路包括多路复用器、解复用器、编码器、解码器等,而时序电路包括锁存器、触发器、计数器、寄存器等。 在本文中,小编简单介绍关于时序电路的类型和特点等相关内容。

2022-09-12 16:44:00 10673

10673

D 触发器或数据触发器是一种触发器,它只有一个数据输入“D”和一个时钟脉冲输入, 这种触发器也称为延迟触发器,经常用于许多时序电路,如寄存器、计数器等。下面一起来了解一下D触发器不同应用下的电路图。

2023-01-06 14:19:46 9743

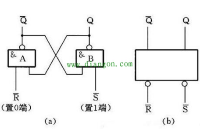

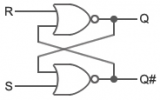

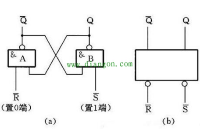

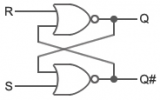

9743 其中R、S分别是英文复位Reset和置位Set的缩写,作为最简单的一种触发器,是构成各种复杂触发器的基础。RS触发器的逻辑电路图如下图所示。

2023-02-08 09:19:45 11327

11327 那么,如何才能将过去的输入状态反映到现在的输出上呢?「时序电路」到底需要些什么呢?人类总是根据过去的经验,决定现在的行动,这时我们需要的就是—记忆。同样,「时序电路」也需要这样的功能。这种能够实现人类记忆功能的元器件就是触发器。

2023-03-24 10:48:58 1943

1943

同步和异步时序电路都是使用反馈来产生下一代输出的时序电路。根据这种反馈的类型,可以区分这两种电路。时序电路的输出取决于当前和过去的输入。时序电路分为同步时序电路和异步时序电路是根据它们的触发器来完成的。

2023-03-25 17:29:52 29287

29287

按结构和功能,触发器可以分为RS型、JK型、D型和T型,在这里,我们只讲解比较有代表性的类型,RS型和D型。

2023-05-22 09:58:43 2417

2417

本文旨在总结近期复习的数字电路D触发器(边沿触发)的内容。

2023-05-22 16:54:29 22343

22343

数字电路是现代电子技术中的重要组成部分,它是由数字信号进行处理和传输的电路系统。数字电路的定义是指由逻辑门和触发器等基本逻辑元件组成的电路,用于处理和传输数字信号。数字电路通过将输入信号转换为离散

2023-07-31 11:46:22 15613

15613 用D触发器设计一个序列发生器 怎么用D触发器做序列信号发生器? 序列发生器是数字电子技术中常用的电路模块之一,它可以用来生成一系列的数字信号序列。在数字电路中,D触发器是一种被广泛使用的数字逻辑组件

2023-08-24 15:50:17 6096

6096 触发器的输出是现态函数 触发器是数字电路中的一种重要元件,它们通常被用于存储和装载二进制数据,也可以用于控制和同步各种数字电路。在许多数字电路应用中,触发器的输出通常被用作输入信号来触发后续电路。在

2023-08-24 15:50:19 1671

1671 触发器(Flip-Flop)是数字电路中的一种时序逻辑元件,用于存储二进制位的状态。它是数字电路设计中的基本构建块之一,常用于存储数据、实现状态机、控制信号的生成等。触发器可以看作是一种特殊

2023-08-31 10:50:19 20343

20343

D触发器,是时序逻辑电路中必备的一个基本单元,学好 D 触发器,是学好时序逻辑电路的前提条件,其重要性不亚于加法器,二者共同构成数字电路组合、时序逻辑的基础。

2023-10-09 17:26:57 6026

6026

建立/保持时间对数字电路的影响 数字电路是指使用数字信号进行连接和处理信息的电路。数字电路是由一系列数字逻辑门和触发器构成的,这些组件可以在特定的输入下产生特定的输出。时间是数字电路中不可忽略的因素

2023-10-29 14:21:46 1380

1380 RS触发器是一种经典的数字逻辑电路元件,用于存储和控制信息流。它是由两个反馈作用的逻辑门组成,常用于时序电路和数据存储。 RS触发器由两个互补的输出Q和~Q组成,其中Q表示触发器的状态为"1",~Q

2023-11-17 16:14:28 4298

4298 RS触发器与SR触发器都是基本的数字逻辑电路元件,常用于存储、控制和时序电路中。

2024-01-29 14:15:08 8676

8676 时序电路是由触发器等时序元件组成的数字电路,用于处理时序信号,实现时序逻辑功能。根据时序元件的类型和组合方式的不同,时序电路可以分为同步时序电路和异步时序电路。本文将从这两个方面详细介绍时序电路,并

2024-02-06 11:22:30 2830

2830 ,时序电路可以分为同步时序电路和异步时序电路。接下来,我们将详细讨论时序电路的分类以及其基本单元电路。 一、同步时序电路 同步时序电路是指所有的时钟信号在整个电路中具有相同的时钟频率和相位。它包括锁存器、触发器

2024-02-06 11:25:21 4239

4239 时序电路基本原理是指电路中的输出信号与输入信号的时间相关性。简单来说,就是电路的输出信号要依赖于其输入信号的顺序和时间间隔。 时序电路由时钟信号、触发器和组合逻辑电路组成。时钟信号是时序电路的重要

2024-02-06 11:30:00 3204

3204 FPGA(现场可编程门阵列)芯片中的触发器是一种重要的存储元件,它在数字电路设计中起着至关重要的作用。触发器的主要功能是存储和同步数字信号,确保电路在正确的时刻捕获和保持信号状态。

2024-03-15 15:20:48 2222

2222 时序电路是数字电子学中的一个核心概念,它利用了触发器或其他记忆元件来存储信息,并根据输入信号和当前状态产生输出。

2024-05-23 15:14:50 4700

4700 在数字电路设计中,触发器和时序逻辑电路是构建复杂数字系统不可或缺的基础元素。触发器(Flip-Flop)作为基本的存储单元,能够存储一位二进制信息,并在特定的时钟信号控制下更新其状态。而时序逻辑电路

2024-07-18 17:43:41 4403

4403 数字电路是现代电子技术的基础,广泛应用于计算机、通信、控制等领域。在数字电路中,触发器是一种重要的存储单元,用于存储和传递信息。然而,在实际应用中,触发器可能会发生空翻现象,影响电路的正常工作

2024-07-23 11:15:35 7127

7127 和保持四种功能,是集成触发器中功能最为齐全的触发器之一。由于其强大的通用性和灵活性,JK触发器被广泛应用于时序电路、频率分析电路、数码集成电路等多种数字电路中,特别是在计算机的寄存器中用于存储二进制信息。

2024-07-27 14:53:31 11270

11270 边沿触发器和脉冲触发器是数字电路中常用的两种触发器,它们在触发方式、触发条件和电路特性等方面存在显著的差异。

2024-07-27 15:03:15 9625

9625 在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的是T触发器(Toggle Flip-Flop)和D触发器(Data Flip-Flop

2024-08-11 09:37:25 6781

6781 双稳态触发器(Bistable Trigger or Flip-Flop)是一种具有两个稳定状态的数字电路元件,广泛应用于数字逻辑电路、存储器和时序电路中。 一、双稳态触发器的基本概念 1.1 定义

2024-08-11 10:00:52 5546

5546 同步触发器和边沿触发器是数字电路中两种常见的触发器类型,它们在触发方式、工作原理、性能特点以及应用场景等方面存在显著的差异。

2024-08-12 11:26:01 3572

3572 在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的有JK触发器、D触发器和T触发器等。 一、触发器的基本概念 1.1 触发器的定义 触发器

2024-08-22 10:33:51 3765

3765 引言 数字电路是现代电子技术的基础,广泛应用于计算机、通信、控制等领域。触发器是数字电路中的一种基本逻辑元件,具有存储和传递信息的功能。 触发器的基本概念 触发器是一种具有记忆功能的数字电路元件

2024-08-22 10:37:33 5059

5059 JK触发器是一种具有两个稳态的数字逻辑电路,广泛应用于数字电路设计中。 引言 在数字电路设计中,触发器是一种非常重要的基本逻辑元件。触发器可以存储一位二进制信息,即0或1。根据触发条件的不同,触发器

2024-08-22 10:39:18 2766

2766 触发器在数字电路中的作用是极其重要且多方面的。作为一种具有记忆功能的电路元件,触发器能够存储一位二进制信息(即0或1),并根据输入信号和时钟信号的变化,在不同状态之间切换,从而实现各种复杂的数字逻辑功能。

2024-08-30 10:46:21 3345

3345

电子发烧友App

电子发烧友App

评论