时序电路是数字电路的基本电路,也是FPGA设计中不可缺少的设计模块之一。时序电路与组合电路最大的不同点是:时序电路的输出不仅与输人有关,还与电路本身的状态有关,即时序电路有记忆功能。大部分时序电路还有一个特征,就是有时钟驱动,电路的各个状态在时钟节拍下变化。本章主要介绍时序电路的一些基本组件及一些简单的时序逻辑电路应用实例。

13.1D触发器建模

【D触发器建模】

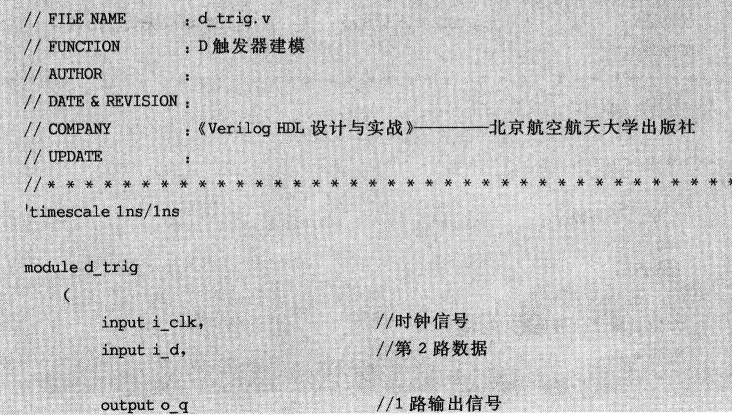

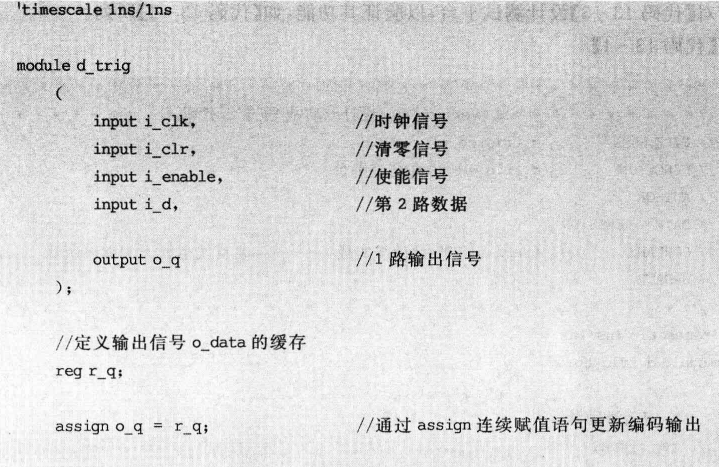

D触发器是时序电路最基本的组件之一,其基本功能是:输出端Q的更新只发生在时钟信号的上升沿(也可以是下降沿,在没有其他说明的情况下,例子中取上升沿)时刻,更新为此时输人端D的信号。D触发器的Verilog HDL编码的实现比较简单,具体实现如【代码13-1】所列。

【代码13-1】

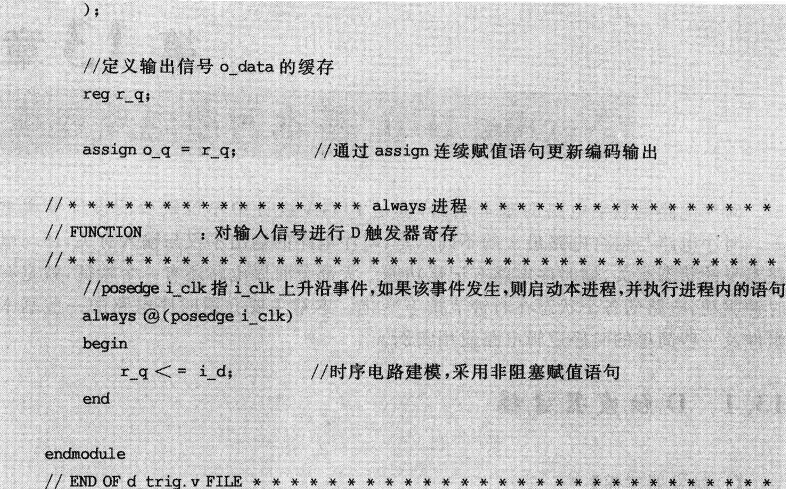

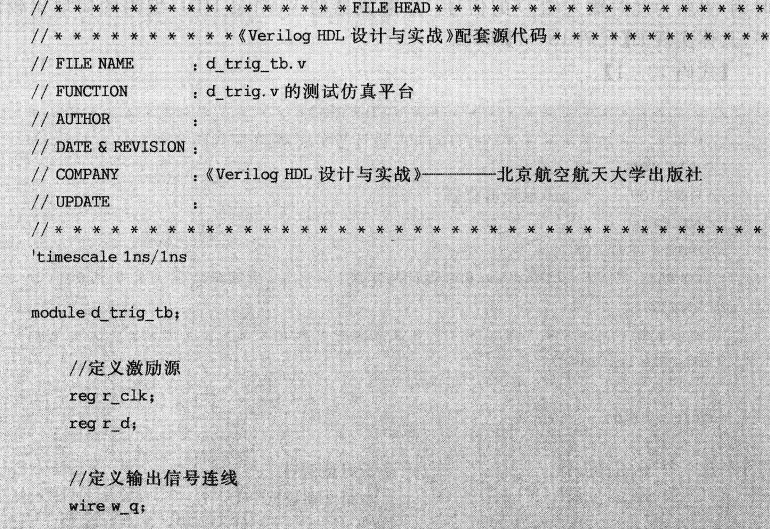

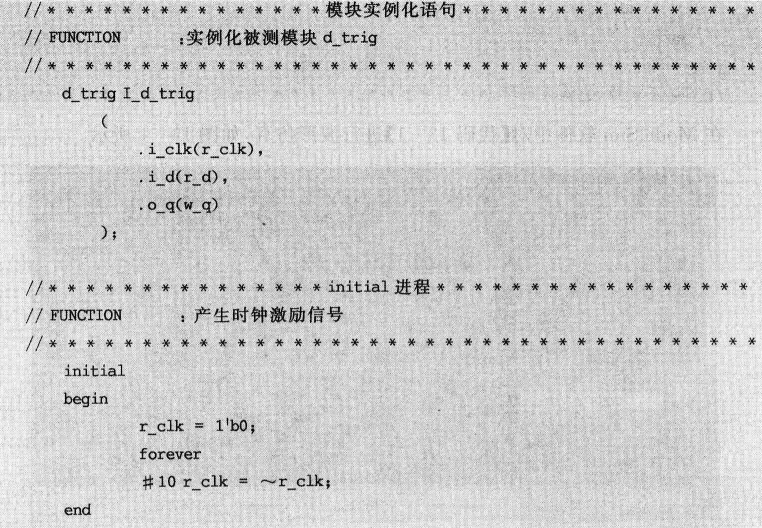

编写【代码13-1】的测试平台如【代码13-2】所列。

【代码13-2】

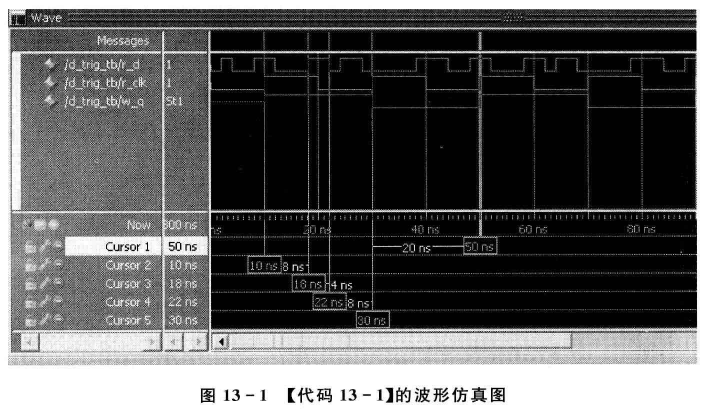

在ModelSim软件中对【代码13-1】进行波形仿真,如图13-1所示。

波形仿真报告分析

从图13-1可以看出,在10ns时刻以前,由于时钟信号的上升沿还没有到来过,所以w_q的值没有被更新过,为x;在10ns时刻,在时钟信号的,上升沿事件发生,w_q更新为此刻的r_d,值为1,该值会一直保持到时钟信号的下一个上升沿事件发生时;在10ns时刻,虽然r_d的值发生了变化,但由于不是发生在时钟信号的上升沿时刻,所以w_q的值并没有发生变化。以上对波形的分析符合D触发器的功能特点。

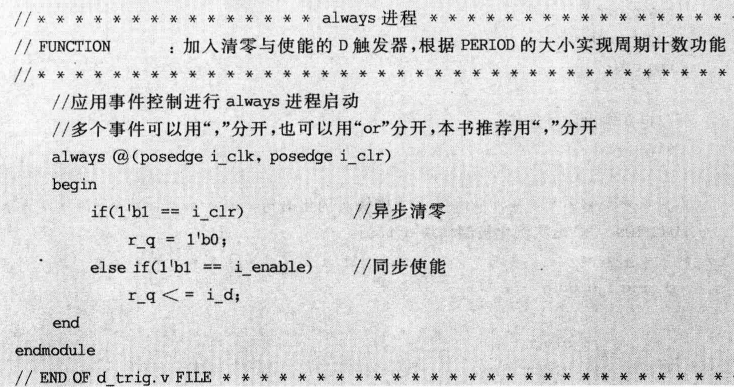

此外,还可以对【代码13-1】的D触发器加入一些控制信号,如清零信号、使能信号,具体实现如【代码13-3】所列。

【代码13-3】

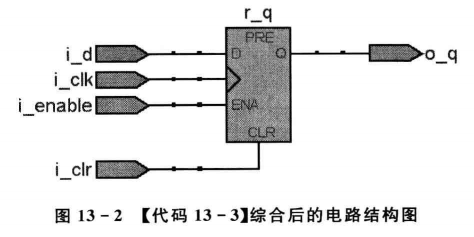

【代码13-3】在Quartus II软件中综合后的电路结构如图13-2所示。

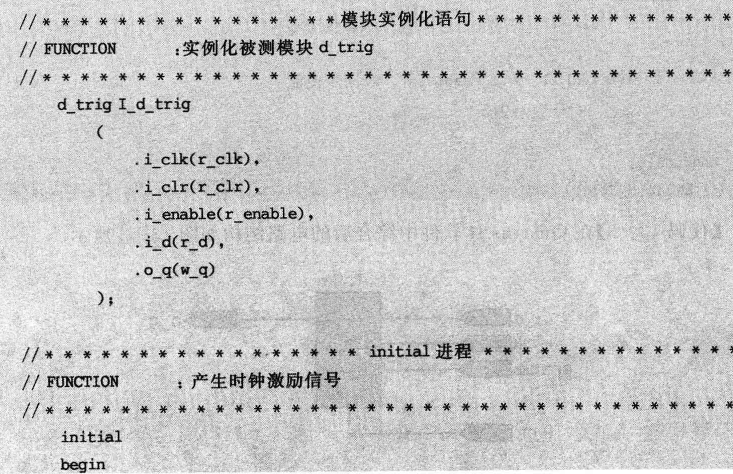

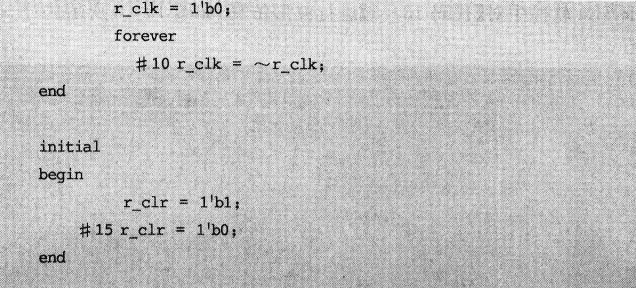

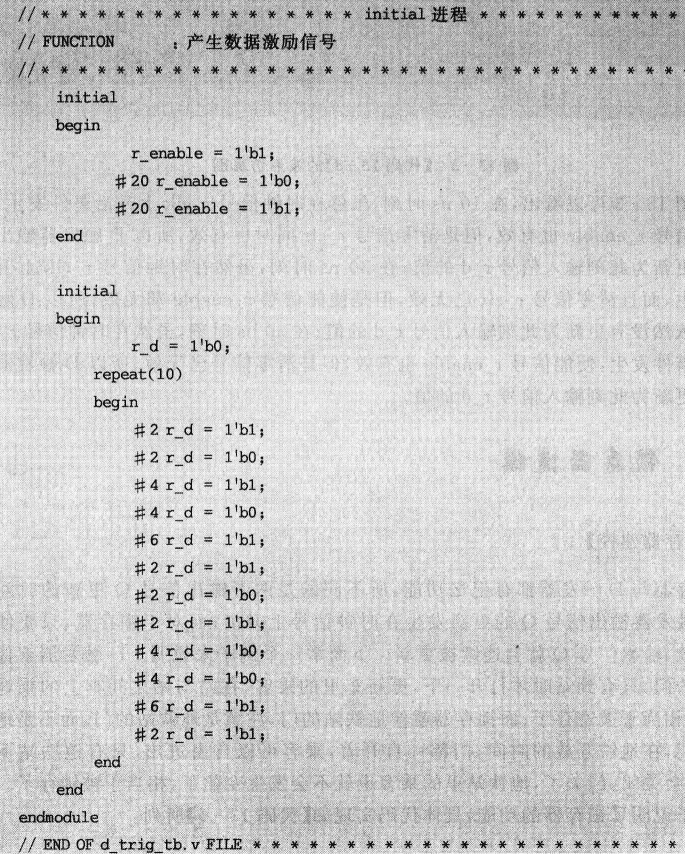

对【代码13-3】设计测试平台,以验证其功能,如【代码13-4】所列。

【代码13-4】

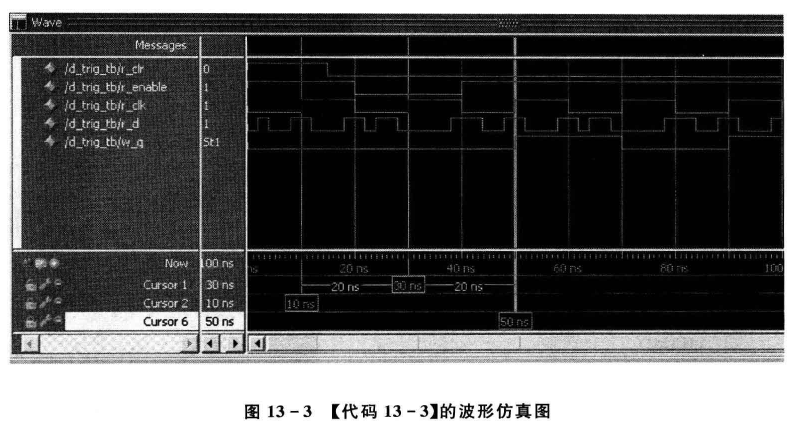

在ModelSim软件中对【代码13-3】进行波形仿真,如图13-3所示。

从图13-3可以看出,在10ns时刻,虽然在时钟信号r_clk上升沿事件发生,而且使能信号r_enable也有效,但是清零信号r_clr同时也有效,所以D触发器输出依然没有更新为此刻输入信号r_d的值;在30ns时刻,虽然在时钟信号r_clk上升沿事件发生,而且清零信号r_clr已无效,但是使能信号r_enable却无效,所以D触发器输出依然没有更新为此刻输入信号r_d的值;在50ns时刻,虽然在时钟信号r_clk上升沿事件发生,使能信号r_enable也有效,但是清零信号已无效,所以D触发器输出立即更新为此刻输入信号r_d的值。

除此之外,有关Verilog HDL基本时序电路建模方面,还包括了锁存器建模、JK触发器建模等。想学习更多Verilog HDL建模、时序与整合电路方面的知识,可以下载编者为大家精选准备的一份FPGA学习指南合集:Verilog HDL那些事儿(建模篇,时序篇,整合篇)

Verilog HDL那些事儿建模篇:

在众多的Verilog HDL 参考书,隐隐约约会会出现这样的一个“建模”。建模在Verilog HDL的世界里是一个重要的基础,很多初学Verilog HDL + FPGA 的朋友会成为徘徊在边缘的一群,主要原因就是他们没有掌握好建模技巧,而形成他们继续前进的一大阻碍。在这里笔者将自己养成的建模技巧,编辑成为一本笔记,好让许更多初学的朋友越过这一段学习的大障碍。

Verilog HDL那些事儿时序篇:

建模不是Verilog HDL 语言的所有,建模只是使用Verilog HDL 语言建立一个“像模像样”的“形状”而已。这个“形状”实际上是很粗糙的,还没有经过任何深入的分析。但是我们不可以小看这个“粗糙的形状”,如果没有这个“粗糙的形状”模块的设计根本无法完成。笔者在《Verilog HDL 那些事儿-建模篇》的结束语中有这样讲过:“建模是一个粗糙的东西,它还可以继续细化”。

“细化”顾名思义就是进入模块的深层进行分析和优化(如果有需要调试的话)的工作。但是前提,我们必须“更深入Verilog HDL 语言的世界”才能有效的“细化”模块。这一本起名为《Verilog HDL 那些事儿-时序篇》的笔记分别有两个部分,上半部分和下半部分。上半部分是“步骤和时钟”;下半部分是“综合和仿真”。

Verilog HDL那些事儿整合篇:

要在Verilog 要实现for 和while 等循环是一个矛盾的作业,这话何说呢?首先我们可以用Verilog 来模仿for 和while 等循环,这也是第一章的重点。可是随着我们深入了解Verilog 各种不同的运行模式,模仿就会失去意义。.. 因为只要有一个指向步骤的i 再加上一些整合的技巧,怎么样的循环我们都可以实现,这也是第五章的重点。当然整合篇所讨论的内容不单是循环而已,整合篇的第二个重点是理想时序和物理时序的整合。说实话,笔者自身也认为要结合“两个时序”是一件苦差事,理想时序是Verilog的行为,物理时序则是硬件的行为。不过在它们两者之间又有微妙的“黏糊点”,只要稍微利用一下这个“黏糊点”我们就可以非常轻松的写出符合“两个时序”的模块,但是前提条件是充足了解“理想时序”。

整合篇里还有一个重点,那就是“精密控时”。实现“精密控时”最笨的方法是被动式的设计方法,亦即一边仿真,一边估算时钟的控制精度。这显然是非常“传统”而且“古老”的方法,虽然有效但往往就是最费精神和时间的。相反的,主动式是一种讲求在代码上和想象上实现“精密控时”的设计方法。主动式的设计方法是基于“理想时序”“建模技巧”和“仿顺序操作”作为后盾的整合技巧。不说笔者吹牛,如果采用主动式的设计方法驱动IIC 和SDRAM 硬件,任何一段代码都是如此合情合理。

-

逻辑电路

+关注

关注

13文章

503浏览量

43836 -

时序电路

+关注

关注

1文章

114浏览量

22186

原文标题:FPGA设计应用实例—Verilog HDL基本时序电路建模

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

时序逻辑电路设计

时序逻辑电路的分析和设计

数字电路基础教程之时序逻辑电路的详细资料概述

时序电路基本组件及时序逻辑电路应用实例

时序电路基本组件及时序逻辑电路应用实例

评论