时钟使能和同步设置的D触发器 •FDRE:具有时钟使能和同步复位的D触发器 Register with Rising-Edge Coding Example (Verilog) // 8-bit Register with //

2020-12-13 10:29:00 4344

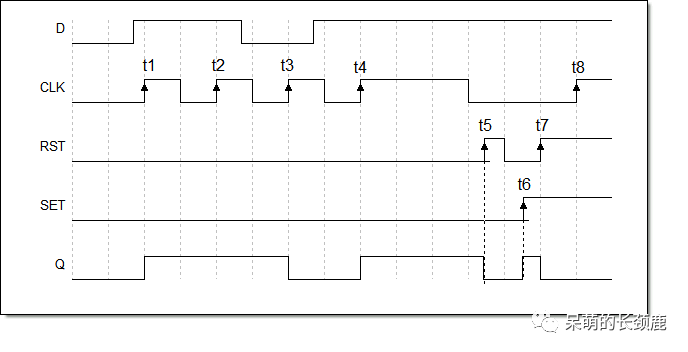

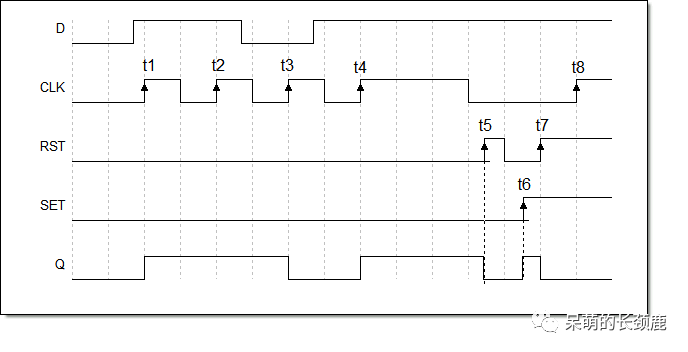

4344 FF_DRE是一个具有异步设置(SET)和重置(RST)输入的边缘触发的D触发器(D Flip-Flop)

2023-12-04 15:47:45 1825

1825

,呵呵。。。上半年,由于Boss项目,学习了FPGA,学的有点急,也断断续续的,才过几个月,似乎知识已经远去,打开电脑,速览以前的资料,记忆又回来了。。。简单记录下这道题,权当回忆。。。//基本D触发器

2012-02-22 13:54:40

做了一个仿真:key_in作为D触发器的输入,led_out作为触发器输出,时钟周期20ns,key_in每10ns随机变化一次,这样的设置下,key_in信号的变化沿有时会和时钟上升沿重合,根据

2022-01-25 22:41:02

新手,verilog描述异步置0,异步置1功能的D触发器,置0低电平有效,置1高电平有效,用modelsim仿真时,个别时序存在问题,费解,请指出问题所在。谢谢。代码及仿真图形如下:module

2014-04-04 20:55:20

触发器实验1)熟悉常用触发器的逻辑功能及测试方法。2)了解触发器逻辑功能的转换。三.实验内容及步骤 (1) 基本RS触发器逻辑功能测试(2) JK触发器逻辑功能测试(3) D触发器逻辑功能的测试

2009-03-20 10:01:05

D触发器在FPGA里面用verilog代码怎么描述呢?其实就是这样的代码,可以看出来,这个代码跟这个D触发器是完全一样的,描述的就是D触发器。怎么讲,可以分析一下这个代码:1····总是(always

2018-09-20 15:09:45

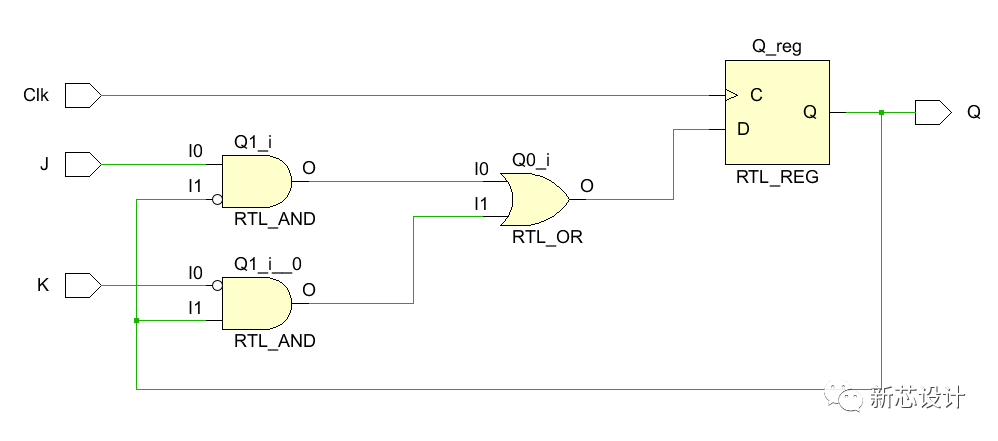

如图, 将j-k触发器用D触发器代替,刚入门 求教

2014-01-09 20:56:31

jk触发器设计d触发器,根据原理图实现模8加1计数器,来源于西电慕课貌似这个软件只有5.0和5.12两个版本。在win10下拖曳器件会发生残影的现象,而且无法修改连线。虽然有自动连线功能但感觉线连

2021-07-22 08:39:47

求助谁能教设计一个D触发器

2014-12-24 22:54:35

D触发器在FPGA里面用verilog代码怎么描述呢?其实就是这样的代码,可以看出来,这个代码跟这个D触发器是完全一样的,描述的就是D触发器。怎么讲,可以分析一下这个代码:1····总是(always

2017-06-20 09:56:47

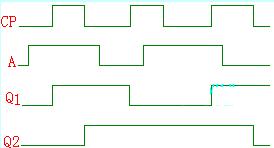

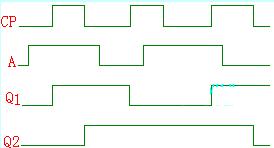

`如图所示,图中第一个触发器D接第二个触发器的非Q端,这个时序图,整不明白啊,我的看法是:当第一个时钟信号高电平来的时候,第一个触发器的输出状态Q是不能判断的啊,因为D接在第二个触发器的非Q端。求大佬指点一下 这个图,是如何工作的?`

2019-01-16 11:50:35

会改变状态,并且不会在时钟转换发生之前在其输出上存储任何数据。换句话说,输出被“锁存”为逻辑“ 0”或逻辑“ 1”。D型触发器的真值表Clkd问问描述↓»0X问问记忆不变↑»1001个重设Q»0

2021-02-03 08:00:00

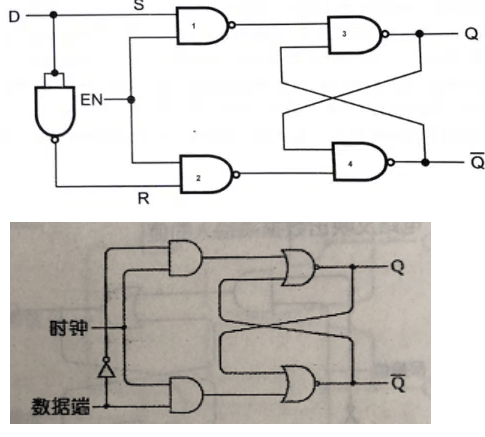

1、在FPGA中使用门级结构设计D触发器的思路一个逻辑电路是由许多逻辑门和开关组成的,因此用基本逻辑门的模型来描述逻辑电路结构是最直观的。本实验设计使用结构描述语句实现D触发器功能,采用带异步置位

2022-07-04 16:01:57

Verilog模型有哪几种?Verilog HDL模型是由哪些模块构成的?如何用Verilog HDL语言描述D型主从触发器模块?

2021-10-19 08:36:32

单片机内部有大量寄存器, 寄存器是一种能够存储数据的电路, 由触发器构成。1.触发器触发器是一种具有记忆存储功能的电路, 由门电路组成。 常见的触发器包括: RS 触发器、 D 触发器和 JK触发器

2022-01-20 07:13:51

你好,我是verilog /逻辑设计的新手。我不确定问题属于哪里,如果不是,请告诉我,谢谢我想用D触发器构建一个3位计数器我在阅读了“逻辑设计的基本原理(Charles H. Roth)”一书后写了

2019-02-14 06:13:32

D触发器在FPGA里面用verilog代码怎么描述呢?其实就是这样的代码,可以看出来,这个代码跟这个D触发器是完全一样的,描述的就是D触发器。怎么讲,可以分析一下这个代码:1····总是(always

2019-01-17 17:24:19

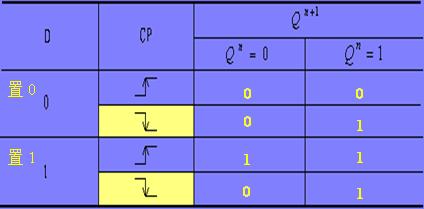

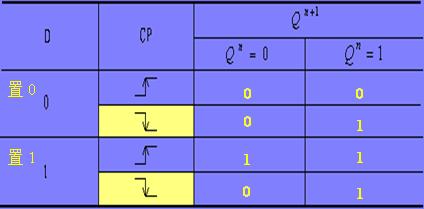

重新点亮。 7、接下来由于U1D已经处于锁定状态,输出端11脚的电平不再发生变化,D触发器也处于锁定状态,输出维持高电平。发光二极管维持导通。 注意: 本例属于数字电路的分析,分析过程比较简单,但是用文字描述比较繁琐,有发现描述错误的地方,还请指正。原作者:电子懒人

2023-03-20 15:33:48

使用带同步清零端的D触发器(清零高电平有效,在时钟下降沿执行清零操作)设计下一个下降沿触发的D触发器,只能使用行为语。使用设计出的D触发器输出一个周期为10个时间单位的时钟信号。下面是网上的答案

2015-07-30 21:01:49

请问触发器的描述方法有哪几种?

2021-04-22 06:02:53

电平触发的D触发器型号有哪些?大部分都是边沿触发的,现在要用到电平触发器,不知道具体型号没法买到

2019-02-28 14:32:13

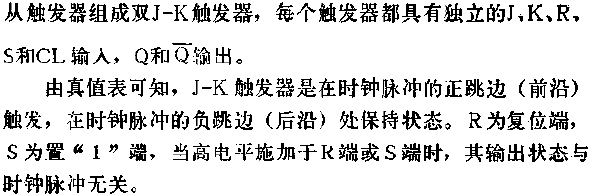

一、实验目的1、掌握基本RS、JK、D和T触发器的逻辑功能2、掌握集成触发器的逻辑功能及使用方法3、熟悉触发器之间相互转换的方法二、实验原理触发器具有两个稳

2008-12-19 00:40:23 49

49 D触发器的功能测试74LS74型双D触发器芯片引脚图,D触发器功能测试的引脚连线图,D触发器功能测试的引脚连线图,用D触发器构成二进制计数器,用D触发器构成四位移位寄存器

J-K

2009-02-14 15:27:51 0

0 D触发器的制作及电路图

2009-05-19 09:35:49 33

33 40174 CMOS 六D触发器:

2009-08-08 11:32:28 46

46 1、掌握锁存器、触发器的电路结构和工作原理;

2、熟练掌握SR触发器、JK触发器、D触发器及T 触发器的逻辑功能;

3、正确理解锁存器、触发器的动态特性

2010-08-18 16:39:35 0

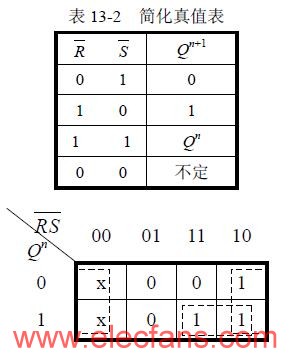

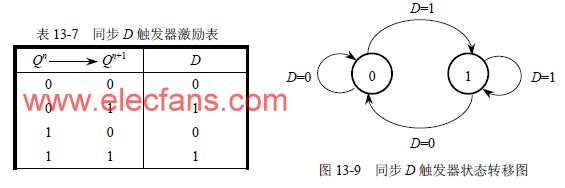

0 触发器是时序逻辑电路的基本构成单元,按功能不同可分为 RS 触发器、 JK 触发器、 D 触发器及 T 触发器四种,其功能的描述可以使用功能真值表、激励表、状态图及特性方程。

2010-09-30 16:03:26 90

90 CD4013 双D触发器 *CD4027 双JK触发器 *CD4042 四锁存D型触发器 *CD4043

2006-04-17 21:18:32 4131

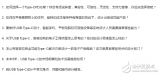

4131 D触发器真值表分析:

1. D 触发器真值表

Dn

2007-09-11 23:15:20 20330

20330 d触发器芯片有:

74HC74 74LS90 双D触发器74LS74

74LS364八D触发器(三态)

2008-01-22 12:42:33 51207

51207

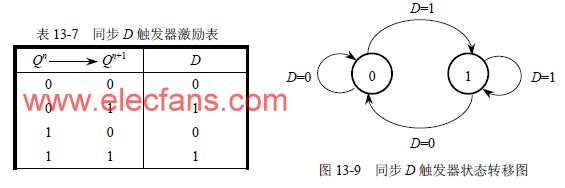

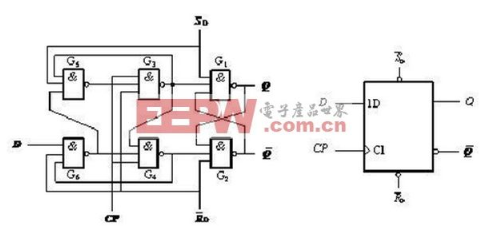

D触发器

同步式D触发器逻辑电路图

D触发器功能

2008-10-20 09:57:54 2818

2818

同步式D触发器逻辑电路图

2008-10-20 09:58:19 9218

9218

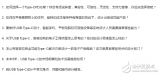

D触发器逻辑功能表

同

2009-03-18 20:13:59 48810

48810

D触发器电路图

2009-05-08 14:26:44 4008

4008

D触发器构成的定时电路图

2009-05-08 15:15:26 4564

4564

D触发器实现二分频电路(D触发器构成的2分频电路)&

2009-06-12 13:58:56 81145

81145

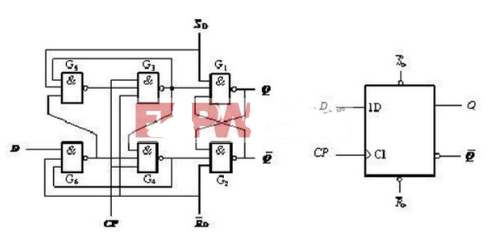

维持阻塞D触发器

(a) 逻辑电路 &

2009-09-30 18:23:59 20961

20961

CMOS触发器的结构与工作原理

CMOS D触发器足主-从结构形式的一种边沿触发器,CMOS T型触发器、JK触发器、计数单元、移位单元和各种时序电路都由其组成,因此仪

2009-10-17 08:52:27 7947

7947

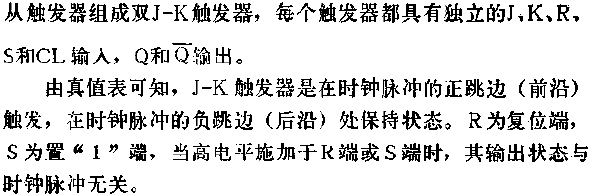

JK触发器,JK触发器是什么意思

1.主从JK触发器主从结构触发器也可以彻底解决直接控制,防止空翻。这里以性能优良、广泛使用的主从JK触发器为

2010-03-08 13:36:29 7474

7474 D触发器,D触发器是什么意思

边沿D 触发器: 电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高

2010-03-08 13:53:13 5322

5322 D触发器工作原理是什么?

边沿D 触发器:

负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出

2010-03-08 13:56:50 70741

70741

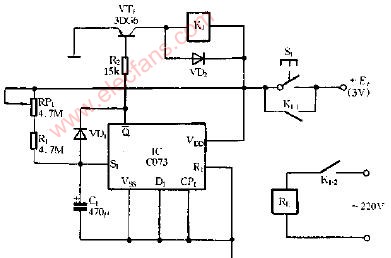

什么是RS触发器,RS触发器的工作原理是什么?

主从RS触发器

2010-03-08 14:00:11 32076

32076 施密特触发器,施密特触发器是什么意思

施密特触发器也有两个稳定状态,但与一般触发器不同的是,施密特触发器采用电位触发

2010-03-08 14:14:56 2290

2290 描述触发器的逻辑功能,通常采用下面三种方法:1.状态转移真值表为了表明触发器在输入信号作用下,

2010-08-13 09:21:35 6700

6700

为了避免同步RS触发器的输入信号同时为1,可以在S和R之间接一个“非门”,信号只从S端输入,并将S端改称为数据输入端D,如图15-8所示。这种单输入的触发器称为

2010-08-18 09:06:00 13148

13148

触发器的相互转换 基本触发器之间是可以互相转换的,JK触发器和D触发器是两种最常用的触发器,别的触发器可以通过这两种触发器转化得来,它们

2010-09-18 08:56:19 5057

5057

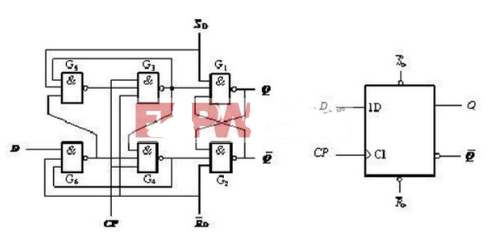

图中所示是用CMOS电路D触发器组成T型触发器和J-K触发器线路。图示线路将D触发器的Q端与D端相连,就可组成T

2010-09-20 03:31:35 21923

21923

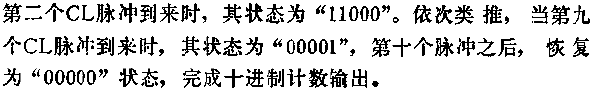

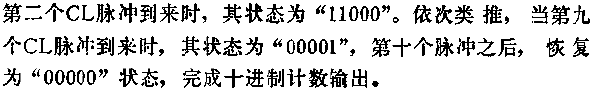

图中所示是用CMOS电路D触发器组成的十进制环形计数器.图中先将D触发器拼成移位寄存器,然后把最后一级D触发器

2010-09-20 23:46:58 20369

20369

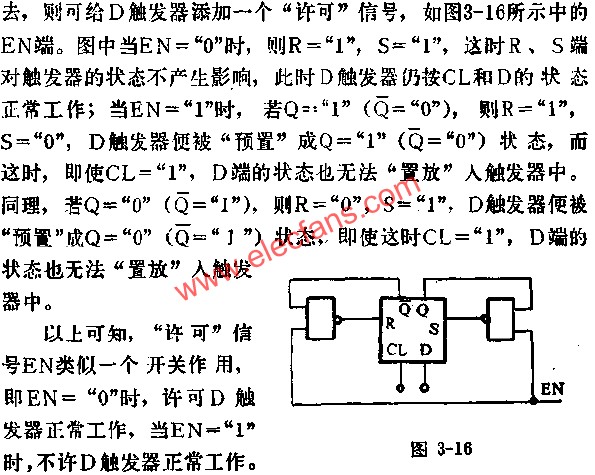

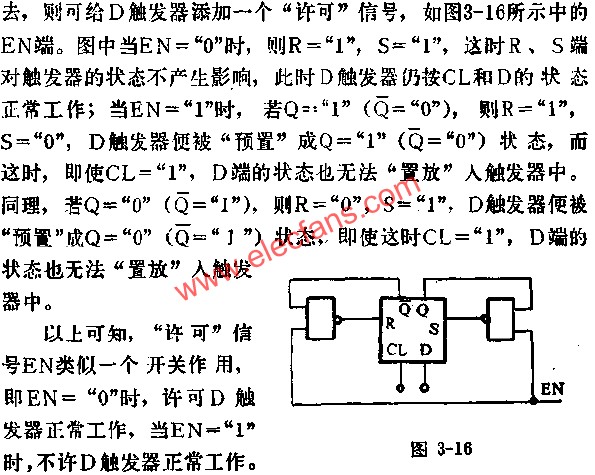

从D触发器的真值表可知,当时钟脉冲CL="1"时,数据输入端D的状态会被“置放”入触发器中去,而与触发器原状无关。如果当时钟冲CL="1",D端状态不旋转放入

2010-09-21 01:27:59 780

780

J-K触发器是一种多功能触发器,它既具有R-S触发器的功能,又具有D触发器和T触发器的功能,因此使用十分灵活

2010-09-24 00:12:06 1641

1641

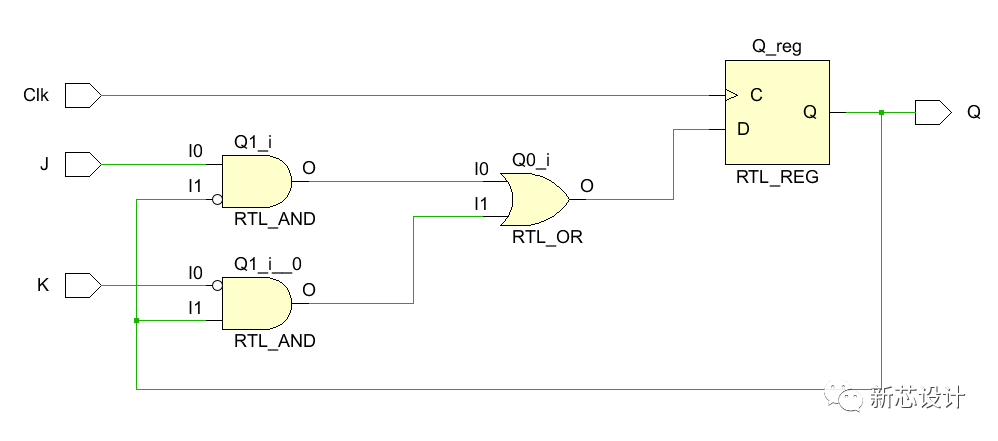

图中所示是用J-K触发器组成的D触发器电路。

从J-K触发器的逻辑图已知在D触发器端增

2010-09-24 00:21:27 8886

8886

用一对互补的输入信号送入RS 触发器,就得到单输入的 D 触发器。由于D 触发器有一对互补信号接至RS 触发器的 输入端,所以它避免了RS 输入端同时为1 的不允许工作状 态。D 触发器通常用来暂时存储一个比特的信息或用作时延 器件。当CLOCK=1 时,触发器能把输

2011-03-09 16:20:01 92

92 1、掌握触发器功能的测试方法。

2、掌握基本RS触发器的组成及工作原理。

3、掌握集成JK触发器和D触发器的逻辑功能及触发方式。

4、掌握几种主要触发器之间相互转换的方法。

5、通过实验、体会CPLD芯片的高集成度和多I\O口。

2022-07-10 14:39:58 18

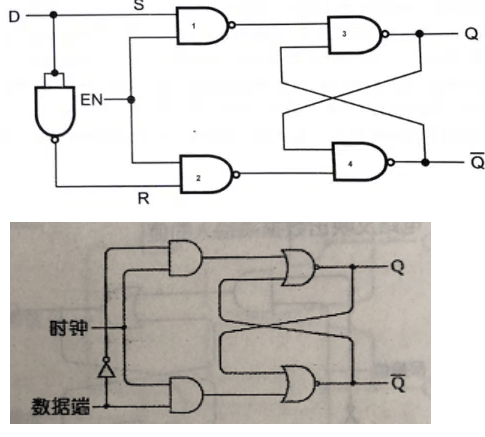

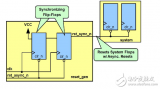

18 D触发器(data flip-flop或delay flip-flop)由6个与非门组成,其中G1和G2构成基本RS触发器。电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

2017-11-02 09:59:08 103266

103266

在带有复位端的D触发器中,当reset信号“复位”有效时,它可以直接驱动最后一级的与非门,令Q端“异步”置位为“1”or“0”。这就是异步复位。当这个复位信号release时,Q的输出由前一级的内部输出决定。

2017-11-30 09:15:37 12892

12892

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2017-12-25 17:30:03 192487

192487

边沿触发器,指的是接收时钟脉冲CP 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CP=l 及CP=0 期间以及CP非约定跳变到来时,触发器不接收数据的触发器。具有下列特点的触发器称为边沿触发方式触发器,简称边沿触发器。

2018-01-31 09:02:33 73165

73165

本文开始介绍了什么是单稳态触发器以及单稳态触发器的电路组成,其次阐述了单稳态触发器特点、门电路构成的单稳态触发器、D触发器构成的单稳态触发器,最后详细的阐述了时基电路构成的单稳态触发器。

2018-03-27 09:24:23 78858

78858

本文开始介绍了触发器的定义和触发器的特点,其次阐述了触发器的分类和触发器的作用,最后介绍了触发器的工作原理。

2018-03-27 17:35:52 22379

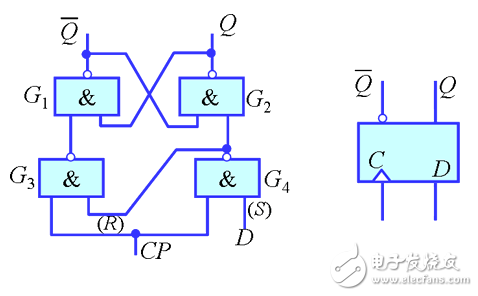

22379 负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。

2019-07-12 08:50:36 102655

102655

CP=1时,门。。打开,门。。被封锁,从触发器保持原来状态不变,D信号进入主触发器。但是要特别注意,这时主触发器只跟随而不锁存,即。。跟随D变化,D怎么变。。也随之怎么变。

2019-07-15 08:57:32 56238

56238

触发器是一个具有异步复位异步置数的器件,那么怎么样Verilog来具体描述这个器件呢,接下来我们就来看一下,

2019-07-26 10:17:16 27983

27983

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2019-11-08 14:48:44 96919

96919

在分析维持-阻塞边沿D触发器的工作原理之前,让我们先来看看 R0的复位功能 、S0的置位功能是如何实现的吧。

2020-10-18 11:26:31 26555

26555

脉冲触发器由两个相同的电平触发的SR触发器组成,其中左SR触发器成为主触发器,右手侧称为从触发器。

2021-02-11 10:56:00 10760

10760

74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入( )复位输入( )、时钟输入(CP)和数据输出(Q)。 的低电平使输出预置或清除,而与其它输入端的电平无关。当

2021-06-04 15:40:41 94565

94565

上图是用与非门实现的D触发器的逻辑结构图,CP是时钟信号输入端,S和R分别是置位和清零信号,低有效; D是信号输入端,Q信号输出端;

2022-09-19 15:22:24 6647

6647 D触发器也称为“延迟触发器”或“数据触发器”,主要用于存储1位二进制数据,是数字电子产品中广泛使用的触发器之一。除了作为数字系统中的基本存储元件外,D触发器也被视为延迟线元件和零阶保持元件。

2022-10-11 17:21:02 175910

175910

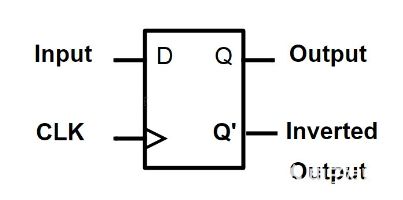

D 触发器或数据触发器是一种触发器,它只有一个数据输入“D”和一个时钟脉冲输入, 这种触发器也称为延迟触发器,经常用于许多时序电路,如寄存器、计数器等。下面一起来了解一下D触发器不同应用下的电路图。

2023-01-06 14:19:46 9744

9744 双D型触发器-HEF4013B

2023-02-15 18:49:50 2

2 本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D触发器与亚稳态的那些事。

2023-05-12 16:37:31 2934

2934

本文旨在总结近期复习的数字电路D触发器(边沿触发)的内容。

2023-05-22 16:54:29 22344

22344

锁存器和触发器有时组合在一起,因为它们都可以在其输出上存储一位(1或0)。与锁存器相比,触发器是需要时钟信号(Clk)的同步电路。D 触发器仅在时钟从

2023-06-29 11:50:18 51321

51321

用D触发器设计一个序列发生器 怎么用D触发器做序列信号发生器? 序列发生器是数字电子技术中常用的电路模块之一,它可以用来生成一系列的数字信号序列。在数字电路中,D触发器是一种被广泛使用的数字逻辑组件

2023-08-24 15:50:17 6096

6096 文章中,我们将详细探讨触发器的输出状态如何被决定的。 1. 异步触发器 异步触发器是一种最简单的触发器类型。它包括SR触发器和D触发器。SR触发器由两个输入引脚“S”和“R”组成,D触发器只有一个输入引脚“D”。 SR触发器有四

2023-08-24 15:50:23 3995

3995 的存储单元,具有时钟同步的特性。其中,D触发器是数字电路设计中使用最广泛的一种触发器类型之一,因为它具有简单、稳定和多功能等优点。

2023-08-31 10:50:19 20344

20344

由于RS触发器实现方式的不同,对输入信号抖动(即短时间内多次变化)的响应也不同。原始的电路设计可能导致RS触发器对输入信号的抖动比较敏感。

2023-09-07 15:47:45 7895

7895 JK 触发器的 Verilog 代码实现和 RTL 电路实现

2023-10-09 17:29:34 6643

6643

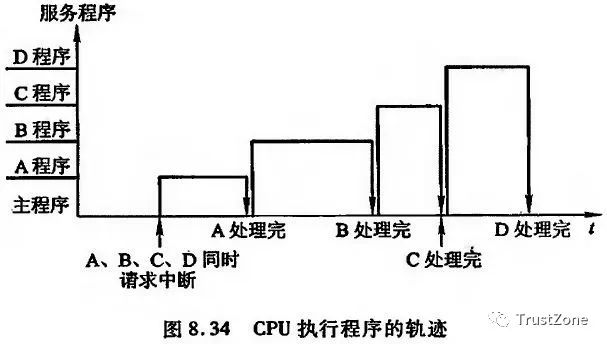

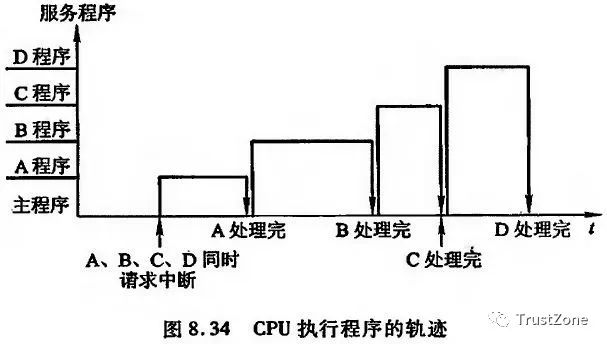

•1)屏蔽触发器和屏蔽字:程序中断接口电路中,完成触发器D,中断请求触发器INTR和屏蔽触发器MASK。 在程序中断接口电路中,有三个重要的组成部分:完成触发器D,中断请求触发器INTR和屏蔽触发器

2023-10-30 17:02:05 2731

2731

D触发器(D flip-flop)可以存储一位二进制数据的状态,因此具有记忆功能。D触发器通常用于数字电路中,用于实现寄存器、计数器等电路,可以通过时钟信号进行同步操作,使它们可以存储和操作二进制数据。值得注意的是,D触发器只能存储一位二进制数据,如果要存储更多的数据,则需要使用多位寄存器。

2023-11-29 14:52:03 6217

6217

不同类型的触发器可能有不同的执行顺序。例如,对于同一个表上的多个触发器,插入触发器(INSERT trigger)可能先于更新触发器(UPDATE trigger)执行。

2024-02-05 10:09:13 2190

2190

D触发器的稳态 D触发器是数字电路中常用的一种存储元件,它有两种稳态,即低电平稳态和高电平稳态。当输入D为低电平时,输出Q保持为低电平;当输入D为高电平时,输出Q保持为高电平。 D触发器和RS触发器

2024-02-06 11:32:41 5587

5587 稳态是指触发器在某个特定的输入状态下稳定保持输出的状态。根据触发器的类型和触发方式,触发器分为很多种类,不同类型的触发器有不同的稳态。本文将详细描述几种常见的触发器及其稳态,并介绍如何判断触发器

2024-02-06 13:36:55 7912

7912 D触发器是一种常见的数字逻辑电路,它在数字系统和计算机中扮演着重要的角色。本文将详细探讨D触发器的逻辑功能、工作原理以及RD(Reset-D)触发器和SD(Set-D)触发器的作用。 首先,我们先来

2024-02-06 13:52:14 52531

52531 触发器是数字电路中常用的组合逻辑电路,在现代电子系统中有着广泛的应用。其中,最常用的两种触发器是T触发器和JK触发器。本文将详细介绍T触发器和JK触发器的区别和联系。 一、T触发器 T触发器是一种单

2024-02-06 14:04:55 7823

7823 如何用JK触发器构成T触发器 JK触发器是一种基本的触发器电路,由两个输入端J和K控制,以及两个输出端Q和Q'组成。JK触发器的输出可以持续性地保持其前一状态或由输入信号而改变。T触发器是一种特殊

2024-02-06 14:11:11 12517

12517 D触发器是一种经典的时序逻辑电路,具有广泛的应用领域。它的功能包括存储和传输数据,以及在时钟信号的作用下进行状态转换。本文将探讨D触发器的功能和状态方程。 首先,让我们从D触发器的基本功能开始讨论

2024-02-18 16:28:45 17729

17729 触发方式可以有效地减少电路的功耗和提高电路的稳定性。边沿触发器有多种类型,下面介绍几种常见的边沿触发器类型。 D触发器(Data Flip-Flop) D触发器是一种最基本的边沿触发器,它具有一个数据输入端(D)、一个时钟输入端(CLK)和一个输出端(Q)。D触发器的功

2024-08-11 09:07:32 1938

1938 在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的是T触发器(Toggle Flip-Flop)和D触发器(Data Flip-Flop

2024-08-11 09:37:25 6781

6781 D触发器(Data Flip-Flop)是一种常见的数字逻辑电路元件,主要用于存储一位二进制数据。D触发器可以是电平触发的,也可以是边沿触发的,具体取决于设计和应用需求。 电平触发D触发器 1.1

2024-08-22 10:17:27 3013

3013 在数字电路设计中,触发器是一种非常重要的存储元件,用于存储一位二进制信息。触发器的种类很多,其中最为常见的有JK触发器、D触发器和T触发器等。 一、触发器的基本概念 1.1 触发器的定义 触发器

2024-08-22 10:33:51 3767

3767 ,可以存储一位二进制信息。触发器的输出状态取决于输入信号和触发器的当前状态。触发器的分类主要有D触发器、JK触发器、T触发器等。 D触发器 D触发器是一种常见的触发器类型,其名称来源于其数据输入端(Data input)的缩写。D触发器具

2024-08-22 10:37:33 5060

5060 D触发器和D锁存器是数字电路中常用的两种存储元件,它们在功能和应用上有一定的区别。 定义和功能 D触发器(Data Flip-Flop)是一种具有两个稳定状态的双稳态电路,它可以存储一位二进制信息

2024-08-28 09:34:17 3723

3723 在数字逻辑电路中,D触发器(Data Flip-Flop)和RS触发器(Reset-Set Flip-Flop)是两种常用的存储单元。它们在功能上有一定的相似性,但也存在一些差异。 一、D触发器

2024-08-28 09:35:37 2844

2844 将JK触发器变成T触发器,主要涉及到对JK触发器的输入端口进行适当的连接和配置,以实现T触发器的逻辑功能。以下是将JK触发器转换为T触发器的具体步骤: 步骤一:理解JK触发器和T触发器的逻辑功能

2024-08-28 09:41:19 6045

6045

电子发烧友App

电子发烧友App

评论