用D触发器设计一个序列发生器 怎么用D触发器做序列信号发生器?

序列发生器是数字电子技术中常用的电路模块之一,它可以用来生成一系列的数字信号序列。在数字电路中,D触发器是一种被广泛使用的数字逻辑组件,在很多应用场景中都可以用来构建序列发生器。本文将介绍使用D触发器设计序列发生器的方法和步骤。

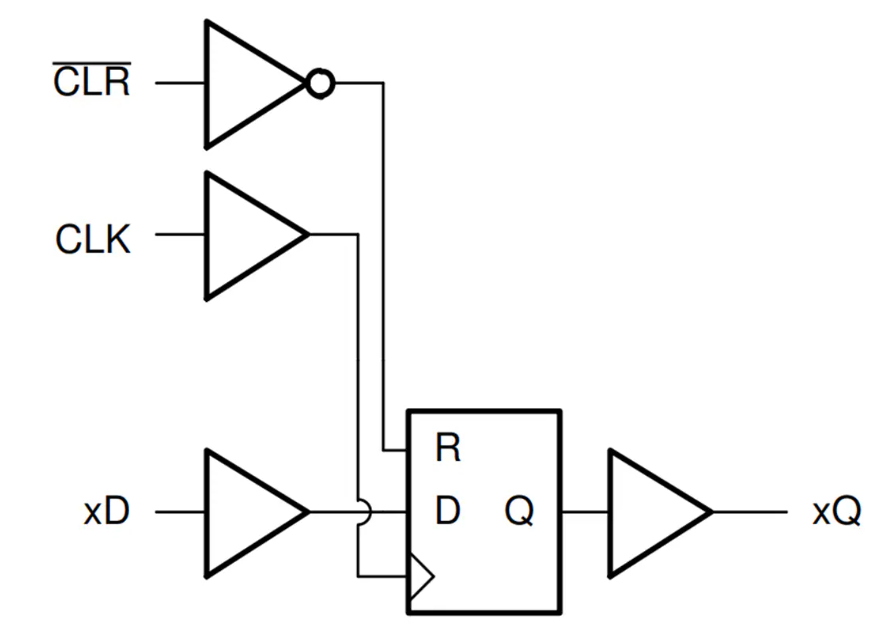

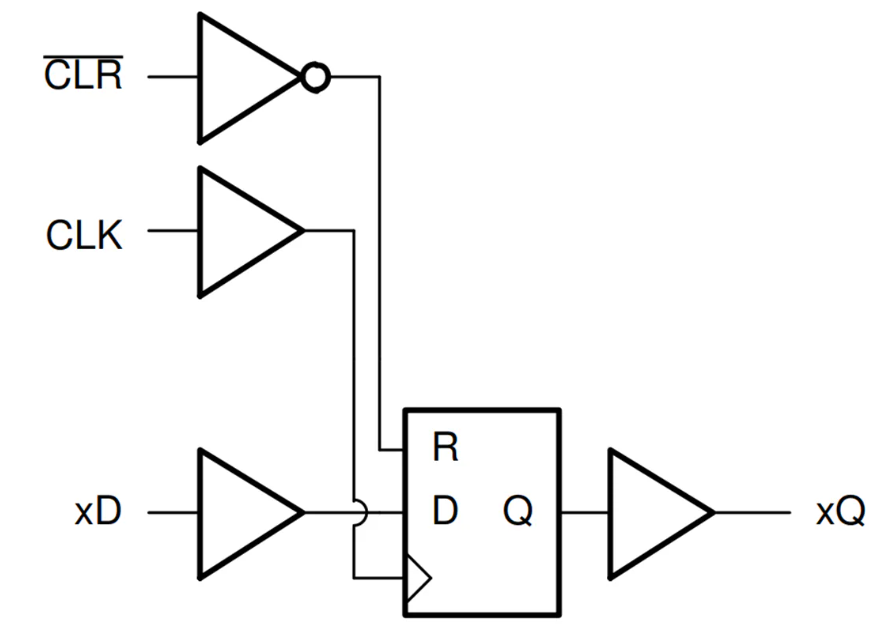

首先,我们需要了解D触发器的基本原理和性质。D触发器是一种时序电路,它可以存储和延迟一个输入信号,并在时钟信号到来时输出这个输入信号的状态。

其中,D表示输入端输入的电平,Q表示输出端输出的电平,CLK表示时钟信号。当时钟信号从低电平变为高电平(上升沿)时,D触发器将输入端的值D存储到内部,同时输出端的值Q也随之变化。当时钟信号从高电平变为低电平(下降沿)时,D触发器不受外界信号的影响,内部的状态保持不变。

使用D触发器可以构建一个简单的二进制序列发生器。假设我们要生成一个从0到7的8位二进制循环序列,我们可以按照以下步骤进行设计。

1. 首先,需要定义一个8位计数器,用来计数并产生序列。

2. 通过D触发器和与门,建立时序电路,实现时序控制。

3. 将输出端的二进制信号接入到各个D触发器的D端。

4. 通过时钟信号,不断切换D触发器的状态,使得每个时钟周期都能够产生一个新的二进制数。

5. 最后将输出端的信号进行显示或接入其他模块进行进一步处理。

在此基础上,我们可以进一步设计出更加复杂的序列发生器。例如,可以通过串联多个D触发器,构建更高位数的二进制序列;还可以使用多路选择器和计时器,实现随机序列或者周期变化的序列。

总之,D触发器是构建数字序列发生器的重要组件之一,掌握使用D触发器设计序列发生器的方法和技巧,对于数字电子技术的学习和应用都有很大帮助。

序列发生器是数字电子技术中常用的电路模块之一,它可以用来生成一系列的数字信号序列。在数字电路中,D触发器是一种被广泛使用的数字逻辑组件,在很多应用场景中都可以用来构建序列发生器。本文将介绍使用D触发器设计序列发生器的方法和步骤。

首先,我们需要了解D触发器的基本原理和性质。D触发器是一种时序电路,它可以存储和延迟一个输入信号,并在时钟信号到来时输出这个输入信号的状态。

其中,D表示输入端输入的电平,Q表示输出端输出的电平,CLK表示时钟信号。当时钟信号从低电平变为高电平(上升沿)时,D触发器将输入端的值D存储到内部,同时输出端的值Q也随之变化。当时钟信号从高电平变为低电平(下降沿)时,D触发器不受外界信号的影响,内部的状态保持不变。

使用D触发器可以构建一个简单的二进制序列发生器。假设我们要生成一个从0到7的8位二进制循环序列,我们可以按照以下步骤进行设计。

1. 首先,需要定义一个8位计数器,用来计数并产生序列。

2. 通过D触发器和与门,建立时序电路,实现时序控制。

3. 将输出端的二进制信号接入到各个D触发器的D端。

4. 通过时钟信号,不断切换D触发器的状态,使得每个时钟周期都能够产生一个新的二进制数。

5. 最后将输出端的信号进行显示或接入其他模块进行进一步处理。

在此基础上,我们可以进一步设计出更加复杂的序列发生器。例如,可以通过串联多个D触发器,构建更高位数的二进制序列;还可以使用多路选择器和计时器,实现随机序列或者周期变化的序列。

总之,D触发器是构建数字序列发生器的重要组件之一,掌握使用D触发器设计序列发生器的方法和技巧,对于数字电子技术的学习和应用都有很大帮助。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

发生器

+关注

关注

4文章

1423浏览量

64409 -

计数器

+关注

关注

32文章

2306浏览量

97571 -

D触发器

+关注

关注

3文章

181浏览量

49532 -

信号发生器

+关注

关注

28文章

1647浏览量

112824 -

数字序列发生器

+关注

关注

0文章

3浏览量

5897

发布评论请先 登录

相关推荐

热点推荐

MC74VHCT374A Octal D型触发器技术解析与应用指南

安森美MC74VHCT374A D触发器是一款具有3态输出的高速CMOS八通道触发器,采用硅栅极CMOS技术制成。这些器件是8位D型

延迟脉冲信号发生器在激光触发领域的应用

在激光技术飞速发展的当下,高速延迟脉冲信号发生器作为激光系统中的关键部件,其重要性愈发凸显。SYN5610型脉冲信号发生器凭借出色性能,在激光触发

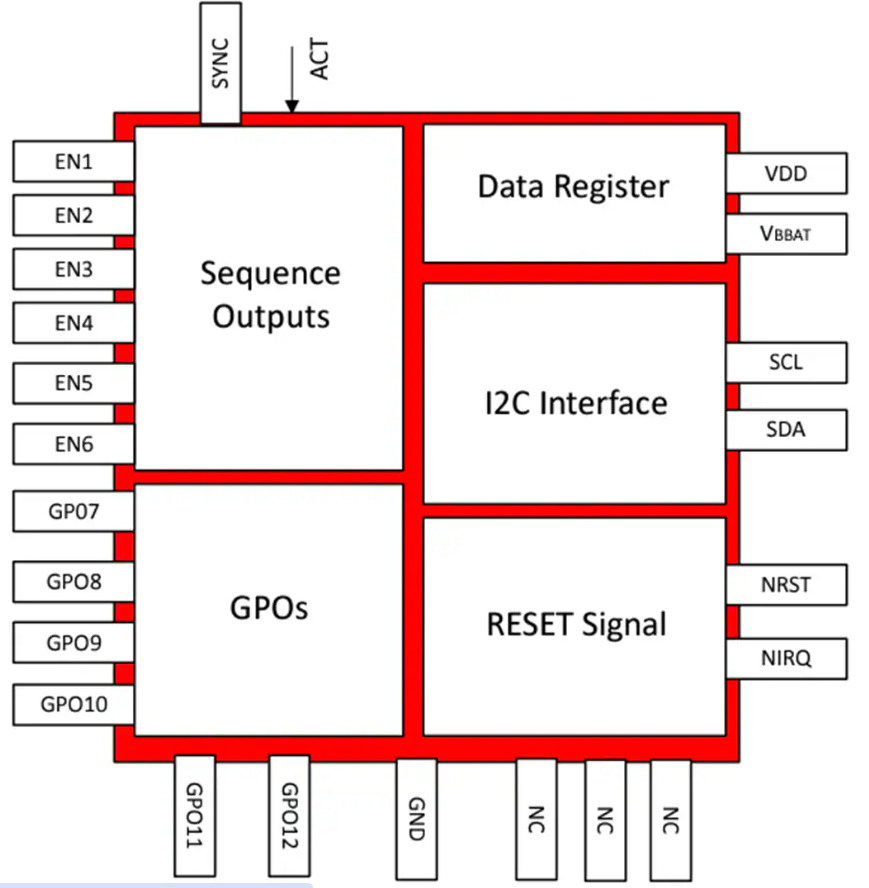

TPS38700S-Q1多通道电压序列发生器技术解析

Texas Instruments TPS38700S-Q1集成式多通道电压序列发生器配有窗口看门狗、I^2^C可编程,采用24引脚4mm x 4mm VQFN封装。该多通道电压序列发生器

Texas Instruments SN74ACT174-Q1六路D型触发器数据手册

Texas Instruments SN74ACT174-Q1六路D型触发器包含六个D型触发器,具有共享低电平有效清除 (CLR) 和上升沿

Texas Instruments SN74AC174-Q1六路D型触发器数据手册

Texas Instruments SN74AC174-Q1六路D型触发器包含六个D型触发器,具有共享低电平有效清除 (CLR) 和上升沿

74ALVT162823 18位总线接口D型触发器规格书

电子发烧友网站提供《74ALVT162823 18位总线接口D型触发器规格书.pdf》资料免费下载

发表于 02-18 17:36

•0次下载

触发器的作用与应用

触发器的作用 数据完整性维护 :触发器可以用来维护数据库中的数据完整性。例如,它们可以确保在更新或插入数据时,相关的数据约束得到满足。 自动数据更新 :触发器可以自动更新表中的数据,而不需要用户手动

用D触发器设计一个序列发生器 怎么用D触发器做序列信号发生器?

用D触发器设计一个序列发生器 怎么用D触发器做序列信号发生器?

评论