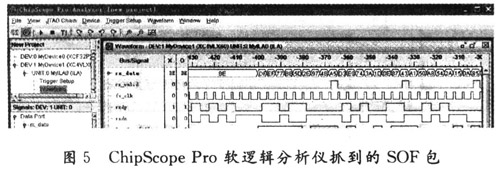

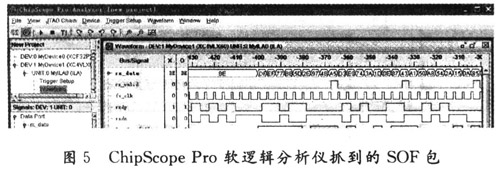

介绍了一款可配置的USB IP核设计,重点描述USB IP核的结构划分,详细阐述了各模块的设计思想。为了提高USB lP的可重用性,本USB IP核设计了总线适配器,经

2010-07-17 10:39:51 3124

3124

采用基于IP复用技术进行设计是减小这一差距惟一有效的途径,IP复用技术包括两个方面的内容:IP核生成和IP核复用。文中采用IP核复用方法和SOC技术基于AVR 8位微处理器AT90S1200IP Core设计专

2012-01-12 14:22:47 2515

2515

本文介绍了LCD的通用驱动电路IP核设计,采用自顶向下的设计方法将其划分为几个主要模块,分别介绍各个模块的功能,用VHDL语言对其进行描述,用FPGA实现并通过了仿真验证。该IP核具有良好的移植性,可驱动不同规模的LCD电路。

2014-05-13 10:09:35 3236

3236 IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则

2012-08-12 12:21:36

本帖最后由 eehome 于 2013-1-5 09:59 编辑

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改

2011-07-06 14:15:52

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动。随着CPLD

2011-07-15 14:46:14

我想问一下,在quartus上直接调用IP核和在qsys中用IP核有什么区别?自个有点迷糊了

2017-08-07 10:09:03

我调用了一个ip核 在下载到芯片中 有一个time-limited的问题 在完成ip核破解之后 还是无法解决 但是我在Google上的找到一个解决方法就是把ip核生成的v文件加到主项目文件中就是上面

2016-05-17 10:28:47

公司现需12bit sar adc的IP核,国内有哪些公司提供相关方面的服务了?

2015-11-06 08:37:44

控制机制对当前变长分组骨干网的流量控制还是具有重要的参考价值,所以有必要对ATM的流量控制及其实现方式进行深入的研究。 IP核是一段具有特定电路功能的硬件描述语言代码,该程序与集成电路工艺无关,因而

2011-09-27 11:54:25

用Quartus II 调用IP核时,在哪可以查看IP核的例程

2014-07-27 20:28:04

Altera_IP核,仅供参考

2016-08-24 16:57:15

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是与FPGA独立的,只是集成在了一起呢,还是占用了FPGA的资源来形成一个RAM?如果我以ROM的形式调用该IP核,在

2013-01-10 17:19:11

FPGA的IP软核使用技巧主要包括以下几个方面:

理解IP软核的概念和特性 :

IP软核是指用硬件描述语言(如VHDL或Verilog)描述的功能块,但并不涉及具体的电路实现细节。它通常只经过功能

2024-05-27 16:13:24

如何根据成本、功耗和性能来选择微处理器?FPGA结构中硬核和软核的特点是什么?处理器IP有什么重要性?

2021-04-08 06:16:37

本帖最后由 gk320830 于 2015-3-8 09:29 编辑

LCD的通用驱动电路IP核设计 摘 要:本文介绍了一种新型的LCD驱动电路IP核的总体设计,采用自顶向下的设计方法将其

2012-08-12 12:28:42

大家好,有没有谁比较熟悉ALTERA公司的VIP系列ip核,我们用该系列IP核中的某些模块(主要是scaler和interlacer)来实现高清图像转标清图像(具体就是1080p50转576i30

2015-04-13 14:12:18

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

求用sopc builder定制IP核的步骤,是9.0的软件,假设硬件代码已有

2013-09-14 18:35:40

请问哪位高手有ise软件中的各个ip核的功能介绍

2013-10-08 16:41:25

有哪位大神用过pci ip核,为什么输入lm_req32请求,pci侧没有reqn请求输出呢?

2016-06-27 17:56:59

本帖最后由 ys_1*****8201 于 2016-5-19 14:16 编辑

Quartus IP核破解在完成quartus软件安装之后,一般都要进行一个软件破解。对于一般的需求来说

2016-05-19 14:13:09

,可以打开参数设置对话框。点击左上方的Documentation可以查看IP核的手册。这里将输入的A、B均设置为4为无符号型,其他为默认值,点击OK确认。三、绘制电路1. 右击Diagram窗口空白处

2018-05-15 12:05:13

有没有大神可以提供xilinx FPGA的FFT IP核的调用的verilog 的参考程序,最近在学习FFT的IP核的使用,但是仿真结果有问题,所以想找些参考设计,谢谢

2016-12-25 17:05:38

随着电路规模不断扩大,以及竞争带来的上市时间的压力,越来越多的电路设计者开始利用设计良好的、经反复验证的电路功能模块来加快设计进程。这些电路功能模块被称为IP(Intellectual Property)核。

2019-11-04 07:40:53

刚刚接触IP核做FFT,现在用的是FFTV9.0,已经建立了一个IP核,但是如何仿真呢?是用quartus自带软件,还是要用MATLAB?抑或其他?我用的自带软件,但是什么也没有出来。正确的办法应该怎样呢,谢谢指点。

2011-04-21 10:22:31

对于深入学习使用FPGA的小伙伴们,特别是一些复杂的、大规模的设计应用,适宜的IP核对开发能起到事半功倍的作用。IP核的概念与我们sdk里库的概念相似。IP即电路功能模块,用户可以直接调用这些模块

2024-04-29 21:01:16

quartus ii9.0创建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)这些文件都有用吗,想在其他工程里调用这些IP核,这几个文件全部要添加吗?

2013-07-02 17:20:01

核的分类和特点是什么?基于IP核的FPGA设计方法是什么?

2021-05-08 07:07:01

引言随着半导体技术的发展,深亚微米工艺加工技术允许开发上百万门级的单芯片,已能够将系统级设计集成到单个芯片中即实现片上系统SoC。IP核的复用是SoC设计的关键,但困难在于缺乏IP核与系统的接口标准

2019-06-11 05:00:07

Viterbi译码的基本过程,接着根据Viterbi译码器IP核的特点,分别详细介绍了并行结构、混合结构和基于混合结构的增信删余3种Viterbi译码器IP核的主要性能和使用方法,并通过应用实例给出了译码器IP

2010-04-26 16:08:39

我毕业设计要做一个基于FPGA的IP核的DDS信号发生器,但是我不会用DDS的IP核,有没有好人能发我一份资料如何用IP核的呀。我的浏览器下载不了网站上的资料,所以只能发帖求帮忙了。

2015-03-10 11:46:40

on Chip)是以嵌入式系统为核心,以IP复用技术为基础,集软、硬件于一体的设计方法。使用IP复用技术,将UART集成到FPGA器件上,可增加系统的可靠性,缩小PCB板面积;其次由于IP核的特点

2019-08-20 07:53:46

什么是三相全控桥整流电路?怎样去设计IP软核?怎样对IP软核进行仿真及验证?

2021-04-23 07:12:38

本人FPGA小白一枚,最近使用到FPGA的IP核遇到一个问题。比如说:某个IP,用于计算sin函数,使用了流水线机制,所有从输入到输出需要20个时钟周期的延时。另外,还有一个IP,从输入到输出需要1

2021-06-19 11:06:07

请问Altera RAM IP核怎么使用?

2022-01-18 06:59:33

这是我们一个小比赛的题面:设计一个简易的电子计算器电路,包括输入数据处理电路,算数运算电路(包含加法、减法、乘法、除法等算数运算),运算结果处理电路,所有运算电路的设计均不可使用IP核及查找表进行

2018-04-06 20:46:11

以SCI接口电路为例,介绍基于FPGA器件的接口电路IP核如何去设计?

2021-04-28 06:10:23

章礼宏 范全润1 引言随着电路规模不断扩大,以及竞争带来的上市时间的压力,越来越多的电路设计者开始利用设计良好的、经反复验证的电路功能模块来加快设计进程。这些电路功能模块被称为IP

2019-07-29 08:33:45

提出一种可进化IP 核的设计和实现方法。这种IP 核采用进化硬件的设计思想, 将遗传算法运用于硬件电路的设计中,使电路能根据当前的环境自动进行内部电路的进化,从而生成最

2009-05-16 14:33:28 14

14 IP核生成器生成ip后有两个文件对我们比较有用,假设生成了一个asyn_fifo的核,则asyn_fifo.veo给出了例化该核方式(或者在Edit->Language Template->COREGEN中找到verilog/VHDL的例化方式)

2009-07-21 16:42:12 0

0 IC设计技术中的IP核互连:随着IC 设计复杂度的不断提高,在SoC 中集成的IP 核越来越多,基于片上总线的SOC 设计技术解决了大规模集成电路的设计难点,但是片上总线的应用带来了

2009-10-14 12:50:23 8

8 随着集成电路设计复杂度的提高和产品上市时间压力的增大,基于IP 核复用的SoC 设计已成为一种重要的设计方法。在SoC 中集成的IP 核越来越多时,IP 核的互连策略和方法就成

2009-11-28 14:40:46 8

8 USB设备接口IP核的设计:讨论了用Verilog硬件描述语言来实现USB设备接口IP核的方法,并进行了FPGA的验证。简要介绍USB系统的体系结构,重点描述USB设备接口IP核的结构划分和各模块的

2010-01-08 18:15:38 22

22 以 FPGA 技术为基础,以Verilog HDL 为载体,设计了遵守Wishbone 片上总线规范的IP 核接口,实现了片上系统的IP 核互联。

2010-01-13 15:09:14 13

13 基于Avalon总线的可配置LCD 控制器IP核的设计

本文讨论了基于Avalon 总线流传输的配置LCD 显示控制器IP 核的设计,根据自顶向下的设计思想,将IP 核进行层次功能

2010-02-09 09:34:44 27

27 本文详述了一种基于AMBA总线接口的IIC总线控制器IP核设计,给出了该IP核的系统结构以及各个子模块的详细设计方法,并对该IP核进行了功能仿真、FPGA原型验证,可测性设计以

2010-07-17 16:20:22 21

21 基于BIST的编译码器IP核测

随着半导体工艺的发展,片上系统SOC已成为当今一种主流技术。基于IP复用的SOC设计是通过用户自定义逻辑(UDL)和连线将IP核整合

2008-12-27 09:25:39 1195

1195

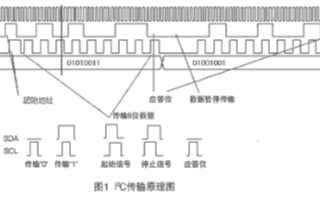

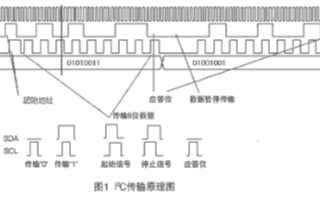

I2C器件接口IP核的CPLD设计

根据单片机I2C串行扩展的特点,在EDA软件MaxplusII的环境下,利用AHDL语言,建立IP核。此设计利用状态机实现,在给出设计的同时详细说明IP核的建立

2009-03-28 16:21:35 1351

1351

摘 要: 根据单片机I2C串行扩展的特点,在EDA软件MaxplusII的环境下,利用AHDL语言,建立IP核。此设计利用状态机实现,在给出设计的同时详细说明IP核的建立过程,并下载到

2009-06-20 13:36:12 1065

1065

基于PCI IP核的码流接收卡的设计

本文介绍了一种基于Altera公司的PCI接口IP核的DVB码流接收系统的硬件设计方案及设计要点的分析。该设计采用Altera公司的新一代FPGA

2009-09-26 18:02:08 912

912

介绍了FreeARM7 IP核的基本概况及其接口特点,以LPC2101为原型对该IP核进行了扩展。结合USB 1.1设备控制器IP核和自定制硬件逻辑,构建了一种微控制器功能验证回路。

2011-04-06 11:41:13 2369

2369

本文介绍的基于Wishbone总线的UART IP核的设计方法,通过验证表明了各项功能达到预期要求,为IP核接口的标准化设计提供了依据。此外,该IP核代码全部采用模块化的Verilog-HDL语言编写,

2011-06-10 11:47:37 4199

4199

文章采用TOP-DOWN 的方法设计了 AMBA 总线IP 核!它包括AHB 和APB两个子IP 核 所有AMBA结构模块均实现了RTL级建模

2011-07-25 18:10:52 93

93 介绍了SoPC(System on a Programmable Chip)系统的概念和特点,给出了基于PLB总线的异步串行通信(UART)IP核的硬件设计和实现。通过将设计好的UART IP核集成到SoPC系统中加以验证,证明了所

2012-03-05 17:53:49 63

63 我国集成电路设计业的高速发展带动IP核市场稳步扩大,国内企业对IP核的数量、质量和服务的需求都在不断增加。

2012-12-23 12:28:42 1459

1459 定制简单LED的IP核的设计源代码

2012-12-23 16:43:53 75

75 FPGA中IP核的生成,简单介绍Quartus II生成IP核的基本操作,简单实用挺不错的资料

2015-11-30 17:36:15 12

12 Xilinx FPGA工程例子源码:PCI Express IP核应用参考设计

2016-06-07 14:13:43 14

14 Xilinx FPGA工程例子源码:USB IP核

2016-06-07 14:41:57 13

13 基于8051内核IP核的应用,感兴趣的小伙伴们可以瞧一瞧。

2016-11-11 18:18:32 1

1 一种小规模LCD驱动电路IP核的设计

2017-01-14 12:35:39 11

11 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言

2017-02-08 13:08:11 3085

3085

电子设计工程 基于FPGA的Flexray IP核通信的研究与实现

2017-08-30 16:08:32 13

13 本文介绍了LCD的通用驱动电路IP核设计,采用自顶向下的设计方法将其划分为几个主要模块,分别介绍各个模块的功能,用VHDL语言对其进行描述,用FPGA实现并通过了仿真验证。该IP核具有良好的移植性

2017-10-26 17:21:59 15

15 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言

2017-11-15 11:19:14 10744

10744 本文档内容介绍了建立用户自己的IP核的操作步骤,供参考

2018-04-03 11:26:51 4

4 大家好,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。 首先咱们来了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 38569

38569 AD的IP核哪里有?

2018-10-06 15:37:29 469

469 利用IP核设计电子系统,引用方便,修改基本元件的功能容易。具有复杂功能和商业价值的IP核一般具有知识产权,尽管IP核的市场活动还不规范,但是仍有许多集成电路设计公司从事IP核的设计、开发和营销工作。

2019-12-19 07:06:00 2168

2168

利用IP核设计电子系统,引用方便,修改基本元件的功能容易。具有复杂功能和商业价值的IP核一般具有知识产权,尽管IP核的市场活动还不规范,但是仍有许多集成电路设计公司从事IP核的设计、开发和营销工作。

2019-10-08 07:07:00 1949

1949 由于CPLD数字设计结构化的趋势,将出现针对CPLD不同层次的IP(Intellectual Property)核。各个IP核可重复利用,可大大提高设计能力和效率。国外各大公司都推出了专门的IP核,我国也迫切需要发展自己的IP核。本文针对I2C的主方式串行扩展通信的特点,详细给出设计过程和结果。

2020-04-07 09:54:10 4073

4073

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核

2020-12-29 15:59:39 13270

13270 提出一种可进化IP核的设计和实现方法。这种IP核采用进化硬件的设计思想,将遗传算法运用于硬件电路的设计中,使电路能根据当前的环境自动进行内部电路的时化,从而生成最有效的电路,并能在普通的FPGA器件

2021-06-22 14:37:40 3382

3382

在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

Vivado IP核提供了强大的FIFO生成器,可以通过图形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7270

7270

在给Vivado中的一些IP核进行配置的时候,发现有Shared Logic这一项,这里以Tri Mode Ethernet MAC IP核为例,如图1所示。

2023-09-06 17:05:12 3014

3014

整体而言,作为集成电路产业上游的IP核领域,市场呈现出前所未有的垄断与集中态势。2013 年,全球半导体 IP 市场规模达到 24.5亿美元,较2012年增长了 11.5%。ARM 以 43.2%的市场占有率遥遥领先,稳居龙头地位。

2023-10-18 17:02:44 1904

1904 电子发烧友网站提供《HDLC协议IP核的设计与实现.pdf》资料免费下载

2023-11-08 15:45:33 5

5 电子发烧友网站提供《LCD的通用驱动电路IP核设计.doc》资料免费下载

2023-11-15 11:15:37 2

2 Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 在使用FPGA的时候,有些IP核是需要申请后才能使用的,本文介绍如何申请xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

在创新加速的浪潮中,为更好地响应客户群需求, 芯驿电子 ALINX 推出全新 IP 核产品线 ,致力于为高性能数据传输和复杂计算需求提供 高带宽、低延迟 的解决方案。发布的第一批 IP 核包括

2024-10-30 17:39:43 1459

1459

本文介绍了Vidado中FFT IP核的使用,具体内容为:调用IP核>>配置界面介绍>>IP核端口介绍>>MATLAB生成测试数据>>测试verilogHDL>>TestBench仿真>>结果验证>>FFT运算。

2024-11-06 09:51:43 5640

5640

电子发烧友App

电子发烧友App

评论