随着大模型、高性能计算、量化交易和自动驾驶等大数据量和低延迟计算场景不断涌现,加速数据处理的需求日益增长,对计算器件和硬件平台提出的要求也越来越高。发挥核心器件内部每一个计算单元的作用,以更大带宽连接内外部存储和周边计算以及网络资源,已经成为智能化技术的一个重要趋势。这使得片上网络(Network-on-Chip)这项已被提及多年,但工程上却不容易实现的技术再次受到关注。

作为一种被广泛使用的硬件处理加速器,FPGA可以加速联网、运算和存储,其优点包括计算速度与ASIC相仿,也具备了高度的灵活性,能够为数据中心与边缘计算提供理想的数据处理加速;除此之外,FPGA还在传感器融合和输入数据流整理汇流等领域发挥关键作用,是智能化应用中从边到云全链路上重要的计算器件。

近年来,诸如Achronix这样提供高容量、高密度和高算力FPGA的供应商,在其高端FPGA芯片中,使用了越来越多的硬IP去提升FPGA芯片对外的数据传输带宽以及存储器带宽。但是在逻辑阵列密度不断快速提升的同时,外部通信和网络带宽的提升并不能完全满足新兴应用的需求,所以FPGA内部数据的交换越来越成为数据传输的瓶颈。

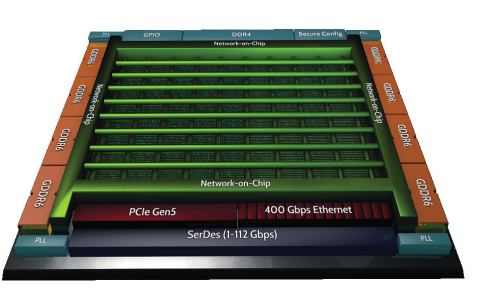

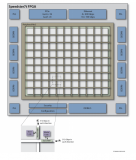

Achronix将此挑战视为一个开发全新架构的机会,以消除传统FPGA的设计挑战并提高系统性能。Achronix的解决方案是在传统FPGA逻辑阵列布局和布线结构之上,创新地使用了革命性的二维(2D)高速片上网络(NoC)。Achronix不久前在业界率先推出了集成2D NoC的Speedster7t器件,这些创新带来了FPGA设计、工程和应用等方面的根本转变。

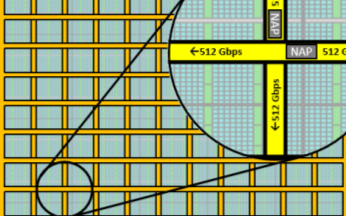

2D NoC是Speedster7t FPGA芯片内可编程逻辑阵列上面部署的覆盖全域的高速纵与横(行和列)数据通道,它们分别向FPGA可编程逻辑阵列的水平和垂直方向提供高速的传输通道。除了这些行和列之外,在NoC硬核的每一行和每一列的交叉位置还有发送点和NoC访问的目标节点(NAP)。这些NAP充当NoC硬核位于可编程逻辑阵列资源之间传输的起点或目的点。

在该FPGA器件的外围,这个硬2D NoC连接到所有高速接口:包括多个400G以太网、PCIe Gen5、GDDR6和DDR4/5端口。这使得Achronix的Speedster7t成为了业界第一款可以商用的集成全域硬2D NoC的FPGA器件,以每通道512Gbps的速率和超过2Tbps的总带宽来与所有系统接口和FPGA逻辑阵列互连。

这种新架构使得Achronix的FPGA器件特别适用于高带宽应用,同时极大提高了设计人员的工作效率。由于2D NoC管理着从用FPGA逻辑阵列实现的数据加速器功能模块到高速数据接口之间的所有交互功能,因此设计人员只需设计他们的数据加速器功能,然后将它们连接到NAP接口。与使用软核2D NoC相比,通过硬核2D NoC做数据交互,设计人员可以受益于以下优点:

● 降低逻辑资源占有率并提高FPGA的整体性能

● 增加带宽

● 减少对存储器的需求

● 更快的设计时间和更短的工具编译时间

Achronix的FPGA中特有的创新的全域2D NoC硬核,对比用可编程逻辑资源来实现的软核2D NoC的传统方法,有诸多益处。在近期发表的白皮书《白皮书:Achronix在其先进FPGA中集成2D NoC以支持高带宽设计(WP028)》中,详尽介绍了全域2D NoC硬核的各种技术细节,并讨论了硬核和软核的两种2D NoC的差异,并提供了一个设计示例,展示硬核与软核2D NoC的对比结果,以及Achronix 的全域硬2D NoC是如何去提高性能、改善带宽、减少面积并缩短设计时间和工具运行时间。

-

传感器

+关注

关注

2573文章

54368浏览量

786061 -

FPGA

+关注

关注

1655文章

22283浏览量

630286 -

智能化

+关注

关注

15文章

5209浏览量

59705

原文标题:利用搭载全域硬2D NoC的FPGA器件去完美实现智能化所需的高带宽低延迟计算

文章出处:【微信号:Achronix,微信公众号:Achronix】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

利用片上高速网络(2D NoC)创新地实现FPGA内部超高带宽逻辑互连

在FPGA设计中如何充分利用NoC资源去支撑创新应用设计

可视化的片上网络(NoC)性能分析

技术文章:如何利用NoC来进行FPGA内部逻辑的互连

利用NoC资源解决FPGA内部数据交换的瓶颈

如何利用NoC资源去支撑FPGA中的创新设计

如何利用片上高速网络创新地实现FPGA内部超高带宽逻辑互连?

怎么让FPGA内部超高带宽逻辑互连的方法

2D NoC可实现FPGA内部超高带宽的逻辑互连

通过2D NoC可实现FPGA内部超高带宽逻辑互连

浅析可视化的片上网络(NoC)性能

利用搭载全域硬2D NoC的FPGA器件去完美实现智能化所需的高带宽低延迟计算

利用搭载全域硬2D NoC的FPGA器件去完美实现智能化所需的高带宽低延迟计算

评论