摘要

随着旨在解决现代算法加速工作负载的设备越来越多,就必须能够在高速接口之间和整个器件中有效地移动高带宽数据流。Achronix的Speedster7t独立FPGA芯片可以通过集成全新的、高度创新的二维片上网络(2D NoC)来处理这些高带宽数据流。Achronix的FPGA中特有的2D NoC实现是一种创新,它与用可编程逻辑资源来实现2D NoC的传统方法相比,有哪些创新和价值呢?本白皮书讨论了这两种实现2D NoC的方法,并提供了一个示例设计,以展示与软2D NoC实现相比,Achronix 2D NoC是如何去提高性能、减少面积并缩短设计时间。

介绍

Achronix为其Speedster7t系列FPGA完全重新设计了片上通信架构,通过集成创新的2D NoC来适应高带宽数据流的需求。在该FPGA器件的外围,这个2D NoC连接到所有高速接口:包括多个400G以太网、PCIe Gen5、GDDR6和DDR4/5端口。在该FPGA内的可编程逻辑阵列上部署了一系列高速行和列通道,它们分别向FPGA可编程逻辑阵列的水平和垂直方向分配网络流量。除了这些行和列之外,在NoC的每一行和每一列交叉的位置还有发送点和目标NoC访问节点(NAP)。这些NAP充当NoC和位于可编程逻辑阵列中的资源之间的源或目的地。

为了将Achronix FPGA中内置的2D NoC,与使用传统方法在可编程逻辑阵列中创建的NoC进行比较,为此我们评估了几种软NoC设计;最后,基于同行评审和FPGA结构的可移植性,我们选择了米兰理工学院的软2D NoC(https://github.com/agalimberti/NoCRouter,2017)设计。这种软NoC在单向网状网络(mesh)中实现了虫洞前瞻预测切换。在实施时,它需要每个mesh节点上的多个存储器来存储和转发流控制单元(flit)。

为了量化片上2D NoC实现模式和使用逻辑阵列资源的软实现模式之间的差异,首先创建了一个实例化AlexNet 2D卷积的19个实例设计,然后在完整的2D NoC设计之间比较了三个主要指标:所需资源、设计性能和设计时间(创建设计的时间以及在工具中编译设计的时间)。其结果是在所有三种情况下,集成Achronix 2D NoC的性能都明显优于软实现。

2D NoC减少使用的资源

为了比较两种不同的2D NoC设计,两种2D NoC都与现有的2D卷积(conv2d)设计相结合。conv2d设计对输入图像执行AlexNet 2D卷积。此conv2d设计需要一个或两个AXI-4连接:一个用于从内存读取,一个用于写入内存,或者一个共享的AXI-4执行读取和写入。为了实现与软NoC的最佳集成,选择了单个共享AXI-4接口,conv2d模块的实例位于每个mesh节点。然后,软NoC启用了GDDR6存储接口的数据入口和出口——在软NoC中,内存接口连接到第20个mesh节点上;而在内置式NoC中,这种连接已经存在。在整个设计中,从GDDR6到每个conv2d节点都存在节点到节点通信,但conv2d节点之间不通信。

Achronix 2D NoC的设计细节

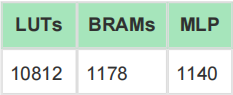

该设计有19个conv2d模块实例,每个实例都访问GDDR6存储器。第20个实例是空闲的,因为GDDR6接口直接连接到集成的2D NoC。80个可用的NoC接入点(NAP)中有38个用于连接到conv2d实例。每个conv2d实例使用64个机器学习处理器(MLP),它在垂直方向覆盖两个NAP。由于这种部署是针对内置2D NoC,所以采用双AXI-4方法连接conv2d模块。下表列出了本设计中使用的资源。

表1:Achronix 2D NoC使用的资源

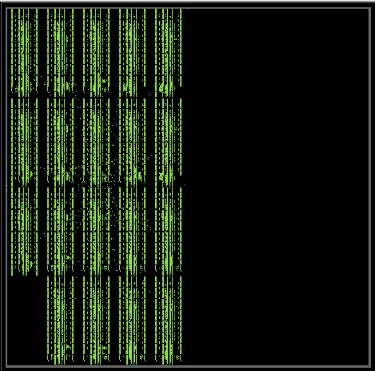

使用Achronix FPGA集成的2D NoC,可为设计布局产生了一种不凌乱的、可重复的结构,并且只消耗了不到一半的器件资源。下面是AC7t1500器件中资源使用的平面图。

图1:在AC7t1500中使用Achronix 2D NoC布局实例

软2D NoC的设计细节

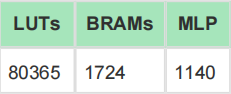

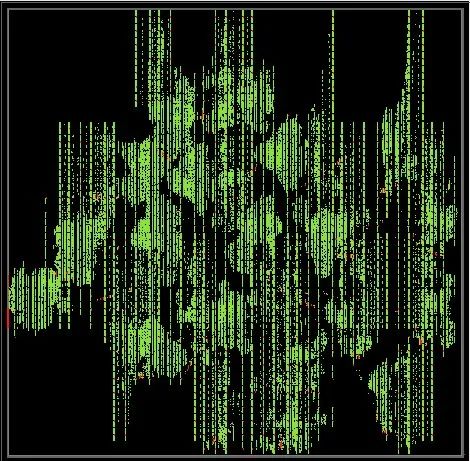

该设计被配置为5 × 4规模mesh,具有19个conv2d模块实例,每个实例都连接到一个软NoC节点。其第20 mesh节点是为GDDR6接口预留的。因此,需要更多的逻辑资源来管理软2D NoC结构。此实现还需要每个节点上的存储,以便存储flit并将其转发到下一个节点。结果是显著提高了资源的使用量,以及在器件上的不规则布局。下表列出了使用的资源;下图为AC7t1500所用资源的平面图。

表2:软2D NoC使用的资源

图2:使用软2D NoC布局实例

2D NoC提高性能

如前所述,通过使用Achronix 2D NoC,conv2d设计产生了规则的资源布局,从而形成规则的布线。减少了逻辑资源使用就减少了拥塞,因为需要布线的逻辑更少。该解决方案实现了最高565 MHz的频率,关键路径包含在conv2d实例逻辑中。随着更多conv2d节点添加到设计中,最大频率不会降低。

下图显示了使用Achronix 2D NoC时产生的布线

图3:使用Achronix 2D NoC的cnv2d设计布线

使用软2D NoC解决方案会导致复杂且不规则的布线,同时时序也受到影响,因为需要深度LUT逻辑来选择软2D NoC中的适当路径。

此外,性能会随着mesh网络大小的增加而降低。使用2 × 3 mesh的设计可以达到94 MHz,而5 × 4 mesh只能达到82 MHz。关键路径包含在软NoC mesh网络中,而不是在conv2d逻辑中。如果花更多时间优化设计以提高性能,则可以进一步优化软2D NoC的时序。

下图显示了使用软2D NoC设计时生成的布线。

图4:使用软2D NoC时的cnv2d设计布线

2D NoC改善了带宽

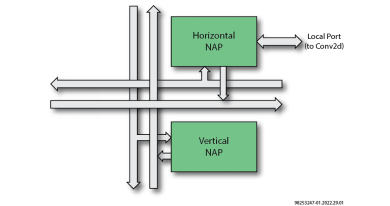

Achronix的2D NoC使用运行速度在2 GHz的256位双向总线,每个conv2d实例连接到两个NAP,从而在一个节点上与GDDR6接口之间的连接可实现的最大带宽为512 Gbps。下面的框图显示了2D NoC和一个连接到本地conv2d实例的NAP的细节。

图5:Achronix的2D NoC和NAP

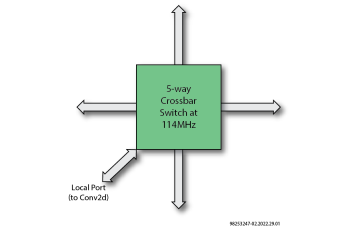

软2D NoC使用五路交叉开关(crossbar switch),其中一个端口与本地conv2d实例通信,而其他端口与网格中的下一个节点通信。该解决方案可以实现节点到节点连接的频率为82 MHz,从而在一个节点上形成最高为21 Gbps的GDDR6接口带宽。下面的框图显示了软2D NoC mesh中的一个交叉开关。

图6:软2D NoC交叉开关

2D NoC缩短了设计时间和工具运行时间

Achronix的2D NoC采用AXI-4标准与NAP通信,这是许多FPGA设计人员已经熟悉的接口标准。此外,2D NoC包括内置功能,例如跨时钟域逻辑、流量控制和地址解码等,这些功能不再需要包含在用户逻辑中。Achronix的2D NoC的全功能实现为用户省去了大量的设计工作,使设计人员能够专注于连接到2D NoC的加速器。

除了缩短设计时间外,使用Achronix片上2D NoC的设计比使用软2D NoC的设计使用更少的资源。结果是需要布局和布线的逻辑更少,从而使得工具的编译时间更短。例如,与使用软2D NoC的实现相比,使用Achronix片上2D NoC的设计布局和布线所需的时间不到一半。

结论

集成2D NoC的Speedster7t器件创新地带来了FPGA设计过程的根本转变。Achronix是第一家集成2D NoC的FPGA公司,它连接所有系统接口和FPGA逻辑阵列。这种新架构使Achronix FPGA器件特别适用于高带宽应用,同时显著提高了设计人员的工作效率。由于2D NoC管理着从设计在FPGA逻辑阵列中的数据加速器到高速数据接口之间的所有网络功能,因此设计人员只需设计他们的数据加速器并将它们连接到NAP接入点。与使用软2D NoC相比,设计人员可以受益于以下优点:

● 降低逻辑资源占有率并提高FPGA的整体性能

● 增加带宽

● 减少对存储器的需求

● 更快的设计时间和更短的工具编译时间

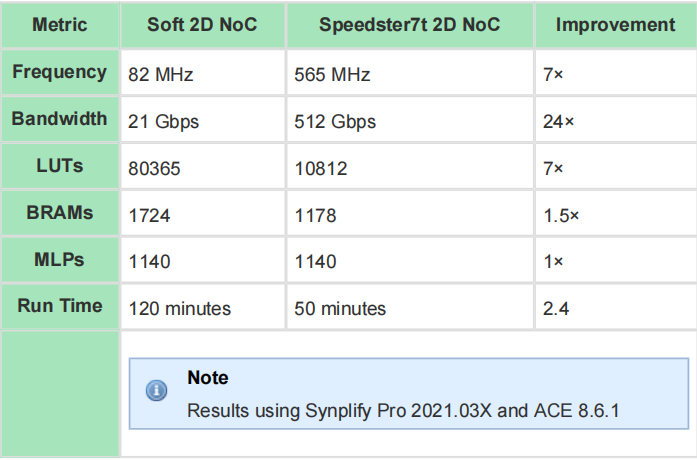

表3:Speedster7t 2D NoC与Soft 2D NoC的总结比较

如希望进一步了解Achronix Speedster7t FPGA芯片及其2D NoC可以发挥的巨大效用。

原文标题:Achronix在其先进FPGA中集成2D NoC以支持高带宽设计(WP028)

文章出处:【微信公众号:Achronix】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22509浏览量

639513 -

芯片

+关注

关注

463文章

54463浏览量

469656 -

NoC

+关注

关注

0文章

43浏览量

12220 -

Achronix

+关注

关注

1文章

78浏览量

23046

原文标题:Achronix在其先进FPGA中集成2D NoC以支持高带宽设计(WP028)

文章出处:【微信号:Achronix,微信公众号:Achronix】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

TechWiz LCD 2D:液晶透镜模拟

TechWiz LCD 2D应用:单畴IPS仿真

TMAG511x系列2D双通道高灵敏度霍尔效应锁存器技术解析

XS5018C:高性能2D/3D降噪ISP-TX 2K芯片电路图资料

2D、2.5D与3D封装技术的区别与应用解析

探索TRAVEO™ T2G Cluster 6M Lite Kit:功能、应用与编程指南

浅谈2D封装,2.5D封装,3D封装各有什么区别?

【CPKCOR-RA8D1】3、2D绘图引擎(D/AVE)DRW

Achronix亮相2025全球AI芯片峰会

Achronix邀您相约2025全球AI芯片峰会

从 2D 到 3.5D 封装演进中焊材的应用与发展

Achronix Speedster7t FPGA芯片中2D NoC的设计细节

Achronix Speedster7t FPGA芯片中2D NoC的设计细节

评论