本文转载自:VagueCheung的博客

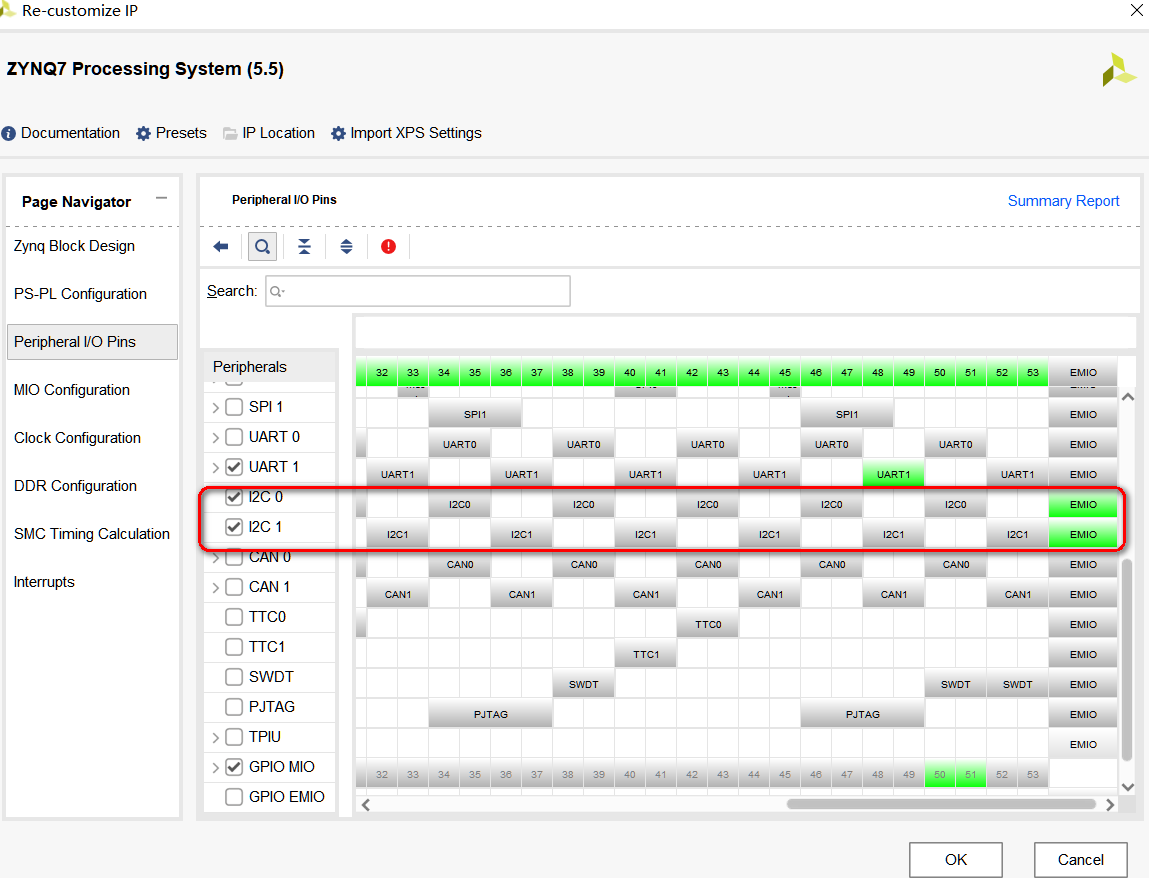

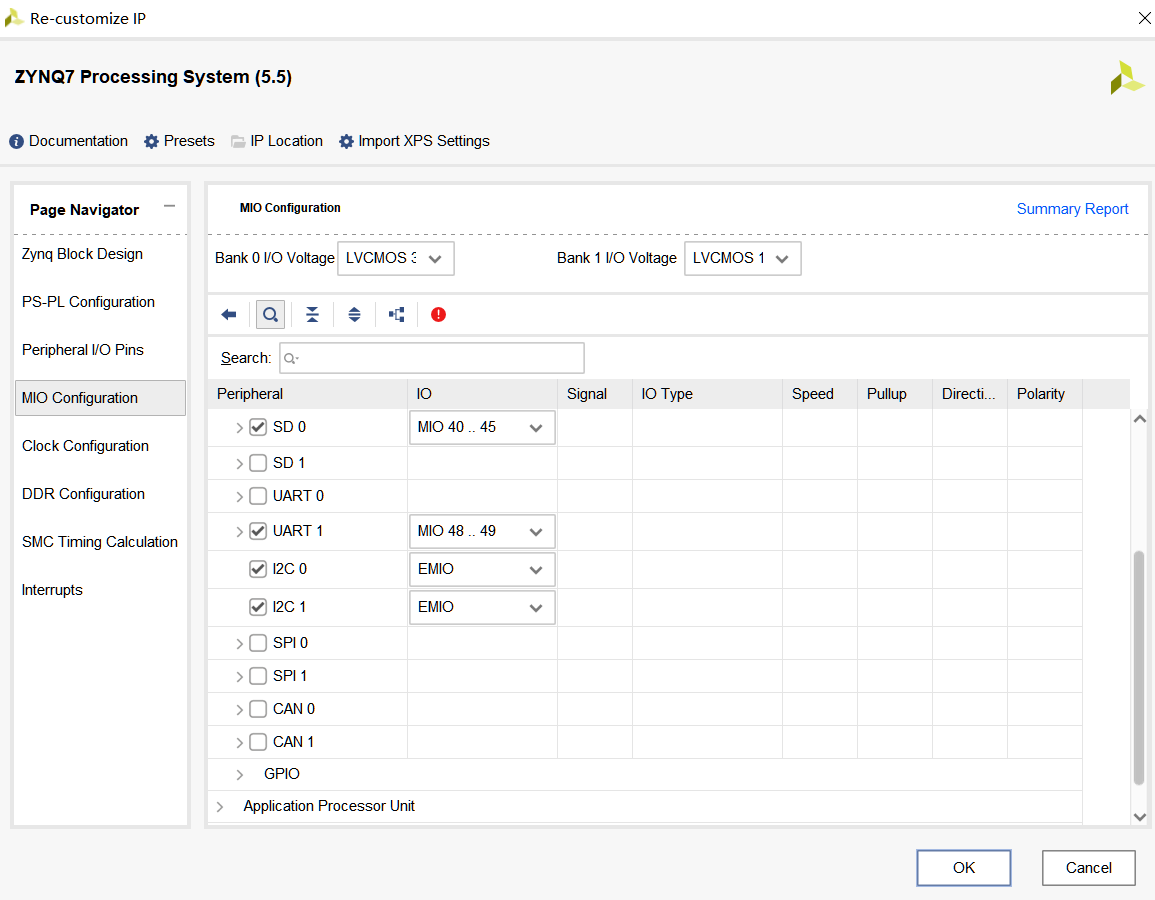

ZYNQ7000系列FPGA的PS自带两个IIC接口,接口PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35);

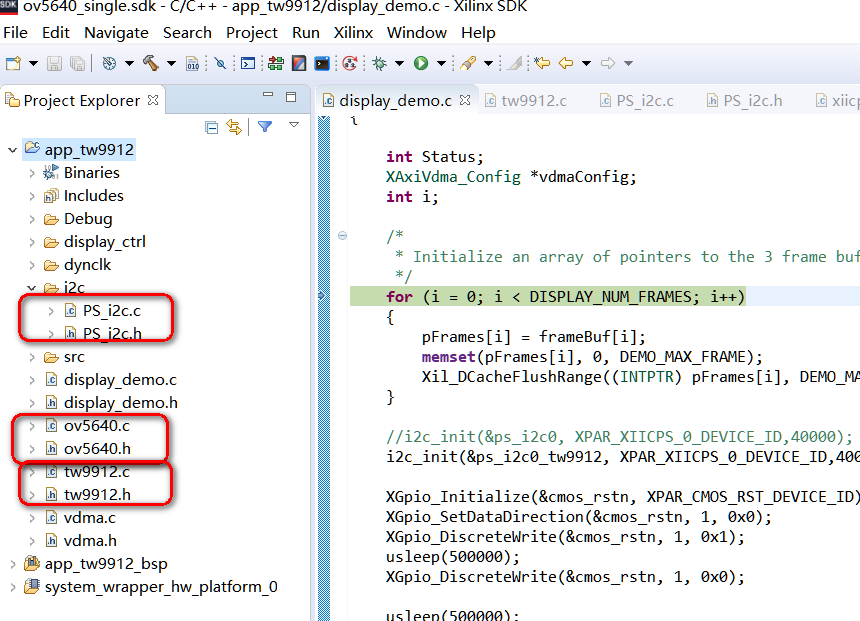

SDK中需要对IIC接口进行初始化在黑金和米联的例程里为了方便用户使用,对IIC和外设设备分别创建了相应的文件方便用户开发。

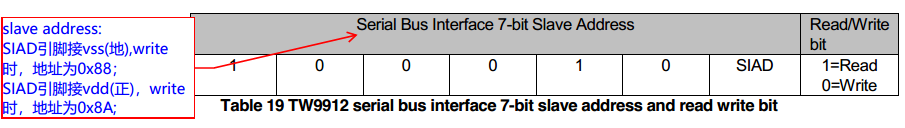

特别注意每个外设设备都会有自己的slave address;而xilinx官方给出的IIC驱动中给出的从设备的地址是7bit模式(IIC总线上的器件一般为8位地址位,去掉低位一位广播位,最多可挂载127个设备),在IIC进行写操作时注意要将设备原有的salve address转化成7bit模式;否则从设备将无法给予应答。

例如tw9912

在SDK中IIC进行写操作时。从设备地址slave address就应设置为0x44/0x45;

IIC总线数据传输速率(波特率)快速模式下可达到400kbit/s;

审核编辑 黄昊宇

-

IIC接口

+关注

关注

0文章

23浏览量

11969 -

Zynq-7000

+关注

关注

3文章

144浏览量

37885

发布评论请先 登录

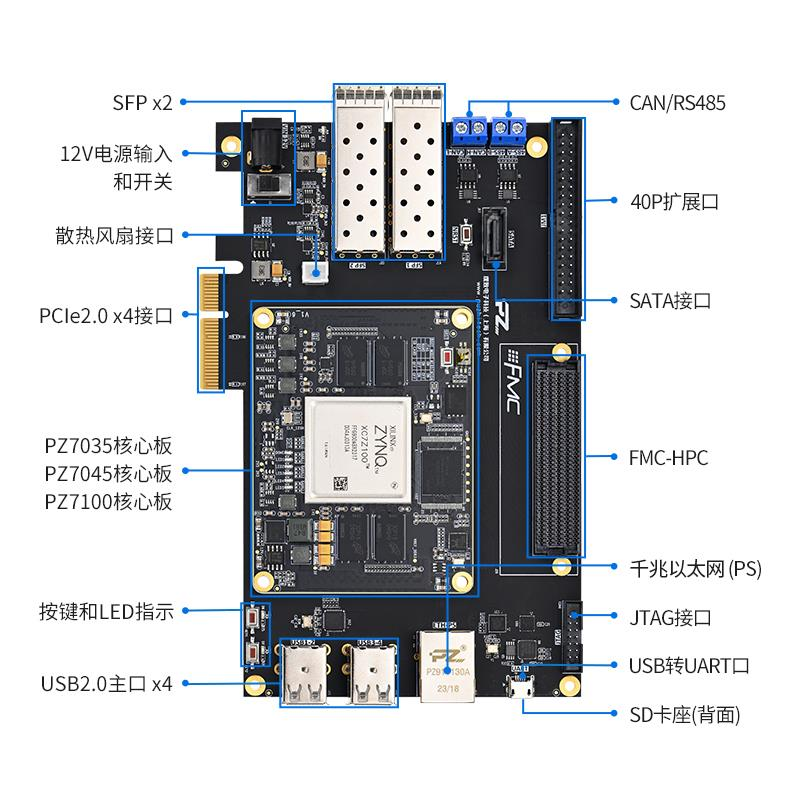

fpga开发板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板与开发板用户手册

Zynq-7000 SoC与7系列设备内存接口解决方案数据手册

Zynq7000处理器的配置详解

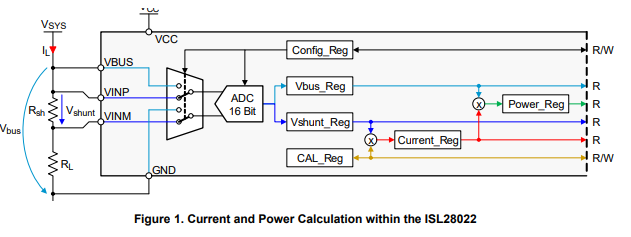

了解ISL28022的电流和功率计算应用笔记

Zynq-7000 PS端IIC接口使用笔记

Zynq-7000 PS端IIC接口使用笔记

评论