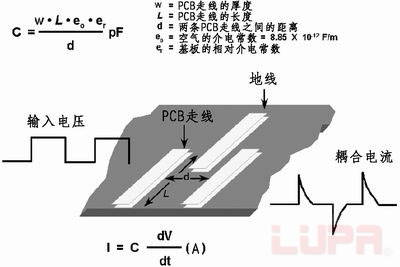

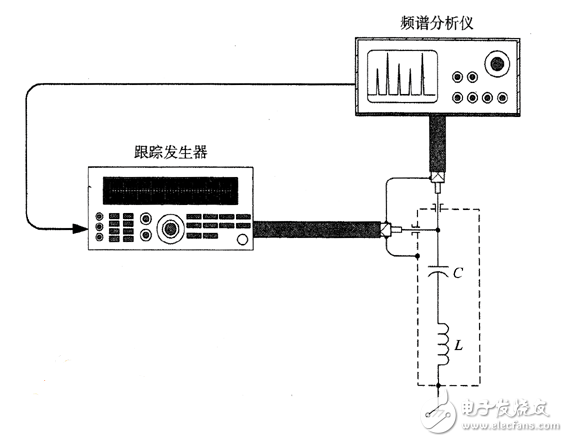

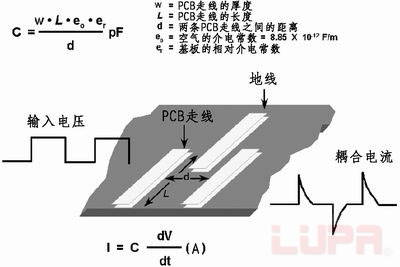

PCB布线设计时寄生电容的计算方法

在PCB上布两条靠近的走线,很容易产生寄生电容。由于这种寄生电容的存在,

2009-09-30 15:13:33 28853

28853

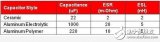

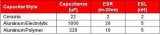

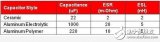

电源纹波和瞬态规格会决定所需电容器的大小,同时也会限制电容器的寄生组成设置。低频下,所有三种电容器均未表现出寄生分量,因为阻抗明显只与电容相关。

2013-03-14 11:12:33 1653

1653

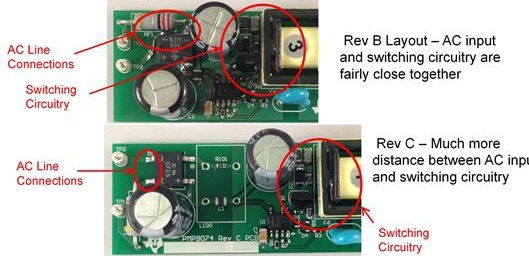

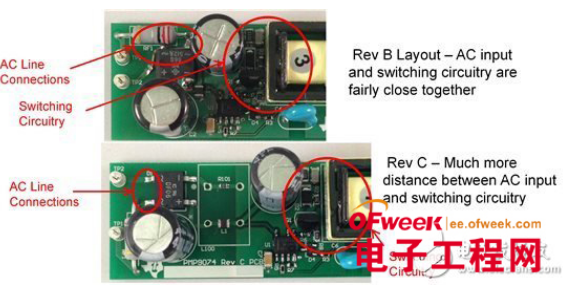

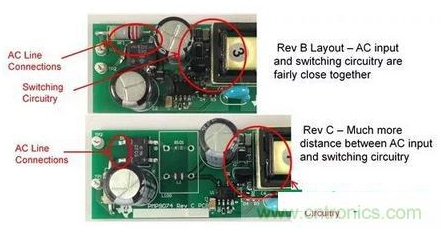

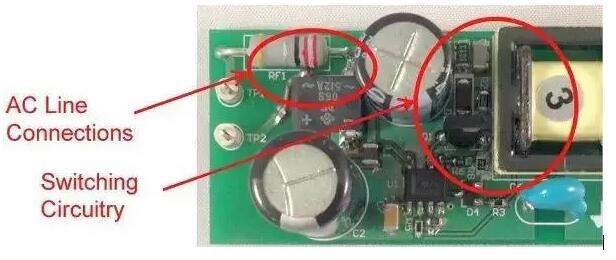

大部分传导 EMI 问题都是由共模噪声引起的。而且,大部分共模噪声问题都是由电源中的寄生电容导致的。

2014-06-19 13:44:02 2609

2609

在您的电源中很容易找到作为寄生元件的100fF电容器。您必须明白,只有处理好它们才能获得符合EMI标准的电源。

2016-01-14 17:52:06 1565

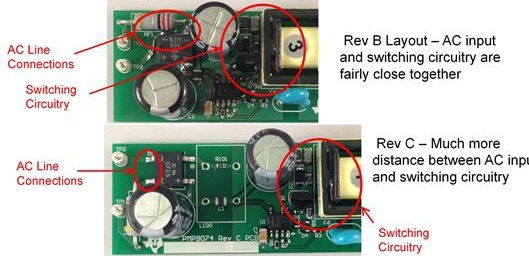

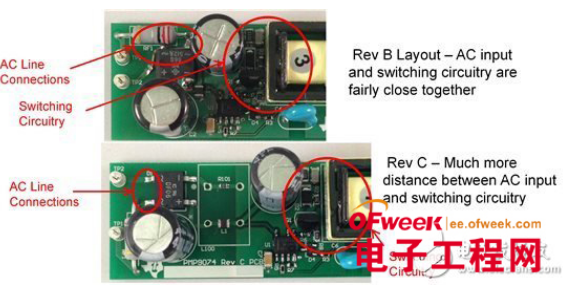

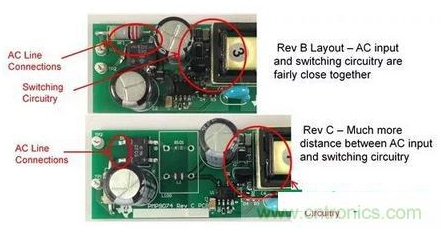

1565 大部分传导 EMI 问题都是由共模噪声引起的。而且,大部分共模噪声问题都是由电源中的寄生电容导致的。 对于该讨论主题的第 1 部分,我们着重讨论当寄生电容直接耦合到电源输入电线时会发生的情况 1.

2018-04-10 09:14:25 25129

25129

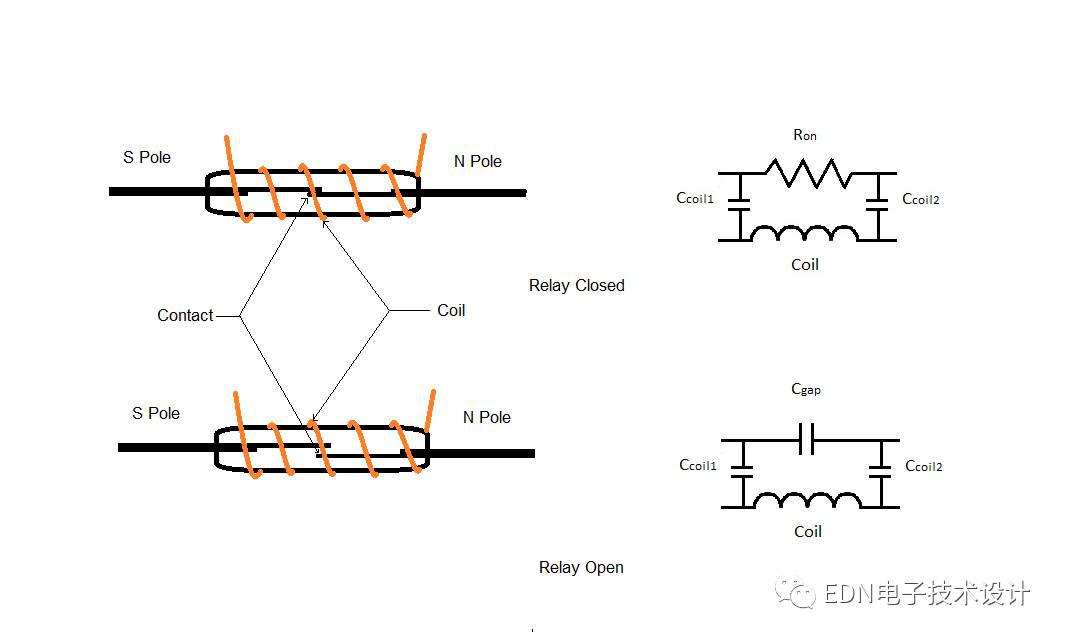

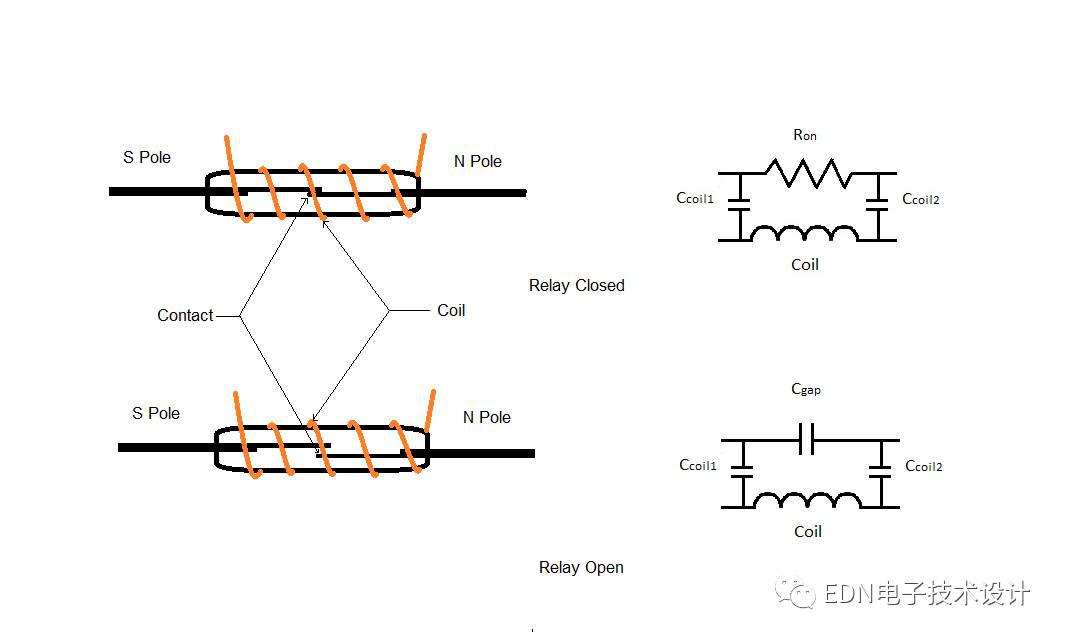

在被测点阻抗较高时,即使该点仅有较小的电容,其带宽也会受限。在基于磁簧继电器的多路选择器中,由于各磁簧继电器的寄生电容会在输出端并联,加大了输出端的电容,使得电路的带宽变窄。

2018-12-14 15:14:47 23983

23983

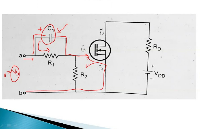

首先,我们介绍设计寄生电容对三极管产生的影响;然后,我们学习上拉电阻和下拉电阻的含义以及在电路中的使用方法。

2019-05-20 07:28:00 11072

11072

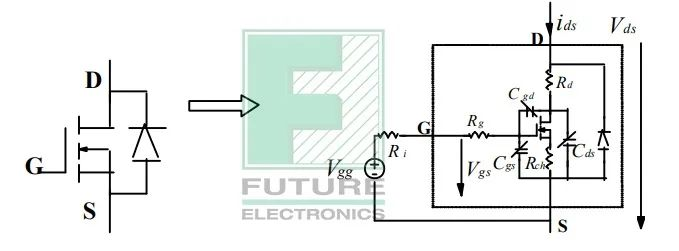

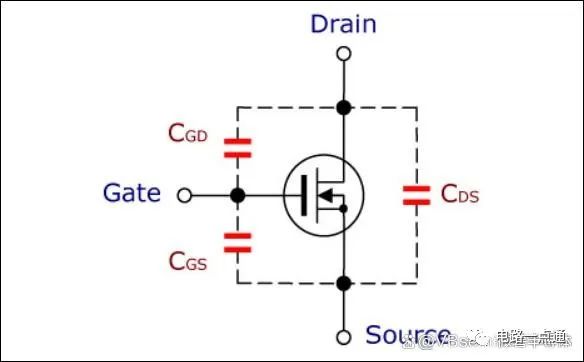

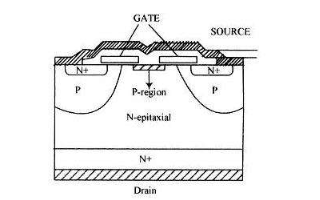

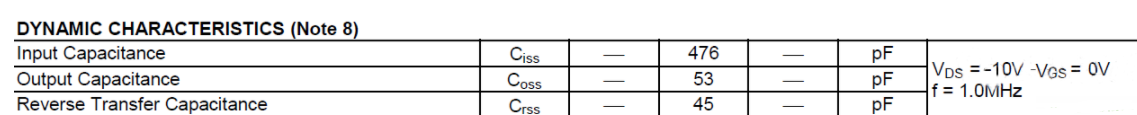

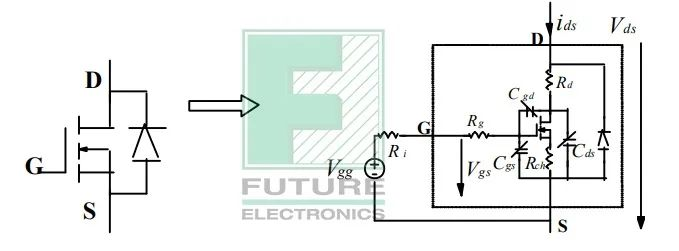

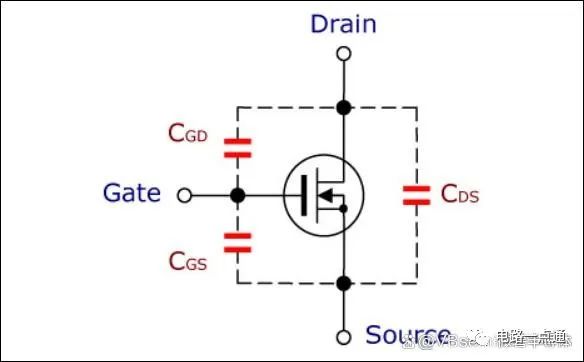

我们应该都清楚,MOSFET 的栅极和漏源之间都是介质层,因此栅源和栅漏之间必然存在一个寄生电容CGS和CGD,沟道未形成时,漏源之间也有一个寄生电容CDS,所以考虑寄生电容时,MOSFET

2021-01-08 14:19:59 19968

19968

在您的电源中很容易找到作为寄生元件的100fF电容器。您必须明白,只有处理好它们才能获得符合EMI标准的电源。

2022-08-04 14:39:22 817

817 在您的电源中很容易找到作为寄生元件的100fF电容器。只有处理好它们才能获得符合EMI标准的电源。

2023-01-11 10:33:59 778

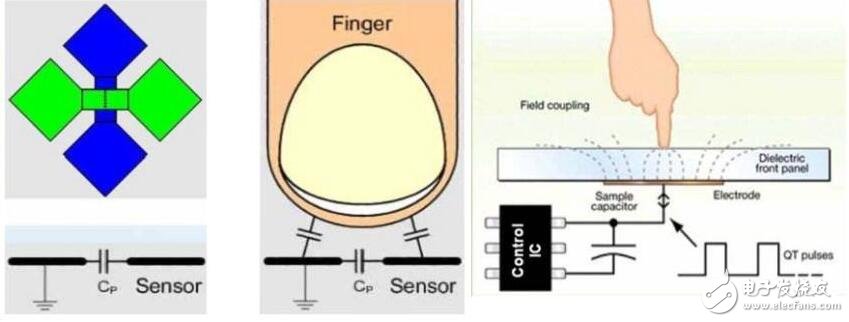

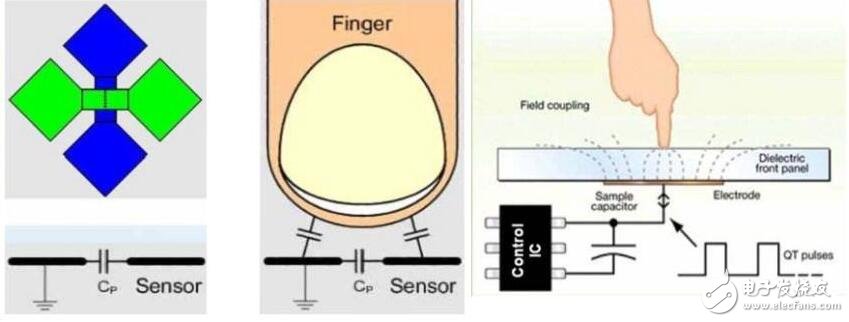

778 寄生电容有一个通用的定义:寄生电容是存在于由绝缘体隔开的两个导电结构之间的虚拟电容(通常不需要的),是PCB布局中的一种效应,其中传播的信号表现得好像就是电容,但其实并不是真正的电容。

2024-01-18 15:36:14 6180

6180

导读在汽车电子与工业控制等领域,CAN通信至关重要。本文围绕CAN通信,阐述节点增多时如何减少寄生电容的策略,同时从发送、接收节点等方面,讲解保障节点数量及通信可靠性的方法。如何减少寄生电容?增加

2025-01-03 11:41:51 3610

3610

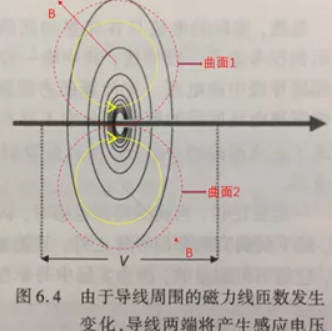

电子系统中的噪声有多种形式。无论是从外部来源接收到的,还是在PCB布局的不同区域之间传递,噪声都可以通过两种方法无意中接收:寄生电容和寄生电感。寄生电感相对容易理解和诊断,无论是从串扰的角度还是从板上不同部分之间看似随机噪声的耦合。

2025-03-17 11:31:39 2333

2333

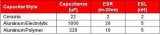

电源纹波和瞬态规格会决定所需电容器的大小,同时也会限制电容器的寄生组成设置。图1显示一个电容器的基本寄生组成,其由等效串联电阻(ESR)和等效串联电感(ESL)组成,并且以曲线图呈现出三种电容

2018-09-29 09:22:17

寄生电容一般是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,和一个电阻的串联,在低频情况下表现不是很明显,而在高频情况下,等效值会增大,不能忽略。

2019-09-29 10:20:26

寄生电容的影响是什么?焊接对无源器件性能的影响是什么?

2021-06-08 06:05:47

在您的电源中很容易找到作为寄生元件的100fF电容器。您必须明白,只有处理好它们才能获得符合EMI标准的电源。

2020-10-29 07:04:52

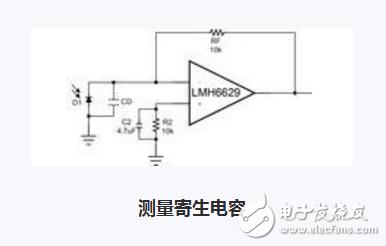

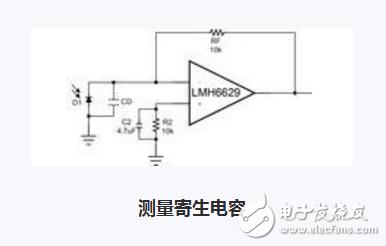

在LTC6268-10芯片手册中,为了减小寄生反馈电容的影响,采用反馈电阻分流的方式减小寄生电容。

请问,在这种工作方式下,为了使寄生电容降到最低,对电路板的材料类型和厚度有什么要求吗?

2023-11-16 06:28:44

MOSFET的工作波形。由于感性负载下,电流相位上会超前电压,因此保证了MOSFET运行的ZVS。要保证MOSFET运行在感性区,谐振电感上的谐振电流必须足够大,以确保MOSFET源漏间等效的寄生电容上存储

2018-11-21 15:52:43

感性负载下,电流相位上会超前电压,因此保证了MOSFET运行的ZVS。要保证MOSFET运行在感性区,谐振电感上的谐振电流必须足够大,以确保MOSFET源漏间等效的寄生电容上存储的电荷可以在死区时间内被

2018-07-13 09:48:50

PCB中电源部分如何处理?DDR的基本要求是什么啊 ?看了好多资料什么样的说法都有

2013-03-14 14:51:56

寄生电容是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,一个电阻的串联,低频情况下表现不明显,而高频情况下,等效值会增大。在计算中我们要考虑

2021-01-11 15:23:51

会使 EMI 辐射超出标准规定。在一些双线式设计中(无基底连接),解决这个问题尤其困难,因为有许多高阻抗被包含在内。解决这个问题的最佳方法是最小化寄生电容,并对开关频率实施高频脉动。频率更高时,电路其余部分的分散电容的阻抗变小,因此共模电感可以同时降低辐射发射和传导发射。

2011-12-20 09:21:36

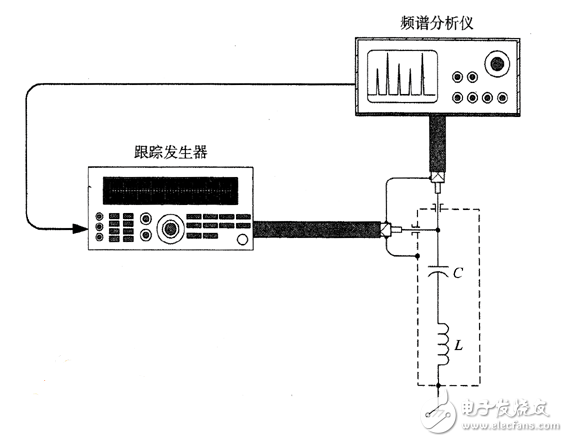

和寄生电容进行提取,但是TDR(时域反射)方法需要时域反射仪,用于样机建成后,这就使开发成本大大增加,而且TDR方法不能寻找到复杂结构中的耦合效应;然而FEA(有限元分析)方法则可以克服这一缺点,用于样机建成

2016-05-04 14:03:26

和直流母线的寄生参数。为了建立开关电源PCB的高频模型,需要对PCB的结构寄生参数进行抽取。提取PCB寄生参数的方法有很多,其中TDR(时域反射)方法可以在不知道实际几何形状的情况下对寄生电感和寄生电容

2016-04-20 16:25:31

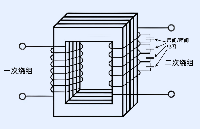

效率、增加无功功率,致使输出功率不稳定。在实际应用中,我们需要通过优化变压器设计、补偿无功功率以及增加功率稳定控制来有效降低寄生电容带来的不利影响。

森木磊石 PPEC inside 数字电源

2025-05-30 11:31:41

电源纹波和瞬态规格会决定所需电容器的大小,同时也会限制电容器的寄生组成设置。图1显示一个电容器的基本寄生组成,其由等效串联电阻(ESR)和等效串联电感(ESL)组成,并且以曲线图呈现出三种电容

2018-09-10 08:16:02

A流向B;VT关断后,寄生电容反向充电,充电电流由B流向A.这样,变压器中便产生了差模传导EMI.同时,电源元器件与大地之间的电位差也会产生高频变化。由于元器件与大地、机壳之间存在着分布电容,便产生

2018-09-27 15:17:42

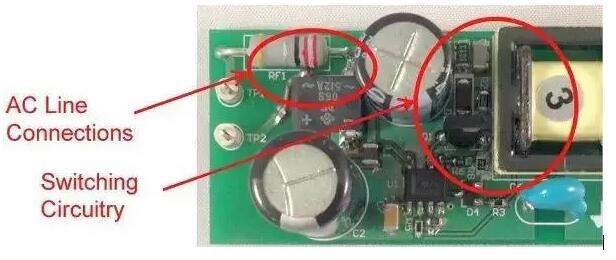

的电容会导致电源EMI签名超出规范要求。 如何处理好电源中的寄生电容才能获得符合EMI标准的电源图2. 寄生漏极电容导致超出规范要求的EMI性能这是一条令人关注的曲线,因为它反映出了几个问题:明显超出

2019-05-14 08:00:00

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。在本篇文章中,主要

2021-07-29 06:19:11

跨时钟域处理是什么意思?如何处理好跨时钟域间的数据呢?有哪几种跨时钟域处理的方法呢?

2021-11-01 07:44:59

如何才能确保电源系统符合FPGA要求?FPGA使用的电源类型是怎样的?FPGA的对电源有什么特殊要求?FPGA配电采取什么样的结构?

2021-04-08 06:55:46

在您的电源中很容易找到作为寄生元件的100fF电容器。您必须明白,只有处理好它们才能获得符合EMI标准的电源。 从开关节点到输入引线的少量寄生电容(100毫微微法拉)会让您无法满足电磁干扰(EMI

2019-10-18 10:21:50

作者:Brian King 大部分传导EMI 问题都是由共模噪声引起的。而且,大部分共模噪声问题都是由电源中的寄生电容导致的。对于该讨论主题的第 1 部分,我们着重讨论当寄生电容直接耦合到电源输入

2018-09-14 15:21:01

给大家分享一份资料教大家如何避免传导EMI问题(资深工程师电源设计资料)序: 大部分传导 EMI 问题都是由共模噪声引起的。而且,大部分共模噪声问题都是由电源中的寄生电容导致的。 我们着重讨论当

2016-01-14 14:15:55

在您的电源中很容易找到作为寄生元件的100fF电容器。您必须明白,只有处理好它们才能获得符合EMI标准的电源。 从开关节点到输入引线的少量寄生电容(100毫微微法拉)会让您无法满足电磁干扰

2018-10-23 16:01:01

在您的电源中很容易找到作为寄生元件的100fF电容器。您必须明白,只有处理好它们才能获得符合EMI标准的电源。从开关节点到输入引线的少量寄生电容(100毫微微法拉)会让您无法满足电磁干扰(EMI

2021-10-21 09:34:21

。这些寄生电容的分布如图4所示。在初级回路中,功率开关管芯片、PWM控制芯片、运算放大器芯片、电源正负输入线的走线轨迹等都会与外壳底板之间产生寄生电容Cp,寄生电容的容量大小取决于基片的厚度和它们在底板

2018-11-21 16:24:32

环境越来越复杂,其电磁兼容问题成为电源设计中的一大重点,同时也成为电源设计工作的一大难点。常规设计方法中,依靠经验设计处理EMC问题,样机建立完毕之后才能对EMC问题做最后的考虑。传统的EMC的补救办法

2011-11-01 17:56:53

大部分传导 EMI 问题都是由共模噪声引起的。而且,大部分共模噪声问题都是由电源中的寄生电容导致的。对于该讨论主题的第 1 部分,我们着重讨论当寄生电容直接耦合到电源输入电线时会发生的情况1. 只需

2022-11-22 07:29:30

贴片晶振的PCB layout需要注意哪些晶振相邻层挖空是如何控制寄生电容Cp的呢?为什么温度会影响晶振频率呢?

2021-02-26 07:43:28

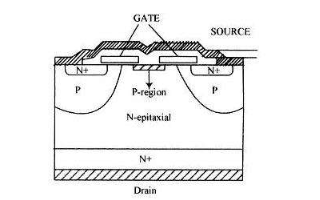

VDMOS的基本原理一种减小寄生电容的新型VDMOS结构介绍

2021-04-07 06:58:17

和PCB布局过程中,对寄生电容、杂散电容和分布电容的考虑和处理是至关重要的。特别是在处理高频信号如晶振时钟信号时,通过上述措施可以有效减小这些电容效应对电路性能的影响,提高系统的稳定性和可靠性。设计师们应充分了解这些电容特性,为电路设计提供有力保障。

2024-09-26 14:49:27

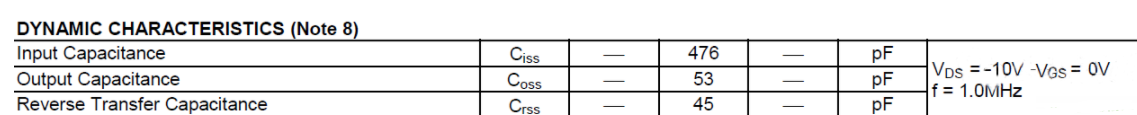

也是基于电容的特性,下面将从结构上介绍这些寄生电容,然后理解这些参数在功率MOSFET数据表中的定义,以及它们的定义条件。1、功率MOSFET数据表的寄生电容沟槽型功率MOSFET的寄生电容的结构如图

2016-12-23 14:34:52

`磁芯对电感寄生电容的影响`

2012-08-13 15:11:07

`磁芯对电感寄生电容的影响`

2012-08-14 09:49:47

`资深工程师电源设计策略:如何避免传导EMI问题大部分传导 EMI 问题都是由共模噪声引起的。而且,大部分共模噪声问题都是由电源中的寄生电容导致的。 我们着重讨论当寄生电容直接耦合到电源输入电线

2014-07-30 11:06:54

为影响 EMI 和开关行为的功率 MOSFET 输入电容、输出电容和反向传输电容三者之间的关系表达式(以图 2 中的终端电容符号表示)。在 MOSFET 开关转换期间,这种寄生电容需要幅值较高的高频

2020-11-03 07:54:52

检验具有高转换率电流的关键回路寄生组分和辐射EMI功率级寄生电容EMI频率范围和耦合模式

2021-02-24 08:01:34

听到斯斯声,感觉是电源和地没有处理好,调试尝试就是在电源接入的地方接一个220UF的电解电容,接磁珠接到PVCC,地还是不知道怎么处理合适,手册的意思是说引脚AGND和PGND和滤波电容的地接在中心焊

2019-04-04 09:51:28

的反偏压结电容,可以合理地降低电源线上的连接寄生电容,这儿近一步探讨这一应用,来分析下“二极管如何降低寄生电容?”。二极管参数——结电容在一些高速场合,需要选结电容比较小的二极管;在某些场合,则需

2020-12-15 15:48:52

铁氧体电感器在较高频率时可等效为“电阻、电感”的串联支路与一寄生电容的并联,该电容的存在对电感器的高频性能有重要影响。本文建立了铁氧体环形电感器2D平行平面场和3D

2009-04-08 15:45:17 66

66 一种减少VDMOS寄生电容的新结构

0 引 言 VDMOS与双极晶体管相比,它的开关速度快,开关损耗小,输入电阻高,驱动

2010-01-11 10:24:05 2089

2089 寄生电容,寄生电容是什么意思

寄生的含义 寄身的含义就是本来没有在那个地方设计电容,但由于布线构之间总是有互容,互

2010-03-23 09:33:55 3188

3188 电磁干扰EMI中电子设备产生的干扰信号是通过导线或公共电源线进行传输,互相产生干扰称为传导干扰。传导干扰给不少电子工程师带来困惑,如何解决传导干扰?这里,我们先着重讨论当寄生电容直接耦合到电源输入

2018-05-18 01:17:00 3518

3518

大部分传导 EMI 问题都是由共模噪声引起的。而且,大部分共模噪声问题都是由电源中的寄生电容导致的。对于该讨论主题的第 1 部分,我们着重讨论当寄生电容直接耦合到电源输入电线时会发生的情况 1. 只需几 fF 的杂散电容就会导致 EMI 扫描失败。

2017-04-18 14:34:32 919

919

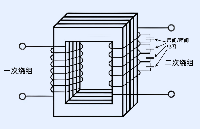

条件周期不稳定。这种影响是非常高的加剧电压设计。重视变压器设计将治愈这个问题。 图2显示了高频电流路径的寄生电容。在操作假设分析中输入和输出电压在交流地。因此,该寄生电容并联。变压器的次级提供这些电容器的交流

2017-05-02 14:15:40 19

19 在您的电源中很容易找到作为寄生元件的100fF电容器。您必须明白,只有处理好它们才能获得符合EMI标准的电源。 从开关节点到输入引线的少量寄生电容(100 毫微微法拉)会让您无法满足电磁干扰(EMI

2017-11-15 10:59:08 1

1 寄生电容一般是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,和一个电阻的串连,在低频情况下表现不是很明显,而在高频情况下,等效值会增大,不能忽略。

2018-01-31 10:09:29 23654

23654

寄生电容一般是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,和一个电阻的串连,在低频情况下表现不是很明显,而在高频情况下,等效值会增大,不能忽略。

2018-01-31 10:57:56 29458

29458 电容的寄生电感和寄生电阻主要是指它的引线和极板形成的电感和电阻,尤其是容量较大的电容更为明显。如果你解剖过电容器,会看到它的极板是用长达1米的金属薄膜卷曲而成的,其层状就像一个几十、甚至上百圈的线圈

2018-01-31 13:44:55 45254

45254

这是一条令人关注的曲线,因为它反映出了几个问题:明显超出了规范要求的较低频率辐射、共模问题通常很明显的1MHz至2MHz组件,以及较高频率组件的衰减正弦(x)/x分布。

2018-05-06 08:25:45 7137

7137

ADI公司的Matt Duff讲解为什么运算放大器反相引脚的寄生电容会引起不稳定。

2019-06-11 06:11:00 6052

6052 1. 只需几fF的杂散电容就会导致EMI扫描失败。从本质上讲,开关电源具有提供高 dV/dt 的节点。寄生电容与高 dV/dt 的混合会产生 EMI 问题。在寄生电容的另一端连接至电源输入端时,会有少量电流直接泵送至电源线。

2019-04-19 15:24:30 2942

2942

本文首先介绍了寄生电容的概念,其次介绍了寄生电容产生的原因,最后介绍了寄生电容产生的危害。

2019-04-30 15:39:37 31576

31576 分布电容强调的是均匀性。寄生跟强调的是意外性,指不是专门设计成电容,却有着电容作用的效应,比如三极管极间电容。单点说,两条平行走线之间会产生分布电容,元器件间在高频下表现出来的容性叫寄生电容。

2019-04-30 15:56:30 22626

22626

减小电感寄生电容的方法

如果磁芯是导体,首先:

用介电常数低的材料增加绕组导体与磁芯之间的距离

2019-07-18 08:00:00 2

2 寄生电感一半是在PCB过孔设计所要考虑的。在高速数字电路的设计中,过孔的寄生电感带来的危害往往大于寄生电容的影响。它的寄生串联电感会削弱旁路电容的贡献,减弱整个电源系统的滤波效用。我们可以用下面的公式来简单地计算一个过孔近似的寄生电感。

2019-10-11 10:36:33 21439

21439 目前,大部分传导EMI问题都是由共模噪声引起的。而且,大部分共模噪声问题都是由电源中的寄生电容导致的。

2019-12-03 16:29:20 2880

2880

在电源中很容易找到作为寄生元件的100fF电容器。所以必须明白,只有处理好它们才能获得符合EMI标准的电源。

2020-08-31 15:13:23 1112

1112

寄生的含义就是本来没有在那个地方设计电容,但由于布线之间总是有互容,互容就好像是寄生在布线之间的一样,所以叫寄生电容,又称杂散电容。

2020-09-17 11:56:11 33093

33093 寄生电容是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,一个电阻的串联,低频情况下表现不明显,而高频情况下,等效值会增大。在计算中我们要考虑进去。

2020-10-09 12:04:17 37464

37464 注意,漏极连接与输入引线之间有一些由输入电容器提供的屏蔽。该电容器的外壳连接至主接地,可为共模电流提供返回主接地的路径。如图2所示,这个微小的电容会导致电源EMI签名超出规范要求。

2020-10-26 15:53:49 2376

2376

AN39-升压变压器设计中的寄生电容效应

2021-04-28 17:42:25 5

5 作者:Brian King

大部分传导 EMI 问题都是由共模噪声引起的。而且,大部分共模噪声问题都是由电源中的寄生电容导致的。

对于该讨论主题的第 1 部分,我们着重讨论当寄生电容直接耦合

2021-11-23 11:03:02 1551

1551 的,今天我们就来讲解一下,对于理想的MOS器件来说,我们只考虑器件本身,而不考虑MOS的寄生电容的话,那么是无需考虑驱动电流的大小的。相信大家都听过一个名词,叫寄生电容,也叫杂散电容,是电路中电子元件

2022-04-07 09:27:12 8403

8403

本来没有在那个地方设计电容,但由于布线之间总是有互容,互容就好像是寄生在布线之间的一样,所以叫寄生电容 寄生电容: 本质上还是电容,满足i=c*du/dt。 电容是用来衡量储存电荷能力的物理量。根据

2022-07-27 14:23:55 19876

19876

继前篇的Si晶体管的分类与特征、基本特性之后,本篇就作为功率开关被广为应用的Si-MOSFET的特性作补充说明。MOSFET的寄生电容:MOSFET在结构上存在下图所示的寄生电容。

2023-02-09 10:19:24 4953

4953

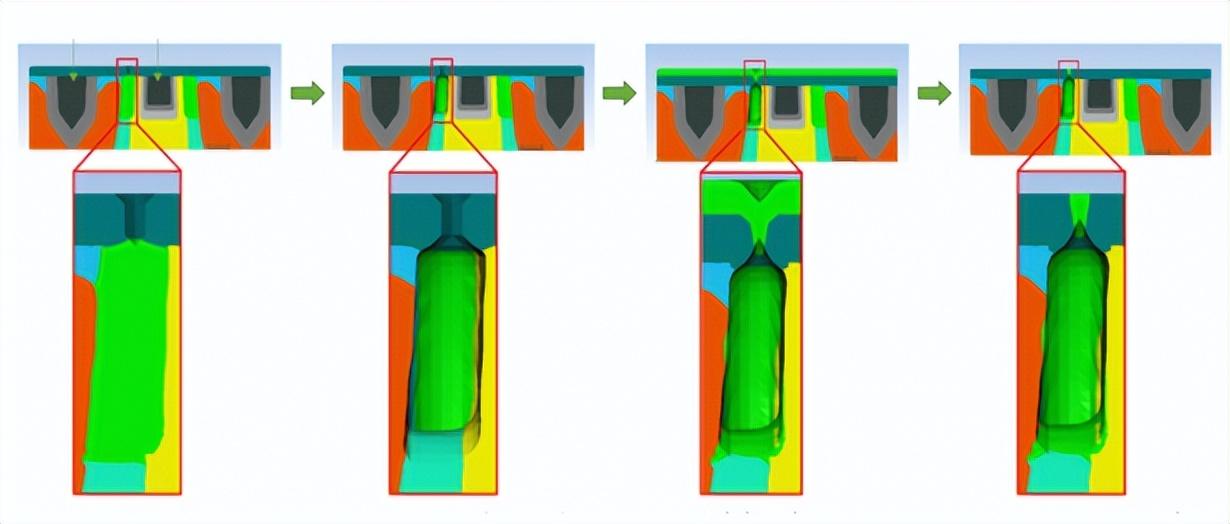

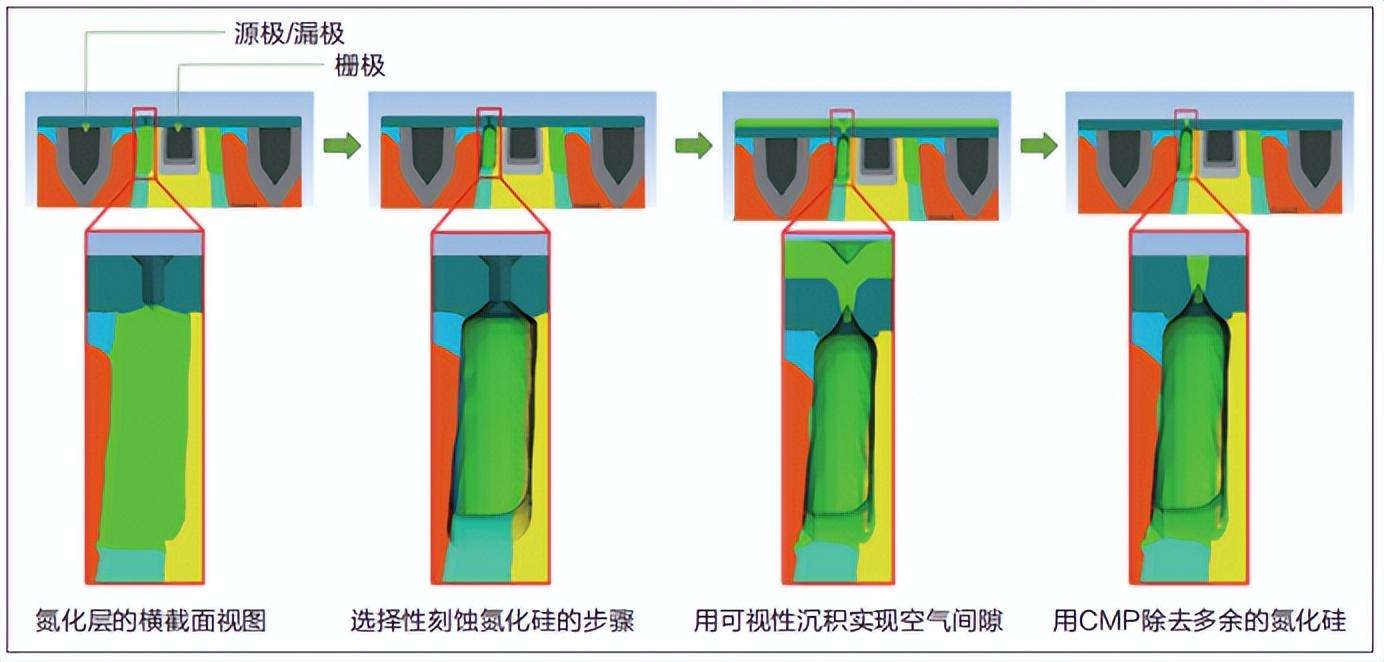

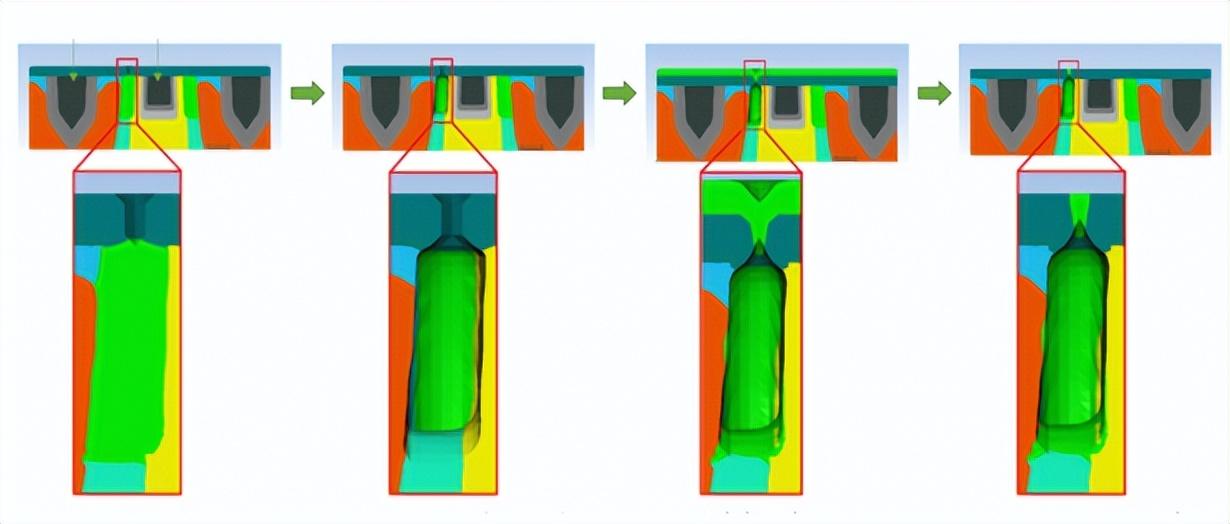

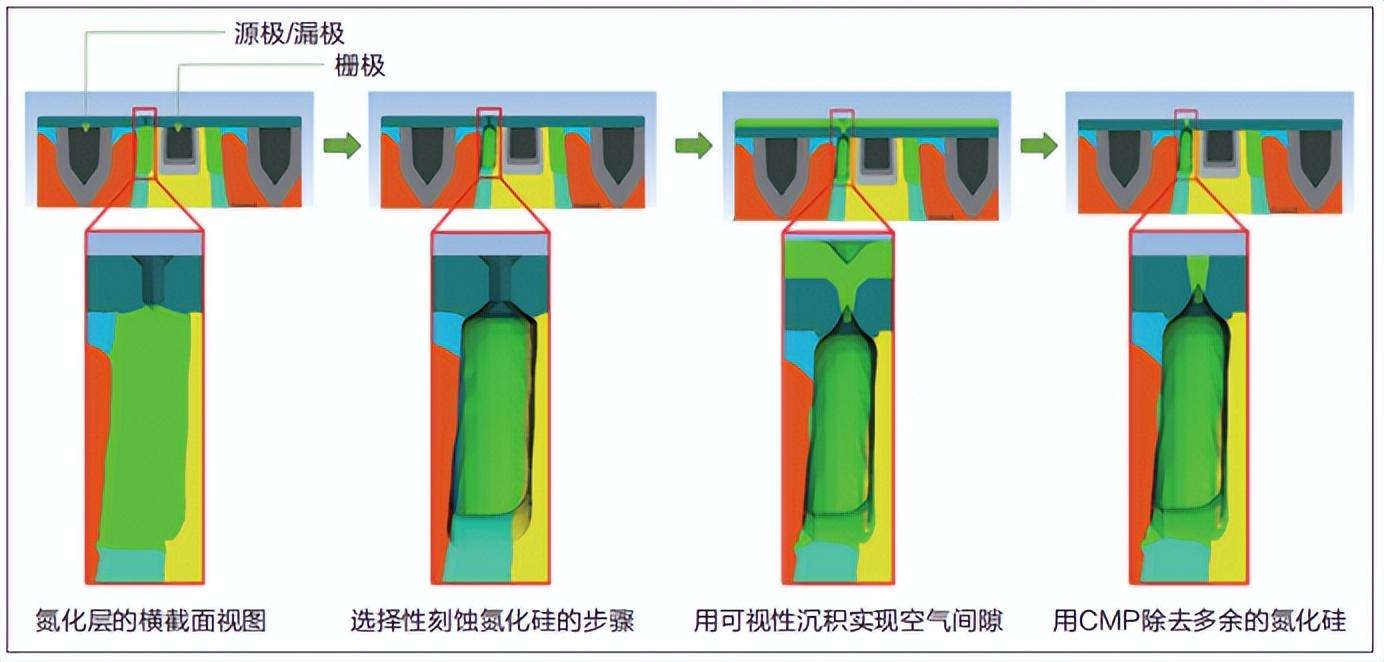

可以减少器件的开关延迟。减少寄生电容的方法之一是设法降低栅极和源极/漏极之间材料层的有效介电常数,这可以通过在该位置的介电材料中引入空气间隙来实现。这种类型的方式过去已经用于后道工序 (BEOL) 中,以减少金属互连之间的电容 [1-4]。本文中,我们将专注于前道工序 (FEOL

2023-03-28 17:19:08 4118

4118

和晶体管的源极/漏极接触之间的寄生电容可以减少器件的开关延迟。减少寄生电容的方法之一是设法降低栅极和源极/漏极之间材料层的有效介电常数,这可以通过在该位置的介电材料中引入空气间隙来实现。这种类型的方式过去已经用于后道工序(BEOL)中,以减少金属互连之间的电容[1-4]。本文中,

2023-06-02 17:31:46 1072

1072

在您的电源中很容易找到作为寄生元件的100fF电容器。您必须明白,只有处理好它们才能获得符合EMI标准的电源。

2023-06-13 11:13:12 1636

1636

巨大的麻烦或导致严重的健康问题。当然,作为一个PCB设计人员,您可能知道另一种寄生虫—寄生电容。虽然您不必担心电路中的生物寄生,但了解如何消除寄生电容可以帮助提高P

2022-05-31 11:09:01 5360

5360

使用Coventor SEMulator3D®创建可以预测寄生电容的机器学习模型

2023-07-06 17:27:02 864

864

寄生电容有一个通用的定义:寄生电容是存在于由绝缘体隔开的两个导电结构之间的虚拟电容(通常不需要的),是 PCB 布局中的一种效应,其中传播的信号表现得好像就是电容,但其实并不是真正的电容。

2023-07-24 16:01:36 16203

16203

在您的电源中很容易找到作为寄生元件的100fF电容器。您必须明白,只有处理好它们才能获得符合EMI标准的电源。

2023-07-27 10:36:12 820

820

电容可能会对电路的性能和稳定性产生影响。因此,在 PCB 布线设计中,充分了解寄生电容的产生原因和处理方法是非常必要的。 什么是 PCB 连线寄生电容 维基百科上对于 PCB 连线寄生电容的定义是“由于 PCB 上信号线之间的相互耦合而导致的电容效应”。

2023-08-27 16:19:44 3749

3749 寄生电容对MOS管快速关断的影响 MOS(Metal Oxide Semiconductor)管是一种晶体管,它以其高性能和可靠性而广泛应用于许多电子设备,如功率放大器和开关电源。尽管MOS管具有

2023-09-17 10:46:58 5125

5125 SiC MOSFET 和Si MOSFET寄生电容在高频电源中的损耗对比

2023-12-05 14:31:21 1731

1731

寄生电容和寄生电感是指在电路中存在的非意图的电容和电感元件。 它们通常是由于电路布局、线路长度、器件之间的物理距离等因素引起的。

2024-02-21 09:45:35 4596

4596

电源纹波和瞬态规格会决定所需电容器的大小,同时也会限制电容器的寄生组成设置。

2024-03-17 15:45:39 23658

23658

显著的影响。本文将探讨普通探头和差分探头的寄生电容及其对测试波形的影响。 1. 探头寄生电容概述 寄生电容是指在探头设计中无意间形成的电容,它通常由探头的物理结构和材料特性决定。在普通探头中,寄生电容主要来源于探头的接地线

2024-09-06 11:04:37 1503

1503 本文介绍了半大马士革工艺:利用空气隙减少寄生电容。 随着半导体技术的不断发展,芯片制程已经进入了3纳米节点及更先进阶段。在这个过程中,中道(MEOL)金属互联面临着诸多新的挑战,如寄生电容等

2024-11-19 17:09:31 2399

2399

开关电源的EMI(电磁干扰)和EMC(电磁兼容)测试标准是确保开关电源产品符合电磁兼容性要求的重要依据。以下是一些常见的开关电源EMI/EMC测试标准: 一、EMI测试标准 传导发射测试 : 测试

2024-11-20 10:43:15 5986

5986 寄生电容会对充电机输出功率产生显著影响。一、变压器寄生电容的产生原因?变压器的寄生电容主要包括初级与次级绕组之间的分布电容、绕组层间电容及匝间电容。其成因可归纳为以下

2025-05-30 12:00:00 1319

1319

电子发烧友App

电子发烧友App

评论