来源:《半导体芯科技》杂志

作者:Sumant Sarkar, 泛林集团半导体工艺与整合工程师

使用Coventor SEMulator3D® 创建可以预测寄生电容的机器学习模型

减少栅极金属和晶体管的源极/漏极接触之间的寄生电容可以减少器件的开关延迟。减少寄生电容的方法之一是设法降低栅极和源极/漏极之间材料层的有效介电常数,这可以通过在该位置的介电材料中引入空气间隙来实现。这种类型的方式过去已经用于后道工序(BEOL)中,以减少金属互连之间的电容[1-4]。本文中,我们将专注于前道工序(FEOL),并演示在栅极和源极/漏极之间引入空气间隙的SEMulator3D®模型[5]。

SEMulator3D®是一个虚拟的制造软件平台,可以在设定的半导体工艺流程内模拟工艺变量。利用SEMulator3D®设备中的实验设计(DoE)功能,我们展示了寄生电容与刻蚀深度和其他用于制作空气间隙的刻蚀工艺参数的相关性,以及它与空气间隙大小和体积的相关性。

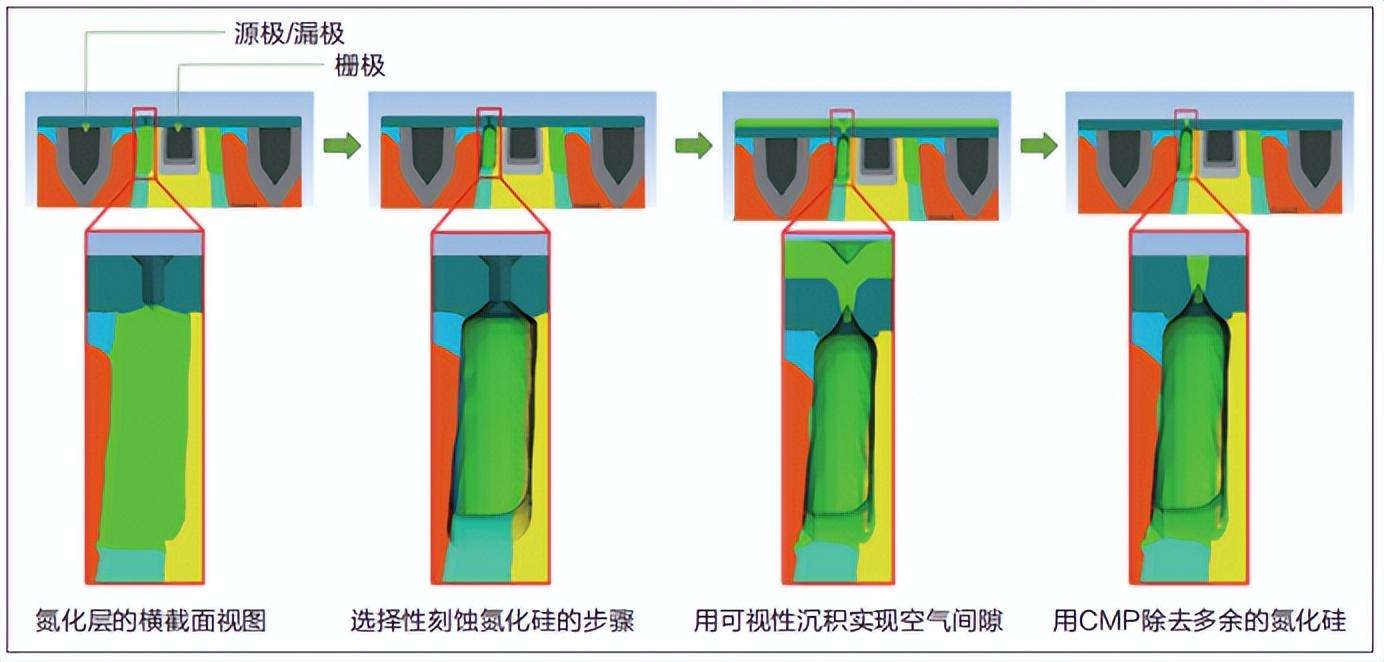

图1显示了SEMulator3D®FinFET模型的横截面。为了在FinFET的栅极和源极/漏极之间引入空气间隙,我们进行了高选择比的氮化硅刻蚀工艺,然后进行经过优化的氮化硅沉积工艺,以封闭结构并产生空气间隙结构。接着用氮化硅CMP(化学机械抛光)工艺对表面进行平坦化处理。

△图1:在FinFET模型中引入空气间隙的SEMulator3D工艺流程。可视性沉积的步骤通过在顶端夹止的方式产生空气间隙,然后进行CMP步骤除去多余的氮化硅。空气间隙减少了栅极和源极/漏极之间的寄生电容。空气间隙的大小可以通过改变刻蚀反应物的刻蚀深度、晶圆倾角和等离子体入射角度分布来控制。

使用SEMulator3D的虚拟测量功能测量以下指标:

1.栅极金属和源极/漏极之间的寄生电容

2.空气间隙的体积

3.空气间隙z轴的最小值,代表空气间隙的垂直尺寸

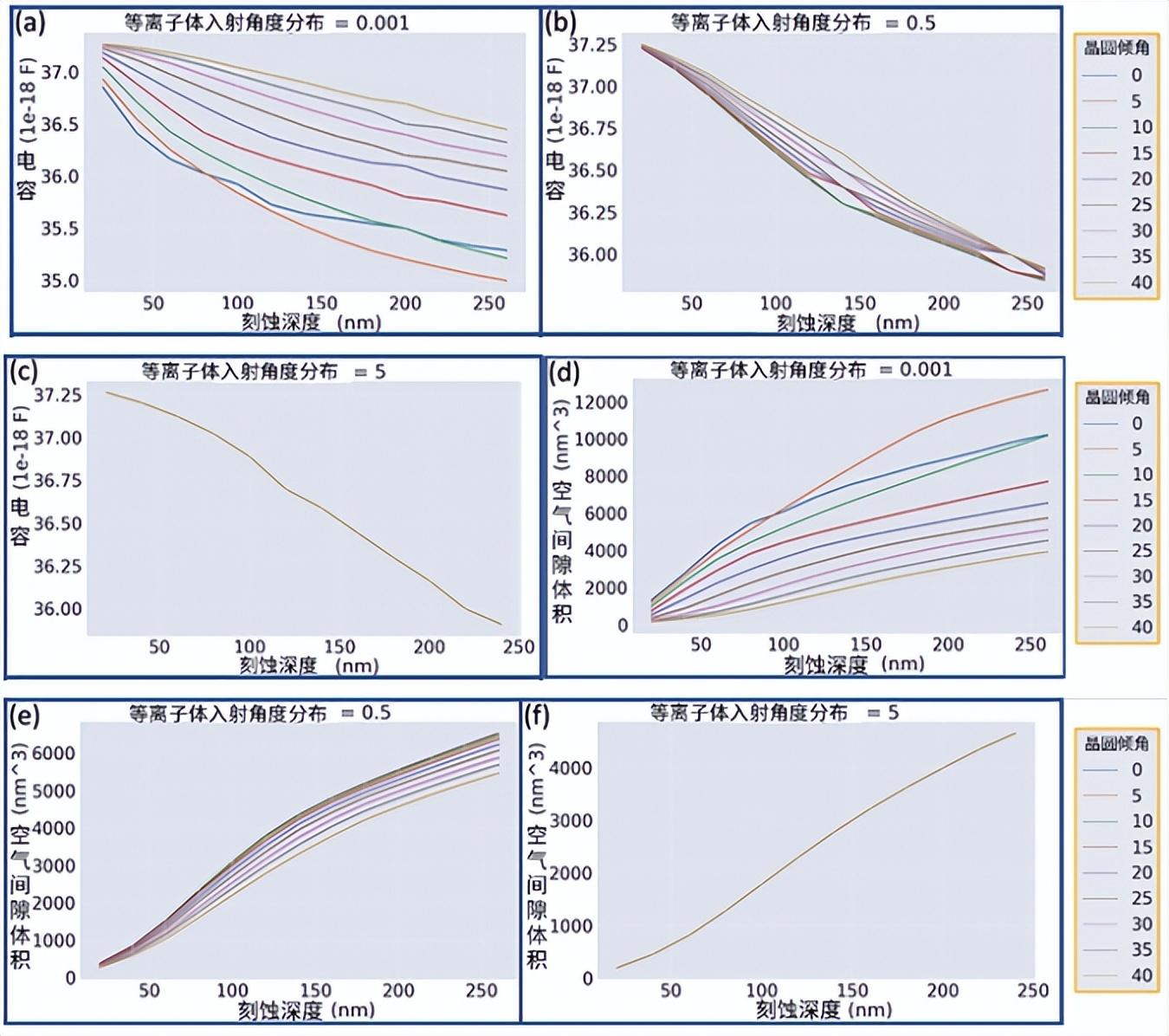

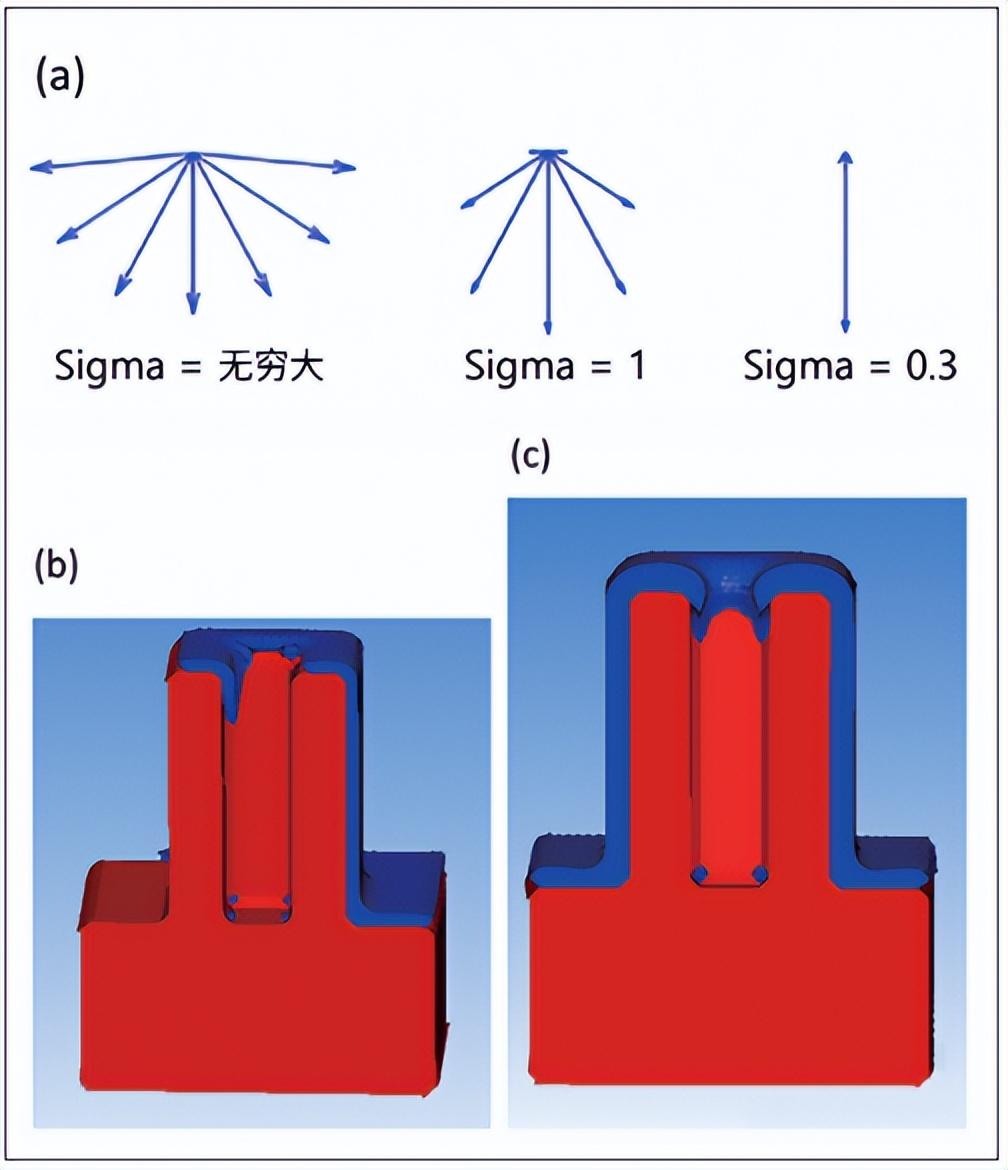

在氮化硅刻蚀步骤中,刻蚀深度、刻蚀反应物等离子体入射角度分布(在文献中称为等离子体入射角度分布)和晶圆倾角(假定晶圆旋转)在实验设计期间是变化的。图2a-f显示了在不同的晶圆倾角和等离子体入射角度分布值下,电容和空气间隙的体积如何跟随刻蚀深度发生变化。随着刻蚀深度的增加,产生的空气间隙也变大(图2d)。因为空气的介电常数比氮化物要低很多,所以这降低了有效的介电常数。相应地,栅极和源极/漏极之间的寄生电容就减小了。倾斜角减小会将刻蚀反应物从侧壁移开,并将其推向所产生的空气间隙底部(图3b-c)。这解释了为什么在给定的深度和等离子体入射角度分布值下,晶圆倾角越小,空气间隙越大,电容越小(图2a&d)。另一个重要的结果是,等离子体入射角度分布的增加会导致晶圆倾角影响减弱。当等离子体入射角度分布设置为5度(对应较宽/等向性的角分散)的时候,晶圆倾角对电容和空气间隙体积完全没有影响(图2c&f)。这与等离子体入射角度分布增加对刻蚀的影响是一致的。等离子体入射角度分布增加会使刻蚀反应物更等向性地轰击基板(图3a)。这意味着相比等离子体入射角度分布值低的时候,晶圆倾角不再影响刻蚀行为。

△图2:随着刻蚀深度增加,空气间隙体积增大,寄生电容减少(图2a&d)。随着晶圆倾角降低,这种下降更为急剧。但晶圆倾角的影响随着等离子体入射角度分布的增加而减小,当等离子体入射角度分布为5度时,晶圆倾角对电容和空气间隙体积没有影响(图2c&f)。

△图3:(a)角分散(sigma)对刻蚀反应物方向性的影响;(b)45度晶圆倾角的影响(晶圆被固定);(c)80度晶圆倾角的影响(晶圆旋转)。图片来源:SEMulator3D产品文档

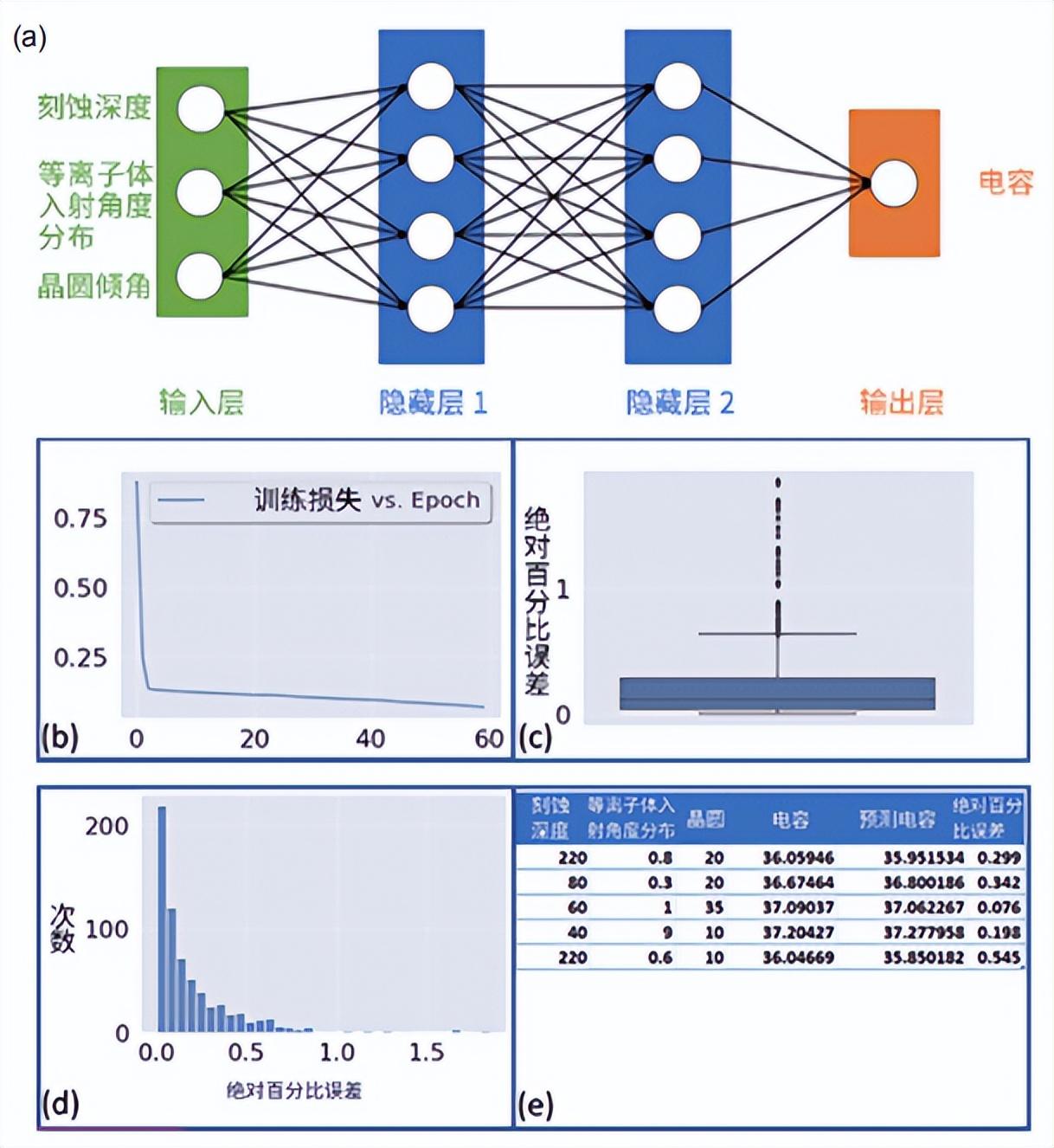

运行大型的实验设计需要消耗很多时间和算力资源。但这在工艺优化中很有必要——实验设计参数空间上的任何减少都有助于减少所需的时间和资源。能够基于自变量预测结果的机器学习模型非常有用,因为它能减少为所有自变量组合进行实验设计的需求。为了这一目标,将从实验设计中收集到的数据分成训练集(70%)和测试集(30%),然后将其输入人工神经网络(ANN)。该模型有两个隐藏层(图4a),用网格搜索法进行超参数调优。该模型在测试数据上运行,发现其平均准确度为99.8%。四分之三测试集的绝对百分比误差(APE)为0.278%及以下(图4c)。图4e显示了预测和实际寄生电容的测试行样本。这种机器学习的应用使我们能够降低实验设计的规模,减少所需时间。我们可以大幅减小参数空间,与此同时并没有明显降低结果的准确性。在我们的案例中,实验设计的规模从~5000减少到~2000个参数组合。SEMulator3D的自定义python步骤将这种类型的机器学习代码整合到工艺模拟中,其结果可以导入半导体工艺模型的下一个步骤。

△图4:根据刻蚀深度、晶圆倾角和等离子体入射角度分布来预测寄生电容的人工神经网络(ANN)模型。测试数据的预测准确度为99.8%。衡量预测电容和实际电容之间差异的指标是绝对百分比误差(APE)。75%测试案例的APE值为0.28%或更低。准确的机器学习模型可以帮助探索更小的参数空间,从而减少所需的时间和算力资源。

结论

使用Coventor SEMulator3D®在FinFET器件的栅极和源极/漏极之间引入虚拟空气间隙,我们研究了空气间隙对寄生电容的影响,并通过改变刻蚀工艺参数,研究了对空气间隙体积和寄生电容的影响。随后,结果被输入到人工神经网络中,以创建一个可以预测寄生电容的机器学习模型,从而减少为每个刻蚀参数值组合进行实验设计的需求。

审核编辑黄宇

-

半导体

+关注

关注

336文章

30043浏览量

258957 -

电容

+关注

关注

100文章

6443浏览量

158149 -

晶体管

+关注

关注

78文章

10286浏览量

146494

发布评论请先 登录

运放如何减少直流分量问题?

电源功率器件篇:线路寄生电感对开关器件的影响

KiCad-Parasitics:KiCad 寄生参数分析插件

逆变器寄生电容对永磁同步电机无传感器控制的影响

【干货分享】电源功率器件篇:变压器寄生电容对高压充电机输出功率影响

LCR测试仪中LP(Parallel)与LS(Series)模式的区别

麦科信光隔离探头在碳化硅(SiC)MOSFET动态测试中的应用

减少PCB寄生电容的方法

TRCX应用:显示面板工艺裕量分析

CAN通信节点多时,如何减少寄生电容和保障节点数量?

引入空气间隙以减少前道工序中的寄生电容

引入空气间隙以减少前道工序中的寄生电容

评论